tq2440开发板基本配置

- 时钟配置及分配

tq2440的晶振频率是12MHz,在uboot中有如下语句:

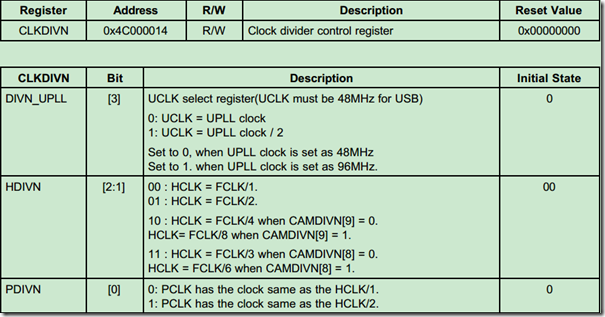

#define S3C2440_CLKDIV 0x05 /* FCLK:HCLK:PCLK = 1:4:8, UCLK = UPLL */ //HJ 100MHz

#define S3C2440_UPLL_48MHZ ((0x38<<12)|(0x02<<4)|(0x02)) //HJ 100MHz

/* Fin = 12.0000MHz */

#define S3C2440_MPLL_400MHZ ((0x5c<<12)|(0x01<<4)|(0x01)) //HJ 400MHz

void clock_init(void)

{

S3C24X0_CLOCK_POWER *clk_power = (S3C24X0_CLOCK_POWER *)0x4C000000;

/* FCLK:HCLK:PCLK = ?:?:? */

clk_power->CLKDIVN = S3C2440_CLKDIV; //HJ 1:4:8

/* change to asynchronous bus mod */

__asm__( "mrc p15, 0, r1, c1, c0, 0\n" /* read ctrl register */

"orr r1, r1, #0xc0000000\n" /* Asynchronous */

"mcr p15, 0, r1, c1, c0, 0\n" /* write ctrl register */

:::"r1"

);

/* to reduce PLL lock time, adjust the LOCKTIME register */

clk_power->LOCKTIME = 0xFFFFFF;

/* configure UPLL */

clk_power->UPLLCON = S3C2440_UPLL_48MHZ; //fin=12.000MHz

/* some delay between MPLL and UPLL */

delay (4000);

/* configure MPLL */

clk_power->MPLLCON = S3C2440_MPLL_400MHZ; //fin=12.000MHz

/* some delay between MPLL and UPLL */

delay (8000);

}

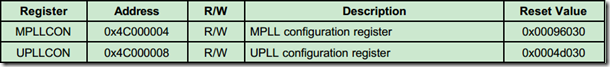

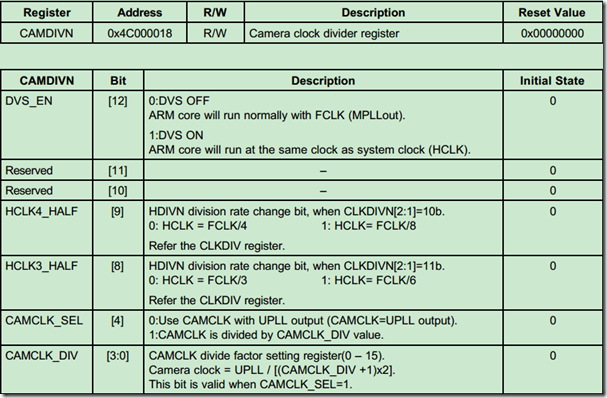

从上面的配置可以看到,与时钟相关的几个寄存器的配置值:

配置的值是:

MOLLCON = 0x5C011

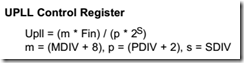

UPLLCON = 0x38022

其中,Mpll就是FCLK UPLL就是UCLK

配置的值是:0x05

该寄存器没有配置,所以是初始值,也就是全0。

综上,FCLK:HCLK:PCLK = 1 : 4 : 8

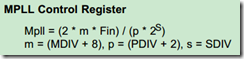

Mpll(FCLK) = (2 * (0x5c+8) * 12M)/((1+2) * 2) = (2*100*12M)/(6) = 400MHz

UPLL(UCLK) = ((0x38+8)*12M)/((2+2)*2^2) = (64*12M)/(16)=48MHz

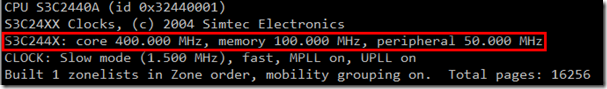

所以,FCLK=400MHz HCLK=100Hz PCLK=50MHz

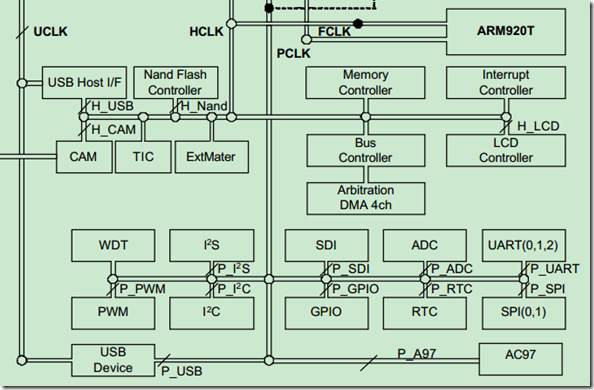

从上图可以看到系统中FCLK、HCLK、PCLK以及UCLK是如何分配给外设的。

其实也可以从系统的启动信息看出:

tq2440开发板基本配置的更多相关文章

- TQ2440开发板网络配置方式

一.命令行模式 1.设置IP.子网掩码(netmask) #ifconfig eth0 <IP地址> netmask <子网掩码> up up 表示开启网卡eth0,可以不加 ...

- 运行在TQ2440开发板上以及X86平台上的linux内核编译

一.运行在TQ2440开发板上的linux内核编译 1.获取源码并解压 直接使用天嵌移植好的“linux-2.6.30.4_20100531.tar.bz2”源码包. 解压(天嵌默认解压到/opt/E ...

- 基于TQ2440开发板的WiFi模块的使用经验总结

一.软.硬件资源准备: 内核版本:linux-2.6.30.4 交叉编译器版本:4.3.3 wpa_supplicant工具:wpa_supplicant-0.7.3.tar ; openssl-0. ...

- TQ2440开发板存储器

TX2440A与TQ2440A开发板使用核心板完全相同 有过51单片基础的同学应该都会看懂下图,先看下图,对实验板存储器分布有一个整体印象: s3c2440存储器概述: 1.S3C2440A的存储器管 ...

- TQ2440开发板挂载U盘出现乱码

解决方法:配置内核 make menuconfig File Systems ---> DOS/FAT/NT Filesystems ---> (utf8) D ...

- zynq开发板外设配置演示

有幸得到米尔电子zynq系列开发板Z-turn Board试用体验,下面说说我这款zynq系列的Z-TURN板子外设配置.从Z-turn Board原理图上看,目前可以配置的FPGA管脚大概有100多 ...

- 【转】深度分析NandFlash—物理结构及地址传送(以TQ2440开发板上的K9F2G08U0A为例)

K9F2G08U0A是三星公司生产的总容量为256M的NandFlash,常用于手持设备等消费电子产品.还是那句话,搞底层就得会看datasheet,我们就从它的datasheet看起. 这就是 K9 ...

- 在TQ2440开发板上ping 127.0.0.1不通

问题:在TQ2440上ping 127.0.0.1,提示错误 ping: sendto: Network is unreachable 解决方法:ifconfig lo 127.0.0.1 up ...

- uboot 2013.01 代码简析(1)开发板配置

u-boot下载地址:ftp://ftp.denx.de/pub/u-boot/u-boot-2013.01.01.tar.bz2 下载之后对该文件进行解压. 我试着分析smdk2410_config ...

随机推荐

- sudo 权限问题

窝里个去,不使用sudo吧rvm requirements执行不成功.加上sudo吧rvm requirements调用的brew install又不行.好吧,就按上面说的将brew转换到root模式 ...

- 主机找不到vmnet1和vmnet8

今天跑程序时,突然发现虚拟机ping不通主机了,返过来可行,防火墙什么的都设置好了,仍然不行,后来发现,在网络和共享中心已经看不到vmnet1和vmnet8了,更改适配器设置也只有本地连接和宽带连接, ...

- [转载]关于CSDN, cnblog, iteye和51cto四个博客网站的比较与分析

CSDN:http://blog.csdn.net/ cnblog: http://www.cnblogs.com/ iteye: http://www.iteye.com/blogs/ 51cto: ...

- 如何用 redis 造一把分布式锁

基本概念 锁 wiki:In computer science, a lock or mutex (from mutual exclusion) is a synchronization mechan ...

- Django Signals 从实践到源码分析(转)

原文:http://foofish.net/blog/66/django-signals 当某个事件发生的时候,signal(信号)允许senders(发送者)用来通知receivers(接收者),通 ...

- 实现系统函数time,获取当前时间与UTC的间隔

因种种原因,最近很少上cnblogs了.刚写了一个实现time的函数,可以通过该函数获取当前时间与1970年1月1日 0时0分0秒的差值,精确到秒,可以用在某些没有时候使用time不正确而不得不调用硬 ...

- HD4505小Q系列故事——电梯里的爱情

Problem Description 细心的同事发现,小Q最近喜欢乘电梯上上下下,究其原因,也许只有小Q自己知道:在电梯里经常可以遇到他心中的女神HR. 电梯其实是个很暧昧的地方,只有在电梯里,小Q ...

- CodeForces 534C Polycarpus' Dice (数学)

题意:第一行给两个数,n 和 A,n 表示有n 个骰子,A表示 n 个骰子掷出的数的和.第二行给出n个数,表示第n个骰子所能掷出的最大的数,这些骰子都有问题, 可能或多或少的掷不出几个数,输出n个骰子 ...

- CStdioFile

CStdioFile类的声明保存再afx.h头文件中. CStdioFile类继承自CFile类,CStdioFile对象表示一个用运行时的函数fopen打开的c运行时的流式文件.流式文件是被缓冲的, ...

- 修改Android 程序的icon快捷方式图标和名称

在res/drawable-hdpi或res/drawable-ldpi或res/drawable-mdpi目录下,加下你要显示的图片,最好后缀是为.png的,然后修改AndroidManifest. ...