Testbench文件编写纪要(Verilog)

之前在使用Verilog做FPGA项目中、以及其他一些不同的场合下,零散的写过一些练手性质的testbench文件,开始几次写的时候,每次都会因为一些基本的东西没记住、写的很不熟练,后面写的时候稍微熟练了一点、但是整体编写下来比较零碎不成体系,所以在这里简要记录一下一般情况下、针对小型的verilog模块进行测试时所需要使用到的testbench文件的编写要点。

本文主要参考了在网上找到的Lattice公司的“A Verilog HDL Test Bench Primer”手册中的有关内容。谢谢!

模块实例化、reg&wire声明、initial和always块的使用

需要测试的模块(Verilog-module)被称为DUT(Design Under Test),在testbench中需要对一个或者多个DUT进行实例化。

Testbench中的顶层module不需要定义输入和输出。

Testbench中连接到DUT instance的输入的为reg类型、连接到DUT instance的输出的为wire类型。

对于DUT的inout类型变量,在testbench中需要分别使用reg、wire类型的变量进行调用。

例如,对于下面这样一个待测试module:

module bidir_infer (DATA, READ_WRITE);

input READ_WRITE ;

inout [:] DATA ;

reg [:] LATCH_OUT ; always @ (READ_WRITE or DATA) begin

if (READ_WRITE == )

LATCH_OUT <= DATA;

end assign DATA = (READ_WRITE == ) ? 'bZ : LATCH_OUT; endmodule

为其设计的testbench文件可以是:

module test_bidir_ver;

reg read_writet;

reg [:] data_in;

wire [:] datat, data_out;

bidir_infer uut (datat, read_writet); assign datat = (read_writet == ) ? data_in : 'bZ;

assign data_out = (read_writet == ) ? datat : 'bZ; initial begin

read_writet = ;

data_in = ;

# read_writet = ;

end endmodule

和普通的Verilog模块中一样、使用assign对wire类型的变量进行赋值。

需要留意的一点是:对于没有在代码中赋初始值的变量,wire类型变量被初始化为Z、reg类型变量被初始化为X。

always和initial是两种对reg变量进行操作的串行控制块。每个initial和always块都会在仿真开始时同时开始运行。

常见的,可以利用它们生成模块所需的时钟和复位信号,如下:

‘timescale ns / ps reg clk_50, rst_l; initial

begin

$display($time, " << Starting the Simulation >>");

clk_50 = ’b0; // at time 0

rst_l = ; // reset is active

# rst_l = ’b1; // at time 20 release reset

end always

# clk_50 = ~clk_50; // every ten nanoseconds invert

首行定义了时间单位/时间精度。时间单位为1ns,这样生成的clk_50时钟周期就是20ns、也就是频率为50MHz。

复位信号rst_l在初始为0复位态、在20ns之后为1解除复位。

仿真中的停止、变量监视和输出

有两种仿真控制函数:$finish和$stop。其中,$finish任务用于终止仿真并跳出仿真器;$stop任务则用于中止仿真。在Modelsim中,$stop任务则是返回到交互模式。

如果需要监视仿真中某个变量的变化情况,可以使用$monitor函数:

$monitor($time, " clk_50=%b, rst_l=%b, enable_l=%b, load_l=%b, count_in=%h, cnt_out=%h, oe_l=%b, count_tri=%h", clk_50, rst_l, enable_l, load_l, count_in, cnt_out, oe_l, count_tri);

每当变量列表中的任一变量发生变化,就会产生输出。

如果需要在仿真控制台屏幕打印输出,可以使用$display函数:

$display($time, "<< count = %d - Turning OFF count enable >>",cnt_out);

任务Task的用法

可以将一组重复性的或者相关的命令组合到一起构成一个任务。

任务通常可以在initial或者always块中被调用。

一个任务可以拥有输入、输出、以及inouts,也可以包含计时或延时元素。

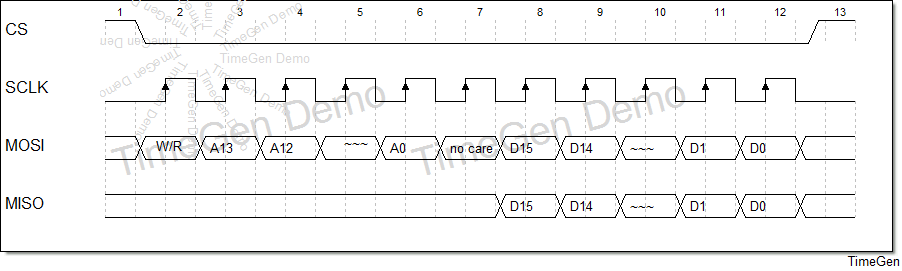

以一个在FPGA上实现的简单SPI接口为例。外部设备为主、FPGA为从,命令一共32bit,构成为“1位读写命令字(1读0写)+14位地址+1位NO CARE+16位数据”,片选信号拉低之后通信开始,时序如下图:

数据流由外设到FPGA时(FPGA为接收),外设在SCLK的下降沿更新MOSI;FPGA在SCLK的上升沿将MOSI上的值抓取到移位寄存器。

当FPGA为发送方时,FPGA在SCLK的下降沿更新MISO线上的输出,外设在SCLK的上升沿将MISO上的值抓取过来。

外设可以通过该SPI接口访问FPGA内部生成的寄存器。

当对FPGA上的spi模块进行读测试时,外设发给FPGA的读指令为:

{1'b1,address,1'b0,data(读取到的16bit数据)}

为此编写的任务spi_read可以是:

task spi_read;

input[:] address;

output[:] data;

reg [:] output_register;

reg [:]input_register;

integer i;

begin

$display("time:%t----------------task spi_read",$time );

#;

spi_clk = 'b0;

spi_csn = 'b1;

spi_mosi ='b0;

output_register = {'b1,address,1'b0,'d0}; $display("time:%t,testbench read output_register: %h,",$time,output_register );

$display("time:%t,testbench read address: %h",$time,address ); spi_csn = 'b1;

for(i = ; i < ; i=i+)

begin

spi_csn = 'b0;

spi_clk = 'b0;

spi_mosi = output_register[-i];

#;

spi_clk = 'b1;

#;

end for(i = ; i < ; i=i+)

begin

spi_csn = 'b0;

spi_clk = 'b0;

#;

spi_clk = 'b1;

input_register[-i] = spi_miso;

#;

end

spi_csn = 'b1; data = input_register;

$display("time:%t,testbench spi_read read data: %h,",$time,input_register ); $display("time:%t----------------",$time );

#;

end endtask

(其中仿真的时间单位为1ns,spi时钟频率为10MHz)

示例及汇总

根据前述内容,自我总结一般简单的testbench文件的结构形式可以是如下:

`timescale ns / ns module testbench_module_top;

reg

reg

……

wire

wire

…… //reset and clock definition

initial begin …end

initial begin …end //actual testing flows

initial

begin

//variables initialization

a =

b =

… task_1(var_1… var_N)

…

task_N(var_1… var_N)

$stop;

…end //dut module instance

module_top U1

(

.var1(),

.var2(),

…

.varN()

) //necessary control logic for testbench module test flow

always@(...) //tasks definition

task task_1;

input …;

output …;

……

//action flow

……

endtask …… task task_N;

……

endtask endmodule

Testbench文件编写纪要(Verilog)的更多相关文章

- 转:SYNOPSYS VCS Makefile文件编写与研究

SYNOPSYS VCS Makefile文件编写与研究 这个Makefile是synopsys提供的模板,看上去非常好用,你只要按部就班提供实际项目的参数就可以了.我们来看这个文件的头部说明:mak ...

- Testbench的编写

Testbench的作用,在于给我们编写的可综合代码的模块送入激励.即在我们波形仿真中用编写testbench来代替拖拽波形.其中还包括了我们硬件仿真与matlab仿真的联调建立(将matlab产生的 ...

- 网站 robots.txt 文件编写

网站 robots.txt 文件编写 Intro robots.txt 是网站根目录下的一个纯文本文件,在这个文件中网站管理者可以声明该网站中不想被robots访问的部分,或者指定搜索引擎只收录指定的 ...

- 【OpenWRT】【RT5350】【三】MakeFile文件编写规则和OpenWRT驱动开发步骤

一.Makefile文件编写 http://www.cnblogs.com/majiangjiang/articles/3218002.html 可以看下上面的博客,总结的比较全了,在此不再复述 二. ...

- linux库文件编写入门(笔记)

linux库文件的编写 作者: laomai地址: http://blog.csdn.net/laomai 本文主要参考了如下资料⑴hcj写的"Linux静态/动态链接库的创建和使用&quo ...

- Linux Makefile文件编写详细步骤与实践

Linux Makefile文件编写详细步骤与实践 1.makefile概述 Windows环境下IDE会帮你完成makefile文件的编写,但在UNIX环境下你就必须自己写makefile了,会不会 ...

- Pdf File Writer 中文应用(PDF文件编写器C#类库)

该文由小居工作室(QQ:2482052910) 翻译并提供解答支持,原文地址:Pdf File Writer 中文应用(PDF文件编写器C#类库):http://www.cnblogs.com/ ...

- 一个简单的makefile文件编写

下午闲来无聊,就打开很久没动过的linux系统想熟悉熟悉在linux上面编译代码,结果一个makefile文件搞到晚上才搞定,哈哈! 先把代码简单贴上来,就写了一个冒泡排序: sort.h: #ifn ...

- C++ Makefile文件编写

对现有的一个C++动态库文件和调用程序,分别编写Makefile文件,从零开始,这里把自己弄明白的一些东西分享给大家. 1.必须明确Linux下,C++的编译器是g++,C语言的是gcc.网上大多数又 ...

随机推荐

- B - Oulipo

The French author Georges Perec (1936�C1982) once wrote a book, La disparition, without the letter ' ...

- 洛谷—— P2015 二叉苹果树

https://www.luogu.org/problem/show?pid=2015 题目描述 有一棵苹果树,如果树枝有分叉,一定是分2叉(就是说没有只有1个儿子的结点) 这棵树共有N个结点(叶子点 ...

- TCP学习(3)--TCP释放连接的过程(四次挥手)

一.TCP释放连接的过程(四次挥手) TCP释放连接的步骤例如以下图所看到的. 如今如果clientA和server端B都处于数据传送状态. TCP连接断开的过程例如以下: 1.clien ...

- NGINX Web Server Nginx web server

原文地址:http://nginx.com/resources/admin-guide/web-server/ NGINX Web Server Nginx web server This secti ...

- POJ2777 Count Color 线段树区间更新

题目描写叙述: 长度为L个单位的画板,有T种不同的颜料.现要求按序做O个操作,操作分两种: 1."C A B C",即将A到B之间的区域涂上颜色C 2."P A B&qu ...

- FZU 1894 志愿者选拔【单调队列】【monotone decreasing queue】

Problem 1894 志愿者选拔 Accept: 1770 Submit: 5523 Time Limit: 1500 mSec Memory Limit : 32768 KB P ...

- LeetCode 234 Palindrome Linked List(回文链表)(*)(?)

翻译 给定一个单链表,确定它是否是回文的. 跟进: 你能够在O(n)时间和O(1)空间下完毕它吗? 原文 Given a singly linked list, determine if it is ...

- C++ 句柄类的原理以及设计

句柄类存在的意义是为了弥补将派生类对象赋给基类对象时发生的切片效应.比如以下的程序: multimap<Base> basket; Base base; Derived derive; b ...

- mongodb数据库的启动和停止

数据库的启动和停止是数据库最主要的操作,也是数据库可以提供服务和被连接管理的前提条件.不同的数据库启动和停止的方式有一些差异.但也有同样之处,启动和关闭也必然会和数据库的进程有关 ...

- Swift版本UIWebView长按保存图片

起因 最近需要做个IOS的壳子,用到长按保存图片的功能,发现百度出来的全是OC语法的例子,很多都不是全面,只能自己写一份Swift版本的,图片下面附上Github地址 效果图 Github地址:htt ...