DC逻辑综合工具简介-Design Compiler

逻辑综合简介

- 逻辑综合:代码转变为网表

- FPGA:代码转变为FPGA内部的数字单元

- 在进行综合的时候往往会使用一些脚本工具

- 需要学会看综合之后的报告

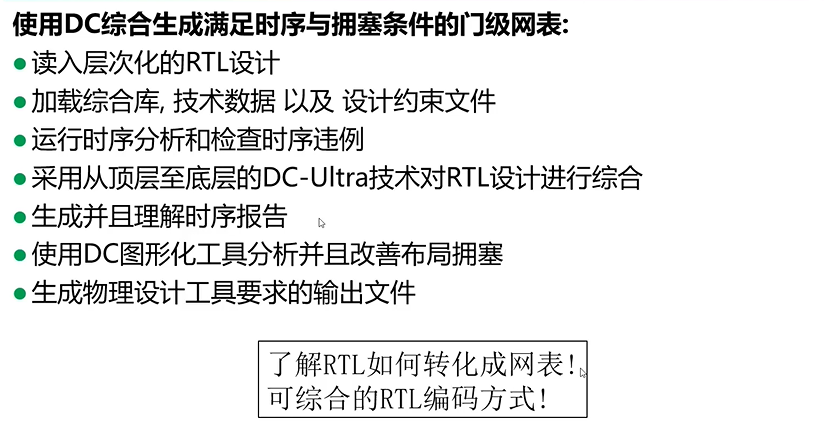

1.目标

- 进行综合需要读入RTL设计,还需要用到fab提供的工艺库(综合库)

- RTL -- 书写完成后,输入到DC,复杂的RTL设计,通常是层次化设计

- 综合库 -- 使用的工艺库,比如台积电5nm工艺,设计约束和技术文件

- 设计约束 - 时钟频率等

- RTL写完之后,就要解决掉RTL中的语法错误

- 了解命令,掌握分析报告的方法

2.必备知识

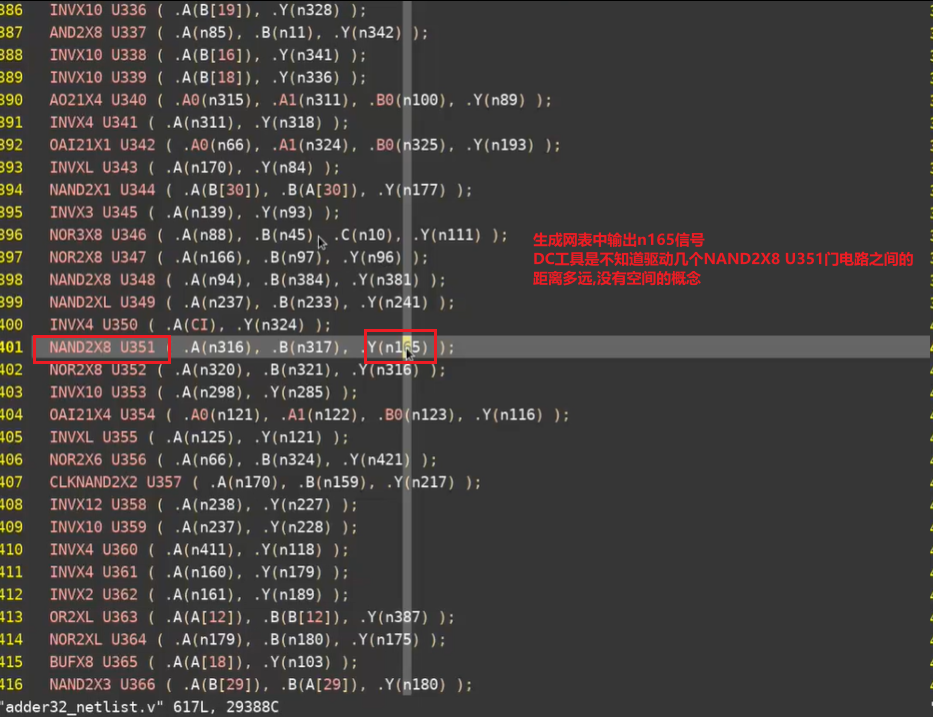

门级 -- 将RTL转变为门级电路(或门\寄存器\与门\与非门)实现的网表

clock skew - 时钟到达不同寄存器的时间不同,需要插入buffer使得时钟到达不同寄存器的时间相同

综合是什么?

- idea -- 需求 -- 架构 -- 微架构设计 -- RTL -- Netlist -- 版图 -- Fab -- 芯片 -- 封装测试 -- 集成到PCB上

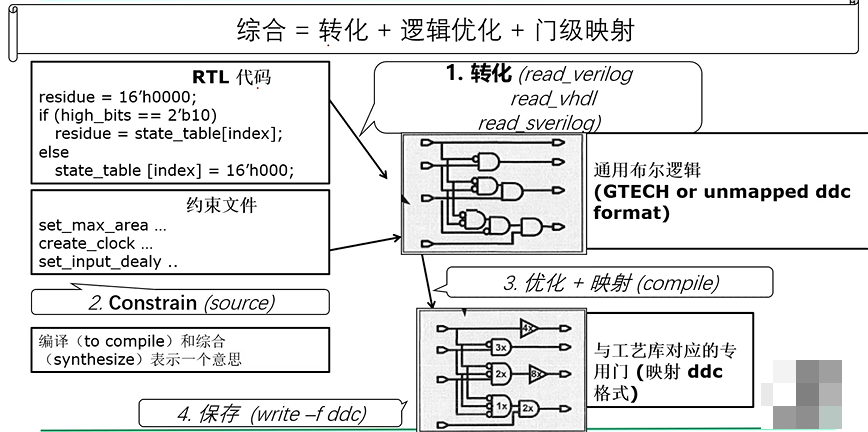

2.1 综合逻辑

- 第一遍综合的时候,输入的是RTL代码和一些约束,没有物理信息,综合结果可能不是很理想

- 往往在第一遍综合之后还可能进行第二遍综合

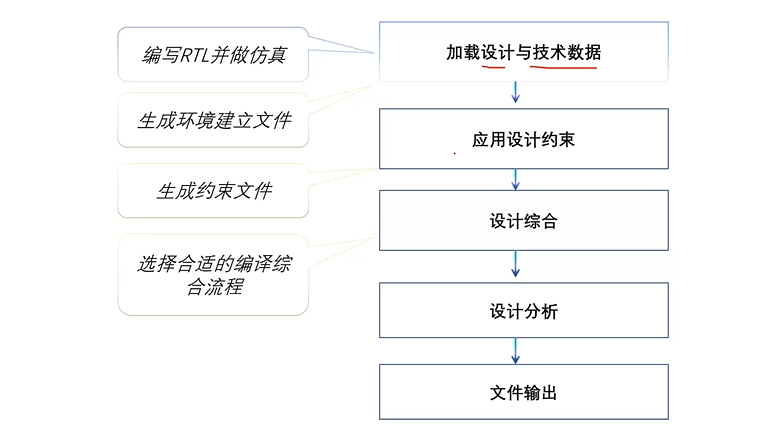

2.2 综合流程

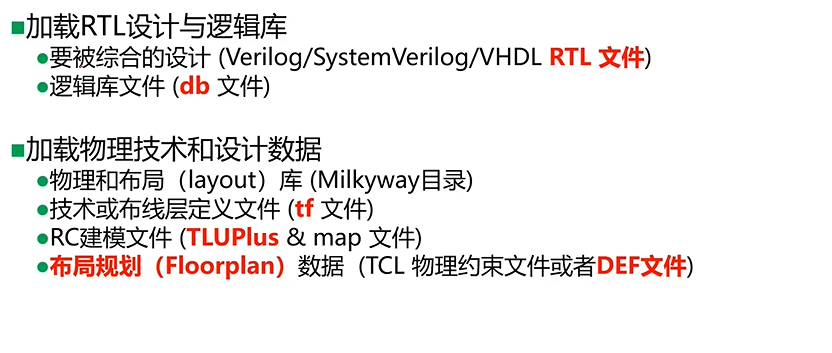

- 读入RTL+工艺库

- 添加约束

- 进行综合

- 转化:先将RTL代码转变为一种GTECH格式的通用网表(使用的门电路和使用的具体工艺库是不对应的)

- 门级映射(GTECH) - 将GTECH中的网表映射成特定工艺库中的专用门电路,根据驱动能力选择门器件的大小

- 优化逻辑 - 哪些门可以合并或者取消

3.综合示例

3.1 RTL

module (

input wire [31:0] a_in,

input wire [31:0] b_in,

input wire [0:0] c_in,

output wire [31:0] sum_out,

output wire [0:0] c_out

);

assign {c_out,sum_out} = a_in + b_in + c_in;

endmodule

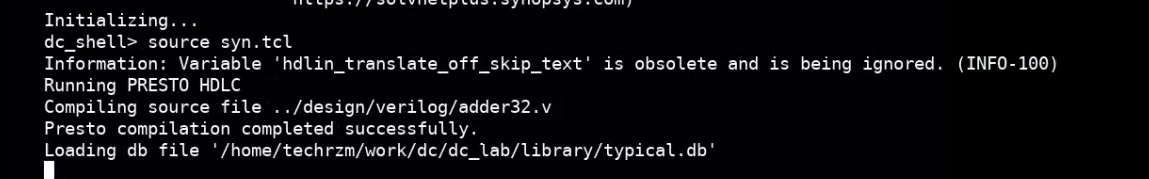

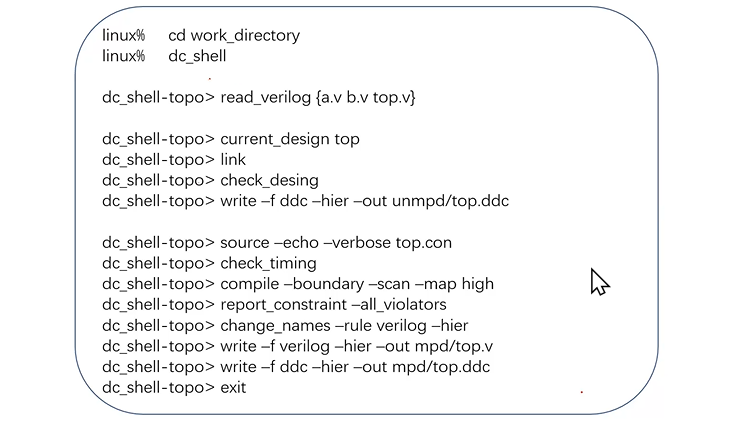

3.2 综合过程

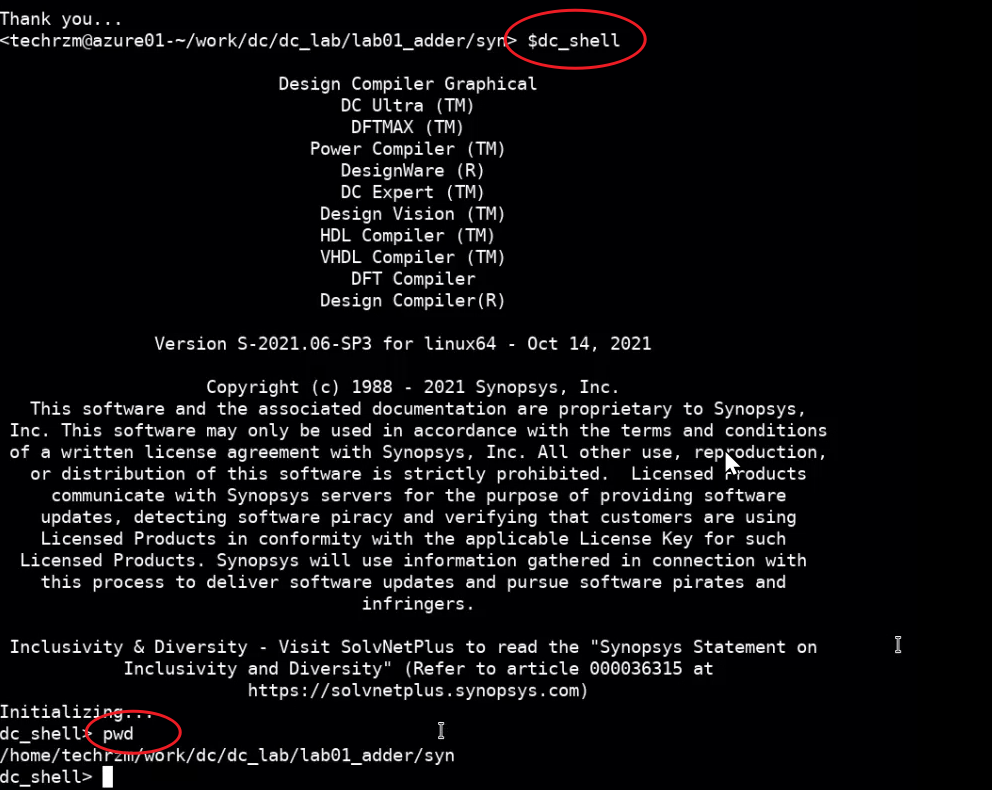

- 在命令行中输入dc_shell

dc_shell

- 一般使用脚本的形式

2.source 综合文件

source syn.tcl

3.产生结果

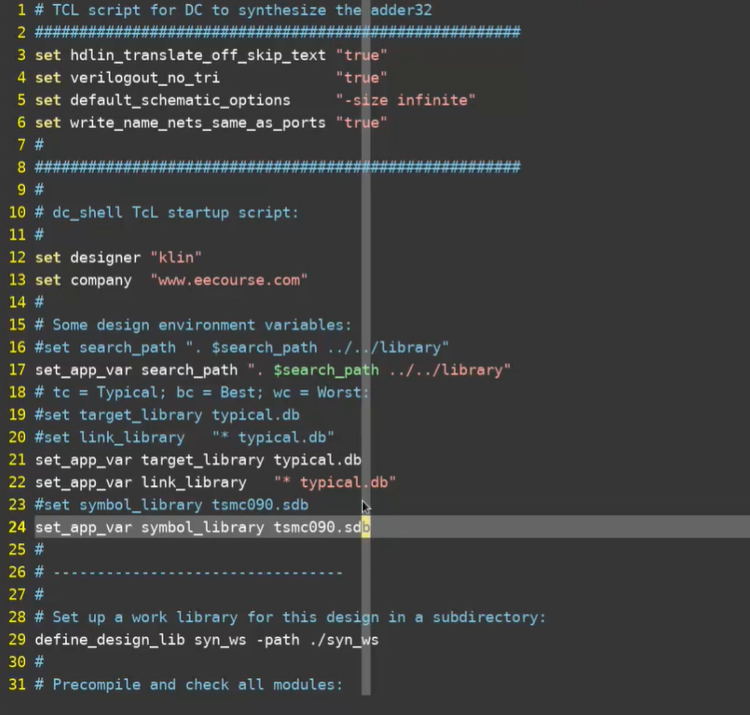

3.3 syn.tcl脚本内容

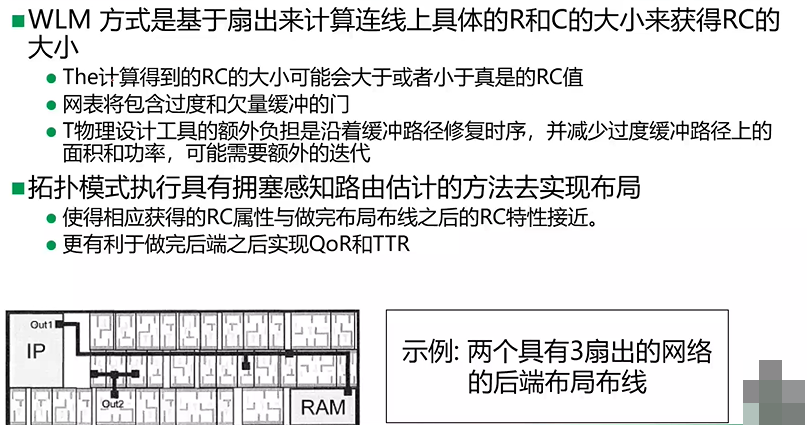

4.两种计算互连产生的RC系数的方式

- WLM根据扇出的数量估算门电路和门电路之间的线路长度,以此来推断RC的大小,是一种概率学上的统计结果

- 优点:方便计算

- 缺点:计算RC > 实际RC,会有一些冗余设计,浪费一些面积;计算RC < 实际RC,网表包含欠量的缓冲门

- 会对RC的结果进行迭代,就是多计算几次

- 寄存器之间的延迟:standcell的延时和一些连线,对于standcell的延时,是准确的,唯一不准确的连线的延时往往是不准的,在综合的时候往往需要迭代

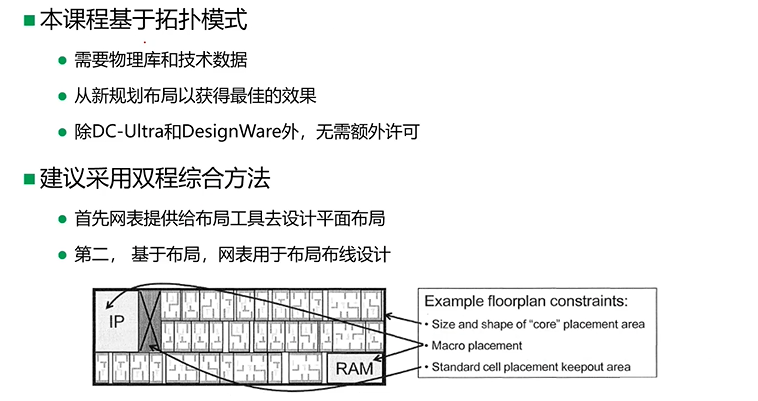

- 采用拓扑的方式计算RC,拓扑模式需要读取RTL之外还需要读入物理信息 ,有物理信息支持之后,计算的RC结果往往是准确的,可以针对性的对一些路径进行优化

- QOR -- quality of result

- TTR -- Time to Result

- 拓扑模式:需要布局布线之后的物理信息

- 在企业中往往使用双程的综合方法,首先使用WLM方式进行一遍逻辑综合,后端使用WLM的结果进行一遍布局布线,将布局布线后的物理信息传递给DC,再次进行拓扑模式下的综合

4.1 双程综合方法

- 首次综合,可以添加一些约束

- ICC -- 进行布局布线,产生DEF文件,其中包含了一些物理信息

- 拓扑模式下的综合:DCT,产生一个网表

- ICC -- 再次进行布局布线

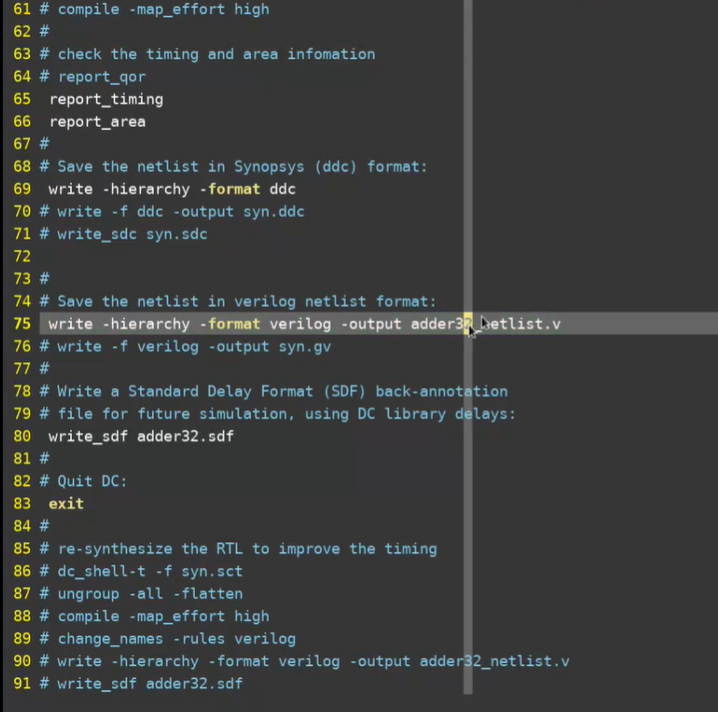

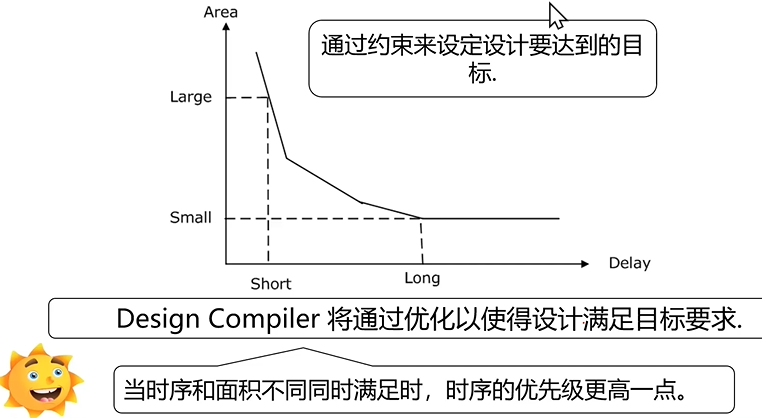

5.约束驱动综合

- 频率约束,面积约束

- DC优先满足时钟频率,在保证时钟的情况下,优化面积

- delay小,performace好,面积大;delay大,performance差,面积小;

- power/performance/area -- 三者是相互约束的

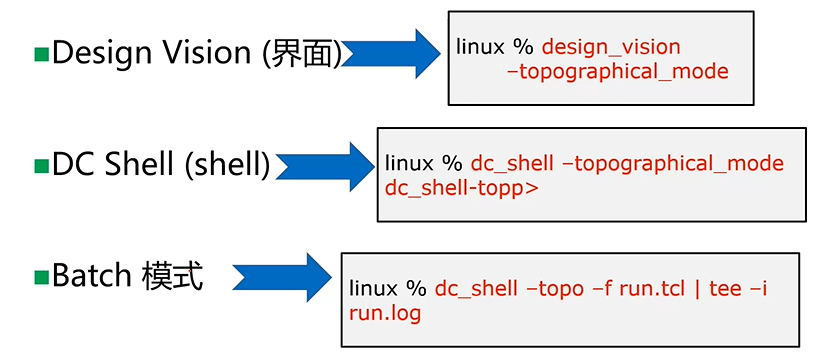

6.综合工具的启动方式

1.在命令行输入design_vision,可以打开图形化界面,查看物理信息的时候使用图形化界面

design_vision

2.dc_shell,使用的是WLM license,交互模式

# 使用WLM模式

dc_shell

# 使用拓扑模式

dc_shell -topo

- 使用bash模式,长用于使用稳定脚本,查看报告,在公司中经常使用bash模式

dc_shell -f syn.tcl | tee -i run.log

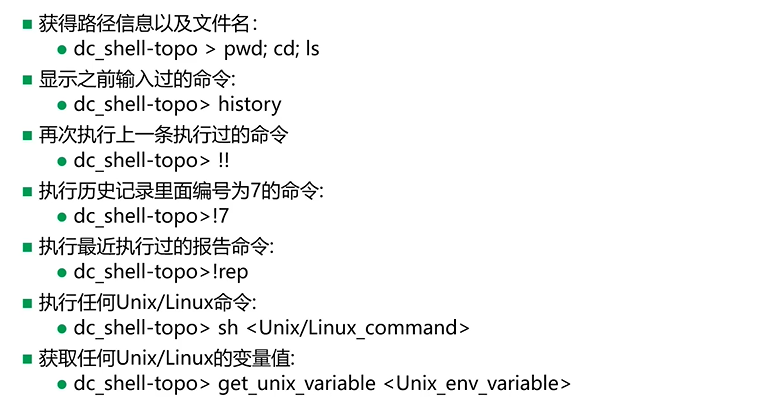

7.Unix\Linux系统DC-Shell命令

dc_shell

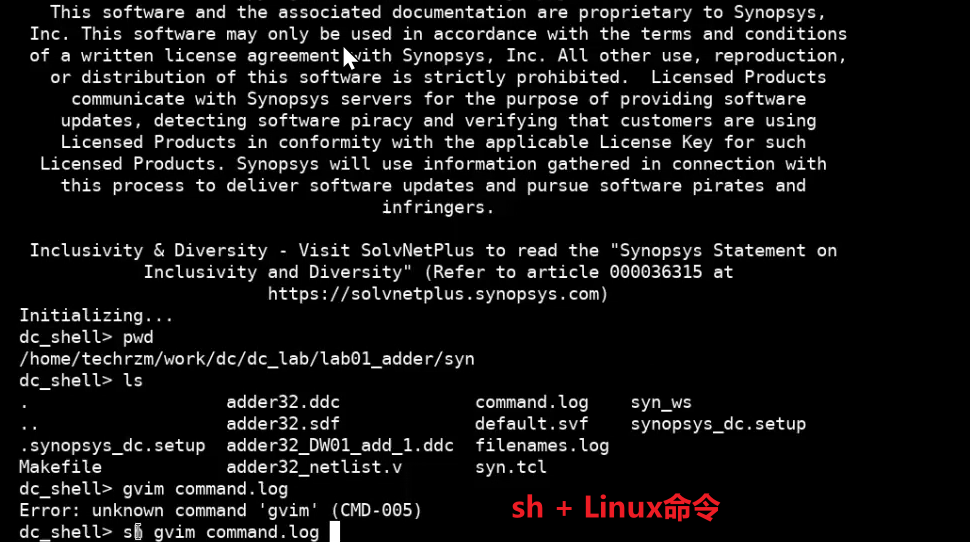

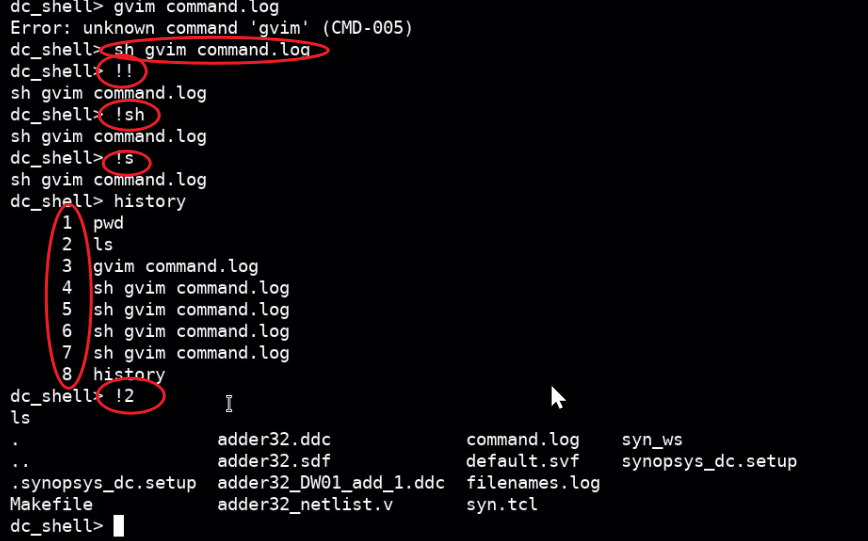

- dc_shell 中执行linux命令,前面加sh

- 执行上一步操作

1.上下箭头可以选择命令

2.!!--执行上一步操作

3.!+上一步开头的命令

sh gvim test.v

!sh -- 可以执行上述命令

!s -- 也可以执行上一步命令

4.history -- 查看历史命令,通过!+数字选择执行第几条命令

- .ddc文件包含网表和约束sdc文件,拿到.ddc文件可以认为是进行了综合

8.DC工具掌握

8.1 综合主要步骤

- .db文件 -- 逻辑综合库

8.2 DC主要流程

8.3 DC命令总览

- current_design top 设置顶层为综合对象

- link -- 将RTL层级理顺

- check_design -- 检查RTL代码

DC逻辑综合工具简介-Design Compiler的更多相关文章

- (转)Synopsys工具简介

DC Ultra--Design Compiler的最高版本 在Synopsys软件中完整的综合方案的核心是DC UltraTM,对所有设计而言它也是最好级别的综合平台.DC Ultra添加了全面的数 ...

- Tcl与Design Compiler (八)——DC的逻辑综合与优化

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 对进行时序路径.工作环 ...

- 03-逻辑综合工具 - Design Compiler

逻辑综合工具DC IC设计流程,市场-->制定spec-->RTL(同时进行sim,通过alint检查RTL有没有错误)-->systhesis(逻辑综合)-->PR(STA) ...

- Tcl与Design Compiler (二)——DC综合与Tcl语法结构概述

1.逻辑综合的概述 synthesis = translation + logic optimization + gate mapping . DC工作流程主要分为这三步 Translation : ...

- Tcl与Design Compiler (五)——综合库(时序库)和DC的设计对象

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 前面一直说到综合库/工艺库这些东西,现在就来讲讲讲 ...

- Tcl与Design Compiler (七)——环境、设计规则和面积约束

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 本文的主要内容是讲解( ...

- Tcl与Design Compiler (十二)——综合后处理

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 概述 前面也讲了一些综合后的需要进行的一些工作,这 ...

- Design Compiler 综合

综合(synthesis) = 转换(translation) + 优化(logic optimization) + 映射(gate mapping): 转换阶段将HDL语言描述的电路用门级逻辑实现. ...

- Tcl与Design Compiler (十一)——其他的时序约束选项(二)

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 前面介绍的设计都不算很复杂,都是使用时钟的默认行为 ...

- Tcl与Design Compiler (十三)——Design Compliler中常用到的命令(示例)总结

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 本文将描述在Design Compliler中常用 ...

随机推荐

- TiDB故障处理之让人迷惑的Region is Unavailable

背景 最近某集群扩容了一批物理机,其中 TiKV 节点有6台机器12个实例,同时调整了 label 设置增加了一层机柜级容灾.因为前期做了比较充分的准备工作,到了变更窗口只等着执行scale-out就 ...

- 笔记本安装linux

下载 桌面版 Ubuntu 镜像 服务器版 Ubuntu 镜像 使用 Balena Etcher 制作系统安装盘 (1)官方网站下载: 点我下载 (2)下载完毕软件之后,打开软件,选择我们下载好的系统 ...

- 在k8s中快速搭建基于Prometheus监控系统

公众号「架构成长指南」,专注于生产实践.云原生.分布式系统.大数据技术分享 前言 K8s本身不包含内置的监控工具,所以市场上有不少这样监控工具来填补这一空白,但是没有一个监控工具有prometheus ...

- ElasticSearch之虚拟内存

查看当前Linux系统中vm.max_map_count变量的值,命令如下: sysctl vm.max_map_count 执行结果的样例,如下: vm.max_map_count = 65530 ...

- 在ASP.NET Core微服务架构下使用RabbitMQ如何实现CQRS模式

前言 在现代软件开发中,微服务架构和CQRS模式都是备受关注的技术趋势.微服务架构通过将应用程序拆分为一系列小型.自治的服务,提供了更好的可伸缩性和灵活性.而CQRS模式则通过将读操作和写操作分离,优 ...

- 开发篇1:使用原生api和Langchain调用大模型

对大模型的调用通常有以下几种方式:方式一.大模型厂商都会定义http风格的请求接口,在代码中可以直接发起http请求调用:方式二.在开发环境中使用大模型厂商提供的api:方式三.使用开发框架Langc ...

- Programming Abstractions in C阅读笔记:p197-p201

<Programming Abstractions in C>学习第64天,p196-p201总结. 一.技术总结 很难,唯有继续往下看才能让其变容易. 二.英语总结 1.psycholo ...

- 痞子衡嵌入式:原来i.MXRT1170内部RAM的ECC初始化工作可全部由ROM完成

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家分享的是i.MXRT1170内部RAM的ECC初始化工作可全部由ROM完成. 痞子衡之前写了三篇文章 <M7 FlexRAM ECC> ...

- 使用 Python 将数据写入 Excel 工作表

在数据处理和报告生成等工作中,Excel 表格是一种常见且广泛使用的工具.然而,手动将大量数据输入到 Excel 表格中既费时又容易出错.为了提高效率并减少错误,使用 Python 编程语言来自动化数 ...

- 华为云HBase冷热分离最佳实践

本文分享自华为云社区<华为云HBase 冷热分离最佳实践>,作者:pippo. HBase介绍 HBase是Hadoop Database的简称,是建立在Hadoop文件系统之上的分布式面 ...