RAM-Based Shift Register (ALTSHIFT_TAPS) IP Core-实现3X3像素阵列存储

最近想要实现CNN的FPGA加速处理,首先明确在CNN计算的过程中,因为卷积运算是最耗时间的,因此只要将卷积运算在FPGA上并行实现,即可完成部分运算的加速

那么对于卷积的FPGA实现首先要考虑的是卷积子模板具体如何实现,我们在matlab或者c实现比如3X3的子模板的时候,只要用一个数组即可将模板的数据存储起来,而在FPGA的话有以下三种方法:

- 用2个或3个RAM存储3X3像素阵列

- 用2个或3个FIFO存储3X3像素阵列

- 用shift_RAM移位存储3X3像素阵列

而shift_RAM好像就是为了阵列的实现量身定做的一般。

shift_RAM的配置参数主要有以下几个:

手册中可以参考理解的一个非常形象的图如下:

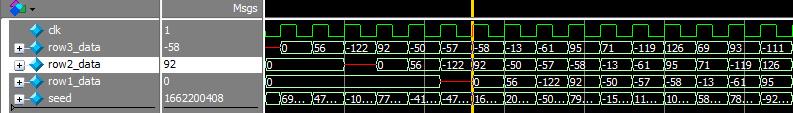

进一步的进行单独一个IP核的仿真后得到:

其中上述参数设置分别为8,2,3,上述仿真图中,相当于把一个矩阵A通过移位寄存的方法通过row3_data送入到RAM,然后分三行输出,在游标所示处就可以开始输出3X3矩阵

0,56,-122

92,50,-57

-58,-13,-61

以下部分是加入了对视频信号处理控制后的代码实现过程:

/*----------------------------------------------------------------------- CONFIDENTIAL IN CONFIDENCE

This confidential and proprietary software may be only used as authorized

by a licensing agreement from CrazyBingo (Thereturnofbingo).

In the event of publication, the following notice is applicable:

Copyright (C) 2011-20xx CrazyBingo Corporation

The entire notice above must be reproduced on all authorized copies.

Author : CrazyBingo

Technology blogs : http://blog.chinaaet.com/crazybingo

Email Address : thereturnofbingo@gmail.com

Filename : VIP_Matrix_Generate_3X3_8Bit.v

Data : 2014-03-19

Description : Generate 8Bit 3X3 Matrix for Video Image Processor.

Give up the 1th and 2th row edge data caculate for simple process

Give up the 1th and 2th point of 1 line for simple process

Modification History :

Data By Version Change Description

=========================================================================

13/05/26 CrazyBingo 1.0 Original

14/03/16 CrazyBingo 2.0 Modification

-*/ `timescale 1ns/1ns

module VIP_Matrix_Generate_3X3_8Bit

#(

parameter [:] IMG_HDISP = 'd640, //640*480

parameter [:] IMG_VDISP = 'd480

)

(

//global clock

input clk, //cmos video pixel clock

input rst_n, //global reset //Image data prepred to be processd

input per_frame_vsync, //Prepared Image data vsync valid signal

input per_frame_href, //Prepared Image data href vaild signal

input per_frame_clken, //Prepared Image data output/capture enable clock

input [:] per_img_Y, //Prepared Image brightness input //Image data has been processd

output matrix_frame_vsync, //Prepared Image data vsync valid signal

output matrix_frame_href, //Prepared Image data href vaild signal

output matrix_frame_clken, //Prepared Image data output/capture enable clock

output reg [:] matrix_p11, matrix_p12, matrix_p13, //3X3 Matrix output

output reg [:] matrix_p21, matrix_p22, matrix_p23,

output reg [:] matrix_p31, matrix_p32, matrix_p33

); //Generate 3*3 matrix

//--------------------------------------------------------------------------

//--------------------------------------------------------------------------

//--------------------------------------------------------------------------

//sync row3_data with per_frame_clken & row1_data & raw2_data

wire [:] row1_data; //frame data of the 1th row

wire [:] row2_data; //frame data of the 2th row

reg [:] row3_data; //frame data of the 3th row

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

row3_data <= ;

else

begin

if(per_frame_clken)

row3_data <= per_img_Y;

else

row3_data <= row3_data;

end

end //---------------------------------------

//module of shift ram for raw data

wire shift_clk_en = per_frame_clken;

Line_Shift_RAM_8Bit

#(

.RAM_Length (IMG_HDISP)

)

u_Line_Shift_RAM_8Bit

(

.clock (clk),

.clken (shift_clk_en), //pixel enable clock

// .aclr (1'b0), .shiftin (row3_data), //Current data input

.taps0x (row2_data), //Last row data

.taps1x (row1_data), //Up a row data

.shiftout ()

); //------------------------------------------

//lag 2 clocks signal sync 因为数据存储耗费了一个时钟,因此3*3阵列读取使能和时钟要偏移一个时钟

reg [:] per_frame_vsync_r;

reg [:] per_frame_href_r;

reg [:] per_frame_clken_r;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

per_frame_vsync_r <= ;

per_frame_href_r <= ;

per_frame_clken_r <= ;

end

else

begin

per_frame_vsync_r <= {per_frame_vsync_r[], per_frame_vsync};

per_frame_href_r <= {per_frame_href_r[], per_frame_href};

per_frame_clken_r <= {per_frame_clken_r[], per_frame_clken};

end

end

//Give up the 1th and 2th row edge data caculate for simple process

//Give up the 1th and 2th point of 1 line for simple process

wire read_frame_href = per_frame_href_r[]; //RAM read href sync signal

wire read_frame_clken = per_frame_clken_r[]; //RAM read enable

//将存储RAM以及阵列生成两个步骤需要的时钟都去掉

assign matrix_frame_vsync = per_frame_vsync_r[];

assign matrix_frame_href = per_frame_href_r[];

assign matrix_frame_clken = per_frame_clken_r[]; //----------------------------------------------------------------------------

//----------------------------------------------------------------------------

/******************************************************************************

---------- Convert Matrix ----------

[ P31 -> P32 -> P33 -> ] ---> [ P11 P12 P13 ]

[ P21 -> P22 -> P23 -> ] ---> [ P21 P22 P23 ]

[ P11 -> P12 -> P11 -> ] ---> [ P31 P32 P33 ]

******************************************************************************/

//---------------------------------------------------------------------------

//---------------------------------------------------

/***********************************************

(1) Read data from Shift_RAM

(2) Caculate the Sobel

(3) Steady data after Sobel generate

************************************************/

//wire [23:0] matrix_row1 = {matrix_p11, matrix_p12, matrix_p13}; //Just for test

//wire [23:0] matrix_row2 = {matrix_p21, matrix_p22, matrix_p23};

//wire [23:0] matrix_row3 = {matrix_p31, matrix_p32, matrix_p33};

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

{matrix_p11, matrix_p12, matrix_p13} <= 'h0;

{matrix_p21, matrix_p22, matrix_p23} <= 'h0;

{matrix_p31, matrix_p32, matrix_p33} <= 'h0;

end

else if(read_frame_href)

begin

if(read_frame_clken) //Shift_RAM data read clock enable

begin

{matrix_p11, matrix_p12, matrix_p13} <= {matrix_p12, matrix_p13, row1_data}; //1th shift input

{matrix_p21, matrix_p22, matrix_p23} <= {matrix_p22, matrix_p23, row2_data}; //2th shift input

{matrix_p31, matrix_p32, matrix_p33} <= {matrix_p32, matrix_p33, row3_data}; //3th shift input

end

else

begin

{matrix_p11, matrix_p12, matrix_p13} <= {matrix_p11, matrix_p12, matrix_p13};

{matrix_p21, matrix_p22, matrix_p23} <= {matrix_p21, matrix_p22, matrix_p23};

{matrix_p31, matrix_p32, matrix_p33} <= {matrix_p31, matrix_p32, matrix_p33};

end

end

else

begin

{matrix_p11, matrix_p12, matrix_p13} <= 'h0;

{matrix_p21, matrix_p22, matrix_p23} <= 'h0;

{matrix_p31, matrix_p32, matrix_p33} <= 'h0;

end

end endmodule

//注意这里得到的每一行得第一第二的像素都没有用到,而且最后一行的像素没有被运算。

RAM-Based Shift Register (ALTSHIFT_TAPS) IP Core-实现3X3像素阵列存储的更多相关文章

- 阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide

阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide 说明:本文档自带测试工程: DE_ALTSHIFT_TAPS.zip 1.支 ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- 在EDK里面添加ISE IP core的方法

(1)在ISE下,使用core generator,可以得到xilinx的IP的*.v和*.ngc 文件,将这两个文件拷贝出来: (2)在EDK下使用“Create or Import Periphe ...

- 使用xilinx ip core FIFO First- World First-Through (FWFT)模式的注意事项

也许很多人知道xilinx ip core 中的fifo可以配成standard 模式和FWFT模式,并知道两者的区别是:standard模式下,当rd为高时,fifo会延时一个时钟输出数据(时序逻辑 ...

- IP Core 分类

IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的.具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中.到了SOC阶段,IP核 ...

- H.265 Video Encoder IP Core

复制: 开源H.265硬件视频编码器H.265 Video Encoder IP Core是开源的H.265硬件视频编码器,实现了H.265(或叫HEVC)的大部分功能. 它由复旦大学专用集成电路与系 ...

- Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core.通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core ...

- Xilinx 7系列例化MIG IP core DDR3读写

昨晚找了一下,发现DDR3读写在工程上多是通过例化MIG,调用生成IPcore的HDL Functional Model.我说嘛,自己哪能写出那么繁琐的,不过DDR读写数据可以用到状态机,后期再添砖加 ...

- Shift Register(Using Submodule)

/*************************************************** / Shift Register module by Submodule / Progra ...

随机推荐

- (BUILDER)建造者与(FACTORY)工厂模式 的比较

首先,说明下 参考博文 1. 建造者 http://www.cnblogs.com/zhili/p/BuilderPattern.html 2. 抽象工厂 http://www ...

- java使用BigDecimal 实现随机金额红包拆分算法

原创代码,引用注明出处:https://www.cnblogs.com/guangxiang/p/12218714.html @Servicepublic class SplitRedPacketsS ...

- IE8Get请求中文不兼容:encodeURI的使用

IE8Get请求中文不兼容:encodeURI的使用 在开发过程中遇到在IE8下,请求出错. 后发现Get请求中含有中文字符. 使用js自带的encodeURI函数对中文进行编码,问题解决. enco ...

- Redis的学习之路

应用场景 1.作为缓存使用 (1)原始业务功能设计 秒杀 双十一.618 排队购票 (2)运营平台察觉到突发式高频访问热点 突发式热点新闻 (3)高频复杂的统计数据 在线直播 投票排行榜 2.附加功 ...

- 19 01 08 javascript 初学

变量 JavaScript 是一种弱类型语言,javascript的变量类型由它的值来决定. 定义变量需要用关键字 'var' 变量类型 5种基本数据类型:1.number 数字类型2.string ...

- centos通过yum安装php

1.添加php的yum软件仓库 sudo rpm -Uvh https://mirror.webtatic.com/yum/el6/latest.rpm 2.安装php相关软件,执行过程中全部选择ye ...

- HTML5 可缩放矢量图形(2)—SVG基础

参考文档——权威 SVG常识 渲染顺序——后来居上:越后面的元素越可见 单位——可以指定,也可以不指定,默认px,其他:em.%.cm.mm... SVG画布——绘制图像的区域,无限大 SVG视窗—— ...

- potplayer记住播放进度

(右键——选项)F5——播放——记忆视频播放位置

- 吴裕雄--天生自然 JAVASCRIPT开发学习:Date(日期) 对象

<!DOCTYPE html> <html> <head> <meta charset="utf-8"> <title> ...

- CYPHER 语句(Neo4j)

CYPHER 语句(Neo4j) 创建电影关系图 新增 查找 修改 删除 导入 格式转换 创建电影关系图 CREATE (TheMatrix:Movie {title:'The Matrix', re ...