使用FDATOOL生成xilinx中FIR滤波器IP核的系数

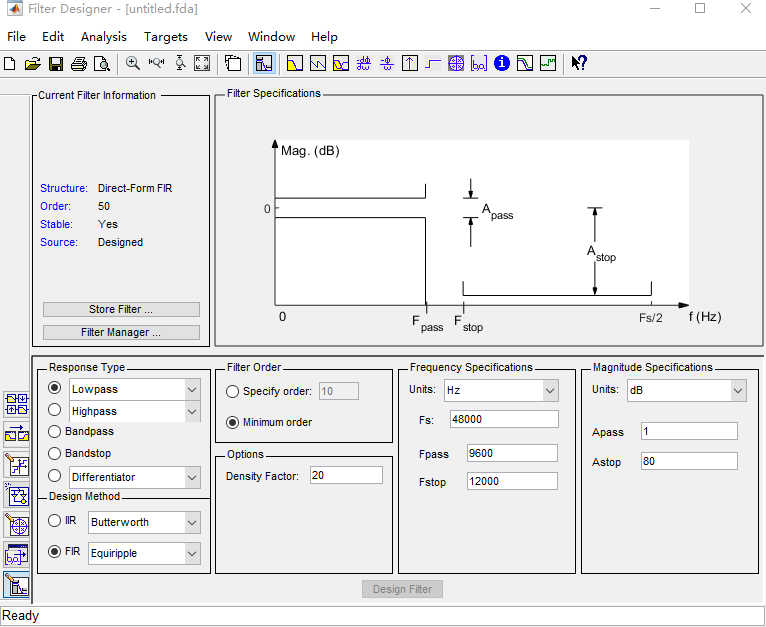

1、在MATLAB命令窗口输入fdatool后回车,打开“Filter Designer & Analysis Tool”工具界面:

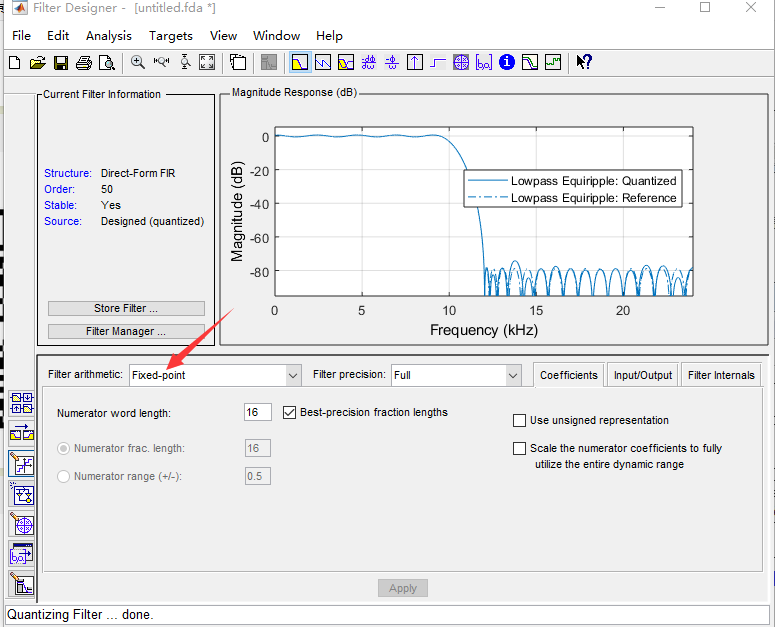

2、点击左下角的Set quantization parameter,设置Filter arithmetic为Fixed-point(定点,由于有些FPGA中是不能直接对浮点数进行操作的,只能采用定点数进行数值运算,参考http://blog.csdn.net/gsh_hello_world/article/details/78742769):

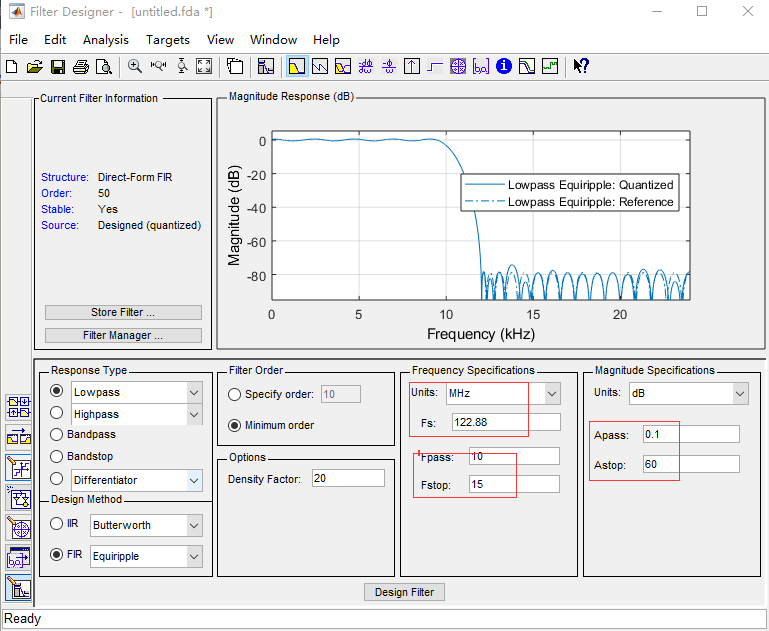

3、点击左下角的Design filter,进入滤波器参数设置页面,在其中设置采样频率(Fs)、通带频率(Fpass)、阻带频率(Fstop)、通带衰减(Apass)以及阻带衰减(Astop)等参数,并点击最下面的“Design Filter”按钮生成滤波器系数

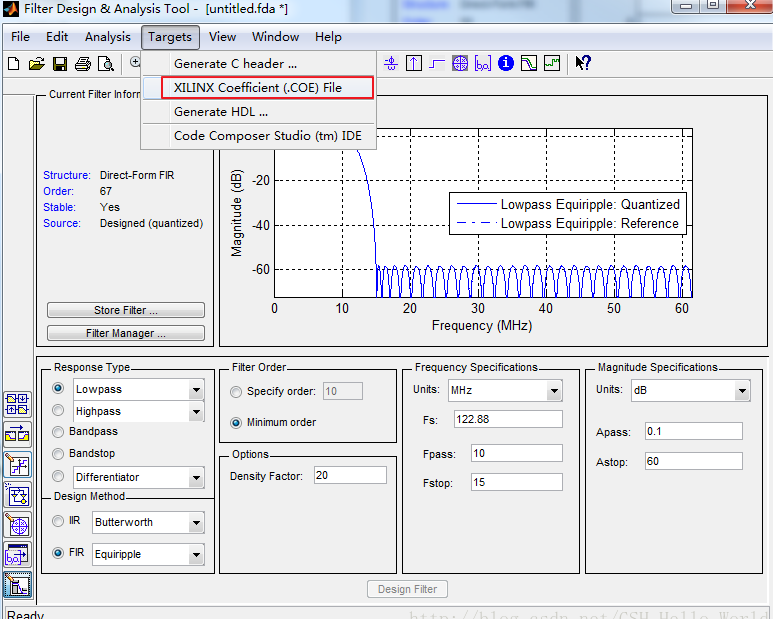

4、Targets —> XILINX Coefficient(.COE) File导出coe文件,此文件中的系数是以定点十六进制表示的,每个数据长度为16位(由Numerator word length决定),其为实际浮点数据左移17位(由Numerator frac. length决定)得到,例如实际浮点数据第一个系数为0.001,定点表示为0x0081((int)0.001 * 2 ^ 17 = 131 = 0x0081,即0.001左移17位):

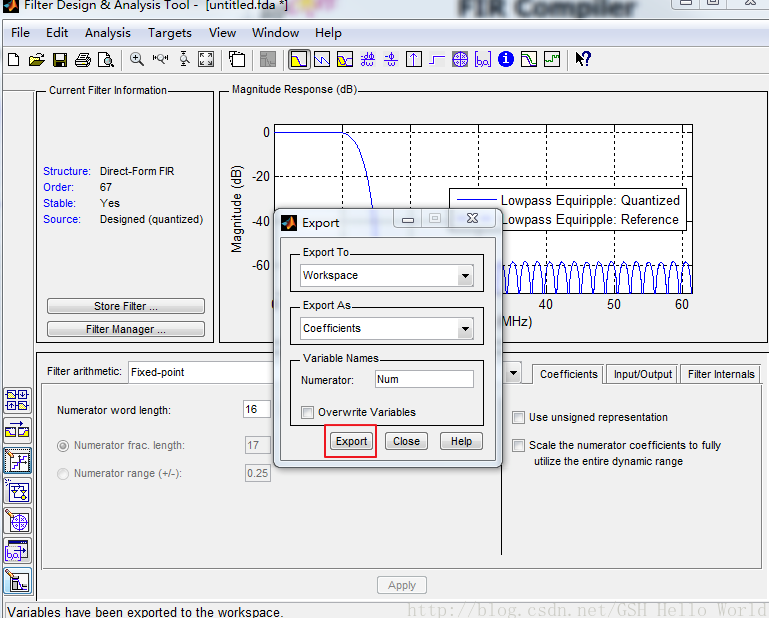

5、也可以点击File —> Export导出滤波器系数到matlab的工作区workspace,快捷键Ctrl+E,这种方式导出的是实际浮点数据:

6、之后生成IP核的步骤参考博客:http://blog.csdn.net/weiweiliulu/article/details/40151053

---------------------

作者:高世皓

来源:CSDN

原文:https://blog.csdn.net/GSH_Hello_World/article/details/78746054

版权声明:本文为博主原创文章,转载请附上博文链接!

使用FDATOOL生成xilinx中FIR滤波器IP核的系数的更多相关文章

- 浅析Xilinx 三速以太网MAC IP核

之前在使用Altera的三速以太网MAC IP的基础上,完成了UDP协议数据传输.此次为了将设计移植到xilinx FPGA上,需要用到xilinx的三速以太网MAC IP核,当然也可以自己用HDL编 ...

- 怎样在Qsys系统中添加第三方IP核

1.新建Quartus II工程 2.新建Qsys系统 3.如果没有我们需要添加的IP,需要自己额外添加 4在我们新建的Quartus工程里面新建一个文件夹,命名为ip; 5.将我们已经下载好的IP文 ...

- Quartus II 软件生成FFT、NCO、FIR等IP核时卡住不动的解决办法

据网友表示,遇到这个问题时,在任务管理器中手动关闭quartus_map进程就可以了,由于我的电脑最近一直没有出问题,因此也无法验证.欢迎大家针对这个问题讨论,提出肯定.否定的说法. 另外,很多人表示 ...

- vivado中使用ROM IP核

1.在project中选择IP Catalog 在IP Catalog中选择---->Block Memory Generator------>RAMs&ROMs&BRAM ...

- vivado中使用MMCM ip核

1.在project中选择IP Catalog 在IP Catalog中选择FPGA Features and Design----->Clocking------>Clocking Wi ...

- 转:基于 xilinx vivado 的PCIE ip核设置与例程代码详解

连接:https://blog.csdn.net/u014586651/article/details/103826967#comments

- Quartus设计FIR滤波器的系数文件格式(适用于FIR II的IP核)

对常用的FIR,我们使用MATLAB的fdatool(或者filterDesigner) 设计滤波器,给定指标,生成系数.为了方便,我们将系数保存到文件,其保存格式比较简介,在此进行说明. 1.FIR ...

- Xilinx Vivado的使用详细介绍(5):调用用户自定义封装的IP核

Zedboard OLED Display Controller IP v1 介绍 Author:zhangxianhe 本文档提供了快速添加,连接和使用ZedboardOLED v1.0 IP内核的 ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

随机推荐

- k8s系列---基于canal的网络策略

文章拷自:http://blog.itpub.net/28916011/viewspace-2215383/ 加上自己遇到的问题简单记录 安装文档:https://docs.projectcalico ...

- linux中的特殊符号及其含义梳理

1. 重定向符号及含义 注意:箭头流向即是数据的流向. 数字0:标准输入(standard input,简写stdin),数据从右往左方向流动 数字1:标准正确输出(standard output,简 ...

- js文本复制插件&vue

/* HTML: * <a href="javascript:;" class="copy" data-clipboard-text="copy ...

- Android中TimePicker时间选择器的使用和获取选择的时和分

场景 实现效果如下 注: 博客: https://blog.csdn.net/badao_liumang_qizhi 关注公众号 霸道的程序猿 获取编程相关电子书.教程推送与免费下载. 实现 将布局改 ...

- AndroidStudio更新时报错:Connection Error,Temp directory inside installation

场景 在将Android Studio的 .AndroidStudio目录修改为别的目录后,打开AS,提示更新,点击更新后提示: Connection Error,Temp directory ins ...

- 关于mac下redis的安装和部署

近来学习scrap分布式,需要用到redis,但以前没接触过,所以记录一下自己的安装过程. 准备:Mac,redis-5.0.4.tar.gz 1.压缩包到官网下(建议下载稳定版)网址:redis.i ...

- linux中shell内置命令和外置命令

shell内置命令 无法通过which或者whereis去查找命令的位置 例如cd,cp这些命令是shell解释器内置的命令 当shell内置命令传入shell解释器,shell解释器通过内核获取相关 ...

- Python 编程入门(2):复杂数据类型(列表,字典)

以下所有例子都基于最新版本的 Python,为了便于消化,每一篇都尽量短小精悍,希望你能尽力去掌握 Python 编程的「概念」,可以的话去动手试一下这些例子(就算目前还没完全搞懂),加深理解. 在 ...

- OHEM论文笔记

目录 引言 Fast R-CNN设计思路 一.动机 二.现有方案hard negative mining 及其窘境 hard negative mining实现 窘境 设计思路 OHEM步骤: 反向传 ...

- PHP0012:PHP操作文件目录

WIN下文件夹的只读权限是0555