我的 FPGA 学习历程(04)—— 练习 verilog 硬件描述语言

这篇讲的是使用 verilog 硬件描述语言编写一个 3 - 8 译码器。

3 - 8 译码器是一个简单的组合逻辑,用于实现并转串,其输入输出关系如下:

| 输入 | 输出 |

-----------------

000 --> 0000_0001

001 --> 0000_0010

010 --> 0000_0100

011 --> 0000_1000

100 --> 0001_0000

101 --> 0010_0000

110 --> 0100_0000

111 --> 1000_0000

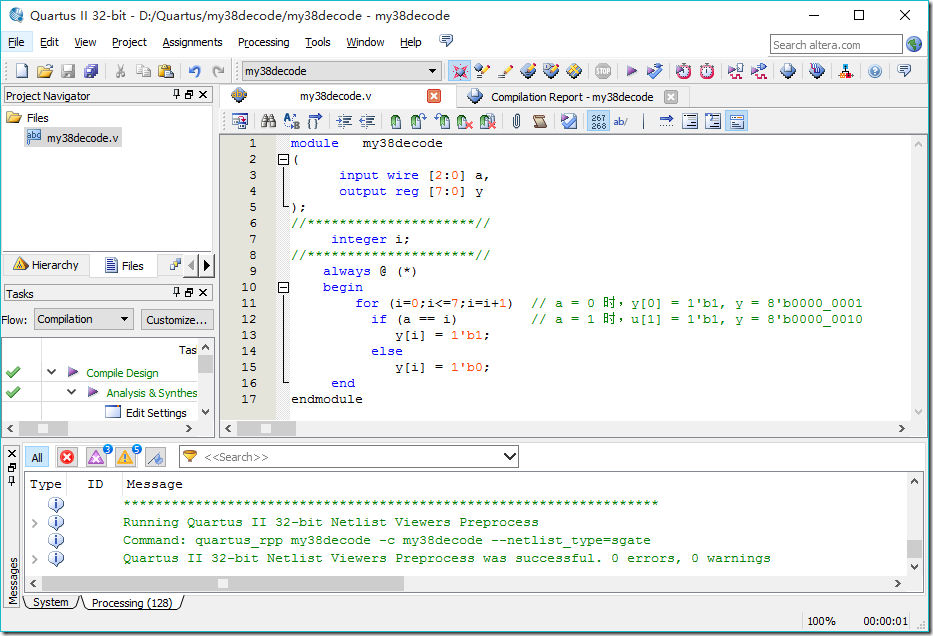

新建工程,并新建如下的代码的 verilog HDL 文件

module my38decode

(

input wire [:] a,

output reg [:] y

);

//*********************//

integer i;

//*********************//

always @ (*)

begin

for (i=;i<=;i=i+) // a = 0 时,y[0] = 1'b1, y = 8'b0000_0001

if (a == i) // a = 1 时,u[1] = 1'b1, y = 8'b0000_0010

y[i] = 'b1;

else

y[i] = 'b0;

end

endmodule

这段代码其实相当抽象(循环变量操作下标),但好在综合工具还是能够理解我们的用意。

建好的工程如下图:

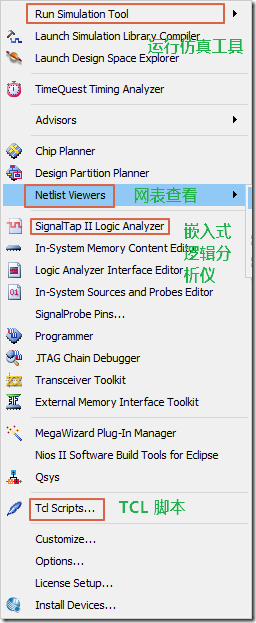

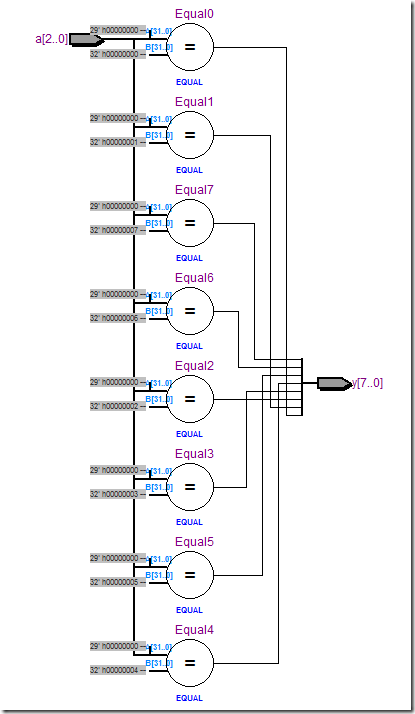

可以在 Tool --> Netlist Viewers --> RTL Viewer 查看生成的 RTL 网表文件。

下图为 Tool 菜单和生成的网表文件。可以看出我们写的代码生成了几个比较器,我们的输入信号被扩大至 32 位(前29位自动填 0);比较器的 B 端口连接的是一些常量,当 32 位比较器在输入相等时输出 1,不等则输出 0;7 个比较器输出分别连接到 y 的 7 个引脚上。如图,综合器在 RTL(寄存器传输级)成功的实现了我们的要求。

我的 FPGA 学习历程(04)—— 练习 verilog 硬件描述语言的更多相关文章

- 我的 FPGA 学习历程(15)—— Verilog 的 always 语句综合

在本篇里,我们讨论 Verilog 语言的综合问题,Verilog HDL (Hardware Description Language) 中文名为硬件描述语言,而不是硬件设计语言.这个名称提醒我们是 ...

- 上一步是硬件描述语言,下一步是FPGA

上一步是硬件描述语言,下一步是FPGA. 学习了硬件描述语言(Verilog或者VHDL)之后,FPGA该如何继续. 世上没有捷径,每一步都得踏踏实实的走.学习FPGA也是这样,在有了硬件描述语言的基 ...

- 硬件描述语言Verilog设计经验总结

一.硬件描述语言Verilog 粗略地看Verilog与C语言有许多相似之处.分号用于结束每个语句,注释符也是相同的(/* ... */和// 都是熟悉的),运算符"=="也用来测 ...

- 我的 FPGA 学习历程(01)—— FPGA 基础知识和 Quartus 的安装

高级的嵌入式市场主要分为以下三类:ARM.DSP 和 FPGA. 其中 ARM 是行业内的佼佼者,目前几乎所有的安卓智能手机都使用 ARM 授权的 CPU架构:而 DSP(数字信号处理器) 早年就被大 ...

- 我的 FPGA 学习历程(09)—— 时序逻辑入门

讲到这篇时,组合逻辑就告一段落了,下面是一些总结: 描述组合逻辑时,always 语句中的敏感信号列表中需要列出全部的可能影响输出的变量 描述组合逻辑时,always 语句中的赋值总是使用阻塞赋值符号 ...

- 我的 FPGA 学习历程(12)—— 电子钟项目准备

初学 FPGA 的时候,我们总是存在很多疑问,比如:xilinx 和 altera 的 FPGA 那种比较好.verilog 语言被如何综合成具体硬件电路.RTL 级电路是什么意思等等.现在我们就不会 ...

- 我的 FPGA 学习历程(05)—— 使用 Modelsim 仿真工具

在第 3 篇中讲到了如何使用图形进行仿真激励输入,图形输入法尽管简单易学,但如若要求复杂的仿真输入激励.较长的仿真时间或是要求打印输出信息乃至输出文件日志则显得不够用了. 本篇以上一篇的 3-8 译码 ...

- 我的 FPGA 学习历程(02)—— 实验:点亮 LED 灯

关于 Quartus 的操作可以使用 Quartus 自带的帮助,帮助中带有全套的操作教程. 中文网络教程链接(链接至 altera中文官网,点击观看) Quartus II 软件设计系列:基础 Qu ...

- 我的 FPGA 学习历程(07)—— BCD 编码:移位加 3 算法

2-10 进制码,也称为 BCD 码,它的编码方式则是通过一个 4 位二进制来表示一个 10 进制数,部分十进制对应的 BCD 码如下 十进制数 | BCD 码 13 --> 0001_0011 ...

随机推荐

- MAC OS进阶必看——这10个技巧让你秒变MAC达人

文章内容及图片来源于:什么值得买,如果涉及版权问题,请联系作者删除 文章收录于:风云社区(提供上千款各类mac软件的下载) 使用mac系统也有好几个年头,出色的办公效率以及越来越广的兼容性让mac成为 ...

- C# this扩展方法

本文导读:扩展方法被定义为静态方法,但它们是通过实例方法语法进行调用的. 它们的第一个参数指定该方法作用于哪个类型,并且该参数以 this 修饰符为前缀. 扩展方法当然不能破坏面向对象封装的概念,所以 ...

- dubbo和zikkeper的使用

1.先来一段异常看看:No provider available for the service 16:05:25.755 [localhost-startStop-1] WARN o.s.w.c.s ...

- 2018年7月6日go语言学习

Go是一门并发支持.垃圾回收的编译型系统编程语言. 特点:类型安全和内存安全 以非常直观和极低的方案实现高并发 高效的垃圾回收机制 快速编译 为多核计算机提供性能提升方案 Utf-8编码支持 Go源码 ...

- 题解-Codeforces1106全套

因为参加完wc后心情很差,而且在广州过年没Ubuntu,所以就没打这场比赛了,结果这套题全部1A了,现在看来真是错失良机 结果这场不计rating 今天是除夕,大家节日快乐 A. Lunar New ...

- Spring扩展自定义的XML标签

在网上搜了许多,感觉不够全面,就找了官方文档,下面记录如何找到对应的文档进入 网上许多博客都是以dateformat为实例进行编写的,通过官方的foo,能够学到更多的东西,下面贴一段代码,在官方示例上 ...

- Mockito框架入门教程(二)

接上一篇,继续学习其它的.... 8.找出冗余的互动(即未被验证到的) @Test(expected = NoInteractionsWanted.class) public void find_re ...

- Linux -- Centos6 yum安装相关问题与处理

Centos6 yum安装相关问题与处理 由于要使用yum下载文件,突然yum下载不了想要的文件,想更换yum源,结果得重新安装yum 来自本人GitHub地址https://github.com/m ...

- 【原创】Linux基础之linux服务器服务器间拷贝文件

linux服务器服务器间拷贝文件,有几种方式: 1 如果是定时任务,可以用rsync 2 如果是基于ssh登录,可以用scp,优点是可以实现远程到远程的拷贝,缺点是需要账号密码 upload: scp ...

- java控台输入

import java.util.Scanner;//访问util包的Scanner(控台输入) public class HelloWorld {public static void main(St ...