我的 FPGA 学习历程(04)—— 练习 verilog 硬件描述语言

这篇讲的是使用 verilog 硬件描述语言编写一个 3 - 8 译码器。

3 - 8 译码器是一个简单的组合逻辑,用于实现并转串,其输入输出关系如下:

| 输入 | 输出 |

-----------------

000 --> 0000_0001

001 --> 0000_0010

010 --> 0000_0100

011 --> 0000_1000

100 --> 0001_0000

101 --> 0010_0000

110 --> 0100_0000

111 --> 1000_0000

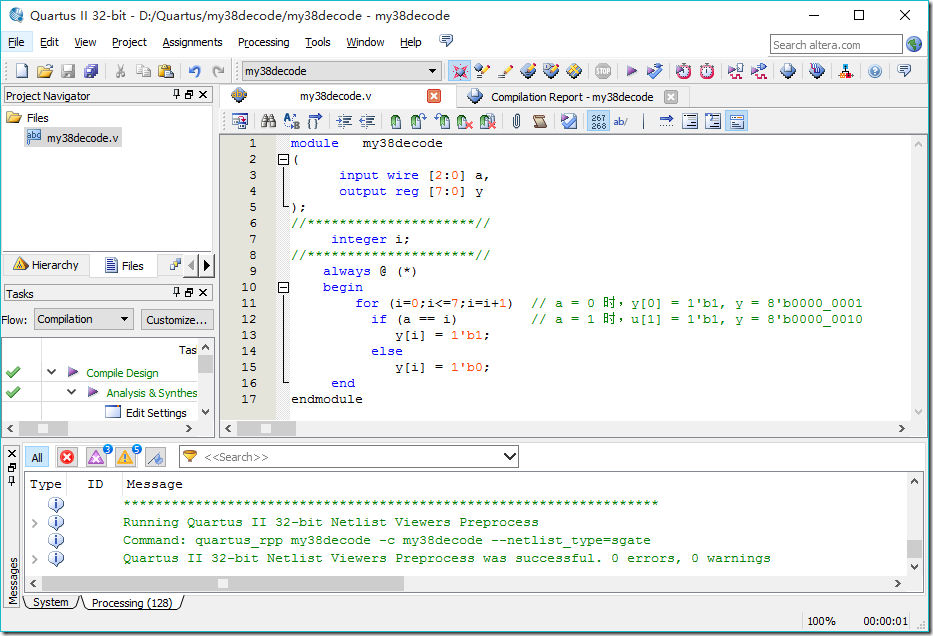

新建工程,并新建如下的代码的 verilog HDL 文件

module my38decode

(

input wire [:] a,

output reg [:] y

);

//*********************//

integer i;

//*********************//

always @ (*)

begin

for (i=;i<=;i=i+) // a = 0 时,y[0] = 1'b1, y = 8'b0000_0001

if (a == i) // a = 1 时,u[1] = 1'b1, y = 8'b0000_0010

y[i] = 'b1;

else

y[i] = 'b0;

end

endmodule

这段代码其实相当抽象(循环变量操作下标),但好在综合工具还是能够理解我们的用意。

建好的工程如下图:

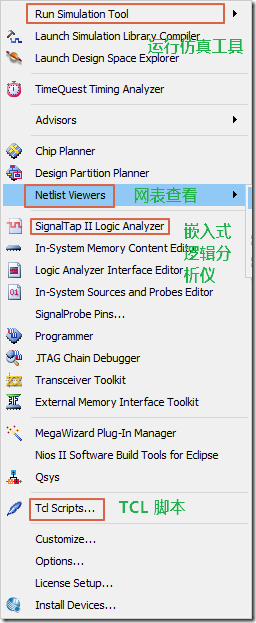

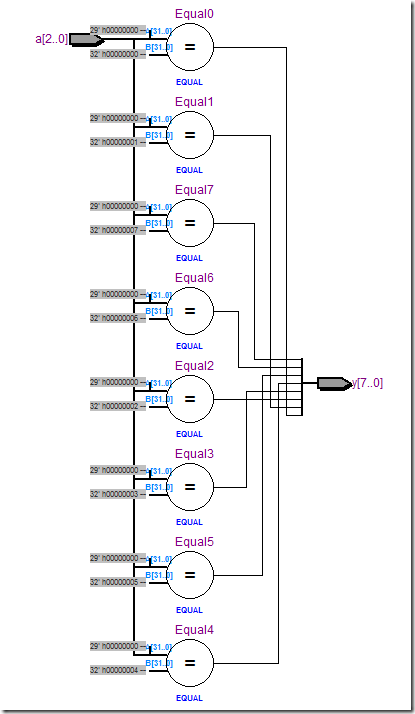

可以在 Tool --> Netlist Viewers --> RTL Viewer 查看生成的 RTL 网表文件。

下图为 Tool 菜单和生成的网表文件。可以看出我们写的代码生成了几个比较器,我们的输入信号被扩大至 32 位(前29位自动填 0);比较器的 B 端口连接的是一些常量,当 32 位比较器在输入相等时输出 1,不等则输出 0;7 个比较器输出分别连接到 y 的 7 个引脚上。如图,综合器在 RTL(寄存器传输级)成功的实现了我们的要求。

我的 FPGA 学习历程(04)—— 练习 verilog 硬件描述语言的更多相关文章

- 我的 FPGA 学习历程(15)—— Verilog 的 always 语句综合

在本篇里,我们讨论 Verilog 语言的综合问题,Verilog HDL (Hardware Description Language) 中文名为硬件描述语言,而不是硬件设计语言.这个名称提醒我们是 ...

- 上一步是硬件描述语言,下一步是FPGA

上一步是硬件描述语言,下一步是FPGA. 学习了硬件描述语言(Verilog或者VHDL)之后,FPGA该如何继续. 世上没有捷径,每一步都得踏踏实实的走.学习FPGA也是这样,在有了硬件描述语言的基 ...

- 硬件描述语言Verilog设计经验总结

一.硬件描述语言Verilog 粗略地看Verilog与C语言有许多相似之处.分号用于结束每个语句,注释符也是相同的(/* ... */和// 都是熟悉的),运算符"=="也用来测 ...

- 我的 FPGA 学习历程(01)—— FPGA 基础知识和 Quartus 的安装

高级的嵌入式市场主要分为以下三类:ARM.DSP 和 FPGA. 其中 ARM 是行业内的佼佼者,目前几乎所有的安卓智能手机都使用 ARM 授权的 CPU架构:而 DSP(数字信号处理器) 早年就被大 ...

- 我的 FPGA 学习历程(09)—— 时序逻辑入门

讲到这篇时,组合逻辑就告一段落了,下面是一些总结: 描述组合逻辑时,always 语句中的敏感信号列表中需要列出全部的可能影响输出的变量 描述组合逻辑时,always 语句中的赋值总是使用阻塞赋值符号 ...

- 我的 FPGA 学习历程(12)—— 电子钟项目准备

初学 FPGA 的时候,我们总是存在很多疑问,比如:xilinx 和 altera 的 FPGA 那种比较好.verilog 语言被如何综合成具体硬件电路.RTL 级电路是什么意思等等.现在我们就不会 ...

- 我的 FPGA 学习历程(05)—— 使用 Modelsim 仿真工具

在第 3 篇中讲到了如何使用图形进行仿真激励输入,图形输入法尽管简单易学,但如若要求复杂的仿真输入激励.较长的仿真时间或是要求打印输出信息乃至输出文件日志则显得不够用了. 本篇以上一篇的 3-8 译码 ...

- 我的 FPGA 学习历程(02)—— 实验:点亮 LED 灯

关于 Quartus 的操作可以使用 Quartus 自带的帮助,帮助中带有全套的操作教程. 中文网络教程链接(链接至 altera中文官网,点击观看) Quartus II 软件设计系列:基础 Qu ...

- 我的 FPGA 学习历程(07)—— BCD 编码:移位加 3 算法

2-10 进制码,也称为 BCD 码,它的编码方式则是通过一个 4 位二进制来表示一个 10 进制数,部分十进制对应的 BCD 码如下 十进制数 | BCD 码 13 --> 0001_0011 ...

随机推荐

- 【洛谷P1313 计算系数】

题目连接 #include<algorithm> #include<iostream> #include<cstring> #include<cstdio&g ...

- AHOI2019N省联考凉凉记

博主并未时空穿越,本文没有对选手造成恐慌 DAY0 这已经是我第四次省选了,时间真快啊,怀念三年前毫无压力的省选,考完以后如果有时间并且没退役的话可能会陆续搬以前写在别处的游记(主要是2018年的游记 ...

- PowerShell Empire使用笔记

##安装过程 git clone https://github.com/EmpireProject/Empire.git cd Empire cd setup sudo ./install.sh ## ...

- 微信小程序无法定位

获取定位的时候报:errMsg:getLocation:fail:require permission desc 错 解决办法: 在app.js加入代码 //app.js新增如下代码 config = ...

- EF CodeFirst系列(6)---配置1对1,1对多,多对多关系

这一节介绍EF CodeFirst模式中的1对0/1,1对多,多对多关系的配置,只有梳理清楚实体间的关系,才能进行愉快的开发,因此这节虽然很简单但是还是记录了一下. 1. 1对0/1关系配置 1. 通 ...

- LCA(ST倍增)

时间复杂度: dfs树,求st表(状态数组f):O(NlgN) 处理M个查询:O(MlgN) 总:O((M+N)lgN) #include<iostream> #include<cs ...

- 使用SO_REVTIMEO套接字选项为recvfrom设置超时

void dg_cli(FILE *fp, int sockfd, const SA *pservaddr, socklen_t servlen) { int n; ]; struct timeval ...

- [译]Ocelot - Middleware Injection and Overrides

原文 使用这个特性的时候要小心点. 可以如下一样提供一些中间件用以覆盖默认的中间件: var configuration = new OcelotPipelineConfiguration { Pre ...

- HttpUtility.UrlEncode编码重写

1. 某些系统方法,例如.NET系统方法HttpUtility.UrlEncode会将‘=’编码成‘%3d’,而不是%3D,导致加密签名通不过验证,请开发者注意检查. 2.Java 1.3和早期版本中 ...

- salt软件远程控制服务器

1.salt安装服务器环境 准备2台机器 192.168.11.250 master端(主人) 192.168.11.167 minion端 (奴隶 ) 2.两台机器配置hosts文件,用于加速域名解 ...