Translation Lookaside Buffer

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION

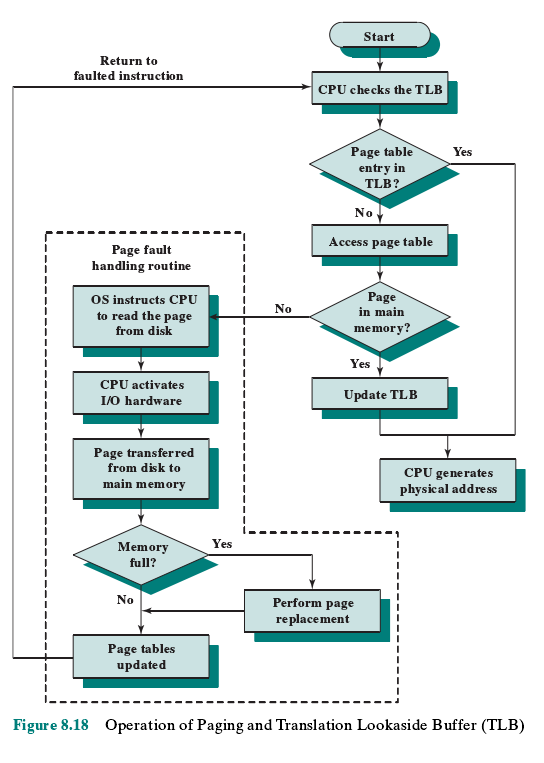

In principle, then, every virtual memory reference can cause two physical mem-

ory accesses: one to fetch the appropriate page table entry, and one to fetch the

desired data. Thus, a straightforward virtual memory scheme would have the effect

of doubling the memory access time. To overcome this problem, most virtual

memory schemes make use of a special cache for page table entries, usually called

a translation lookaside buffer (TLB). This cache functions in the same way as a

memory cache and contains those page table entries that have been most recently

used. Figure 8.18 is a flowchart that shows the use of the TLB. By the principle of

locality, most virtual memory references will be to locations in recently used pages.

Therefore, most references will involve page table entries in the cache. Studies of

the VAX TLB have shown that this scheme can significantly improve performance

[CLAR85, SATY81].

Note that the virtual memory mechanism must interact with the cache system

(not the TLB cache, but the main memory cache). This is illustrated in Figure 8.19.

A virtual address will generally be in the form of a page number, offset. First, the

memory system consults the TLB to see if the matching page table entry is present.

If it is, the real (physical) address is generated by combining the frame number with

the offset. If not, the entry is accessed from a page table. Once the real address is

generated, which is in the form of a tag and a remainder, the cache is consulted to

see if the block containing that word is present (see Figure 4.5). If so, it is returned

to the processor. If not, the word is retrieved from main memory.

The reader should be able to appreciate the complexity of the processor hard-

ware involved in a single memory reference. The virtual address is translated into

a real address. This involves reference to a page table, which may be in the TLB, in

main memory, or on disk. The referenced word may be in cache, in main memory,

or on disk. In the latter case, the page containing the word must be loaded into main

memory and its block loaded into the cache. In addition, the page table entry for

that page must be updated.

Translation Lookaside Buffer的更多相关文章

- 全面学习理解TLB(Translation Look-aside Buffer)地址变换高速缓存

全面学习理解TLB(Translation Look-aside Buffer)地址变换高速缓存 前言: 本文学习思路是:存在缘由 --> 存在好处 --> 定义性质 --> 具 ...

- PatentTips - Virtual translation lookaside buffer

BACKGROUND OF THE INVENTION A conventional virtual-machine monitor (VM monitor) typically runs on a ...

- 【转】TLB(Translation Lookaside Buffers,TLB)的作用

原文网址:http://sdnydubing.blog.163.com/blog/static/137470570201122810503396/ 从虚拟地址到物理地址的转换过程可知:使用一级页表进行 ...

- Linux中Buffer和Cache的区别

1. Cache:缓存区,是高速缓存,是位于CPU和主内存之间的容量较小但速度很快的存储器,因为CPU的速度远远高于主内存的速度,CPU从内存中读取数据需等待很长的时间,而 Cache保存着CPU刚 ...

- armv8 memory translation

AArch32,arm的32bit架构: AArch64,arm的64bit架构: ARMv8.2-LPA,是armv8.2中的新feature,扩大了IPA和PA的支持范围,从48bit扩展到52b ...

- Cache 和 Buffer 都是缓存,主要区别是什么?【转】

作者:Towser 链接:https://www.zhihu.com/question/26190832/answer/32387918 来源:知乎 著作权归作者所有.商业转载请联系作者获得授权,非商 ...

- 【学习笔记】cache/buffer

cache 是为了弥补高速设备和低速设备的鸿沟而引入的中间层,最终起到**加快访问速度**的作用.buffer 的主要目的进行流量整形,把突发的大数量较小规模的 I/O 整理成平稳的小数量较大规模的 ...

- cache和buffer区别探讨

一. 1.Buffer(缓冲区)是系统两端处理速度平衡(从长时间尺度上看)时使用的.它的引入是为了减小短期内突发I/O的影响,起到流量整形的作用.比如生产者——消费者问题,他们产生和消耗资源的速度大体 ...

- PatentTips - Supporting address translation in a virtual machine environment

BACKGROUND A conventional virtual-machine monitor (VMM) typically runs on a computer and presents to ...

随机推荐

- (二)WebRTC手记之框架与接口

转自:http://www.cnblogs.com/fangkm/p/4370492.html 转载请注明出处:http://www.cnblogs.com/fangkm/p/4370492.html ...

- linux下动态库so文件的一些认识

转自:http://mypyg.iteye.com/blog/845915 个人创作,欢迎指错. 牵扯到ELF格式,gcc编译选项待补,简单实用的说明一下,对Linux下的so文件有个实际性的认识. ...

- HDU 4341 分组背包

B - Gold miner Time Limit:2000MS Memory Limit:32768KB Description Homelesser likes playing ...

- 利用Bundle在activity之间传递对象

(2010-12-04 09:45:54) 转载▼ 标签: it 分类: android开发 转自:http://chen592969029.javaeye.com/blog/772656 假如需要在 ...

- Hark的数据结构与算法练习之梳排序

算法说明梳排序是交换排序的一种,它其实也是改自冒泡排序,不同之处是冒泡排序的比较步长恒定为1,而梳排序的比较步长是变化的. 步长需要循环以数组长度除以1.3,到最后大于等于1即可. 光说可能比较抽象, ...

- POJ2396 Budget(有源汇流量有上下界网络的可行流)

题目大概给一个有n×m个单元的矩阵,各单元是一个非负整数,已知其每行每列所有单元的和,还有几个约束条件描述一些单元是大于小于还是等于某个数,问矩阵可以是怎样的. 经典的流量有上下界网络流问题. 把行. ...

- HDU4859 海岸线(最小割)

题目大概就是说一个n*m的地图,地图上每一块是陆地或浅海域或深海域,可以填充若干个浅海域使其变为陆地,问能得到的最长的陆地海岸线是多少. 也是很有意思的一道题. 一开始想歪了,想着,不考虑海岸线重合的 ...

- BZOJ2789 : [Poi2012]Letters

按照顺序依次找到b串每个字母最后的位置,然后求逆序对. #include<cstdio> #define N 1000010 int n,i,j,k,g[26],nxt[N],bit[N] ...

- 自己的一份Spring的xml配置文件

<?xml version="1.0" encoding="UTF-8"?><beans xmlns="http://www.spr ...

- FFT模板

我终于下定决心学习FFT了. orzCHX,得出模板: #include<cstdio> #include<cctype> #include<queue> #inc ...