lower power设计中的DVFS设计

Pswitch = Ceff * Vvdd^2*Fclk,

Pshort-circuit = Isc * Vdd * Fclk,

Pleakage = f(Vdd, Vth, W/L)

尽管对电压的scaling,可以以平方的关系减小dynamic/leakage power,但是voltage的scaling会影响gate delay,

setup/hold timing,memory access time scale。

voltage 的dynamic scaling,在processor和multi media的sys中会有明显的作用。

但是每一个votage的产生,都需要一个regulator的配合,会造成设计的复杂。每一个votage的产生都需要额外的power rail,

造成power的浪费,所以一般都将voltage和frequency作为N个离散的pair来进行设计。

如何根据应用场景scenario,来决定voltage的大小是一个比较困难的事情。

可以通过FPGA的Prototype仿真来完成。

freq的降低,会使得处理时间增加,所以从任务处理方面来看,并没有节能,

主要是因为电压的降低不支持那么高的Freq,所以需要进行scaling。

常见的几种voltage scale的技术:

1)static votage scaling(SVS):不同的block和sys,给不同的fixed voltage。

2)Multi-level votage scaling(MVS):一个block和sys的voltage可以在几个不同值之间switch。

3)Dynamic voltage and Frequency scaling(DVFS):工作电压根据workload进行动态的调整。

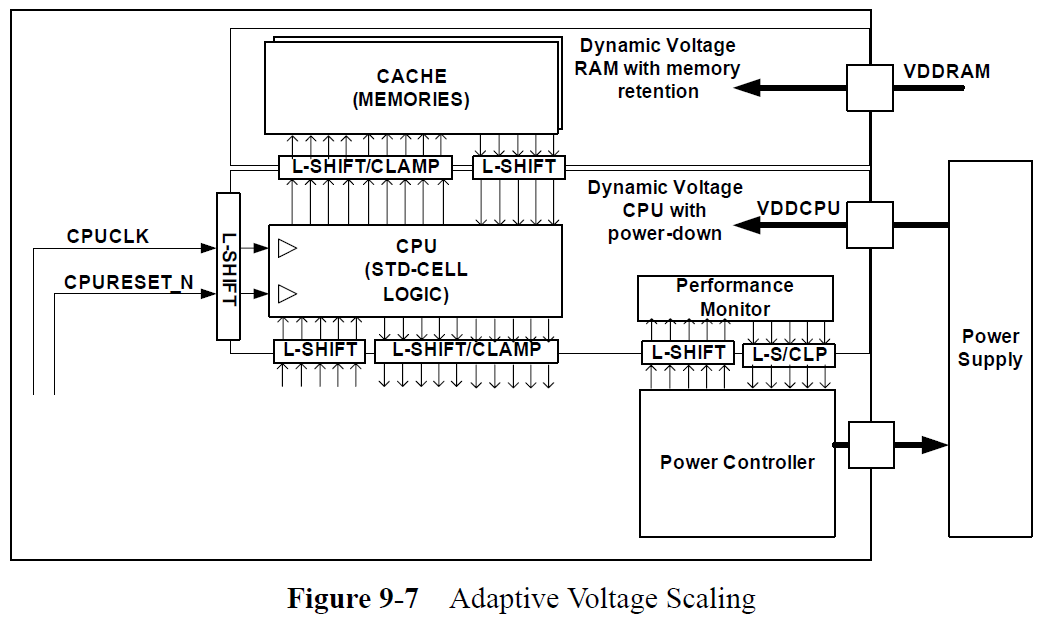

4)Adaptive voltage scaling(AVS):一个闭环的电压调节控制。

针对DVFS来说:

在需要增加Freq,over drive的情况下:软件首先决定最小的clock frequency,再决定最小的voltage供应。

1)cpu program power supply to new voltage。(cpu可以换为其他逻辑)

2)cpu继续工作在现有freq,直到voltage稳定。

3)cpu program新的freq,可以是clock divider或者PLL,如果是PLL,则需要花费更多时间等待PLL稳定。

如果是要降低Freq,则执行顺序:

1)cpu program新的voltage。

2)等待clock divider或者PLL稳定。

3)cpu program新的voltage。

总之Freq只有在voltage增加之后,才能提高,Freq必须在voltage减小前,先降低。

针对timing/voltage的value。

很多的DVFS系统都设置一些discrete voltage/frequency pair。

如果pair太少,可能省电效果不好,太多可能造成decide逻辑冗杂。

可以根据:clock_divider可产生的值,voltage regulator的值来决定。

但是必须保证voltage的值在temperature inversion point以上。(一般情况下delay随着voltage的增加而减小,

delay随着temperature的增加而增加,但是,当voltage的值小于2Vt时,delay的值随着temperature的增加而减小)

(这个voltage的值不确定???)

voltage level的switch可能需要较长的时间,在做design时,可能需要加入counter等延时单元来等待。

如果Freq的scaling涉及到PLL,在relock有效之前,可以先利用别的clock保证logic的有效执行,在lock之后,进行切换。

DVFS是一个open loop的系统,通过frequency/voltage的预留margin来保证不同的PVT下,也可以正常工作。

但是AVS是一个close loop的系统,通过voltage scaling的power supply和delay sensing的performance monitor进行工作。

在DVFS block和剩下的sys之间,最好不要使用sync interface,因为电压的不同会导致clock的skew不同。

可以使用async逻辑或者latch

lower power设计中的DVFS设计的更多相关文章

- 2014年的Google I/O app设计中的材料设计-渣渣的翻译

又是一篇翻译,用了三个多小时.http://android-developers.blogspot.co.id/2014/08/material-design-in-2014-google-io-ap ...

- Lower Power with CPF(一)

CPF(Common Power Format):cadence推出的一种在设计中描述低功耗设计的文件.完全按Tcl的语言格式来定义. CPF文件在整个前端后端的过程中,需要的部分不一样,所以CPF文 ...

- lower power的IP设计

在IP的实现过程中,考虑lower power部分进行设计: 1)Partition the design来满足lower power的一些strategies,尤其是power gating和clo ...

- 在嵌入式设计中使用MicroBlaze(Vivado版本)(转)

原文Xilinx官方文档<ug898-vivado-embedded-design>第三章 一.MicroBlaze处理器设计介绍(略) 二.创建带有MicroBlaze处理器的IP设计 ...

- 在嵌入式设计中使用MicroBlaze(Vivado版本)

原文Xilinx官方文档<ug898-vivado-embedded-design>第三章 一.MicroBlaze处理器设计介绍(略) 二.创建带有MicroBlaze处理器的IP设计 ...

- mysql中数据库的设计

软件开发流程(CMMI): 1):项目启动; 2):项目计划: 3):需求分析; 需要得到的结果是什么? 4):系统设计; 该怎么做? 5):系统开发; 6):系统测试; 7):系 ...

- 数据库设计中的Soft Delete模式

最近几天有点忙,所以我们今天来一篇短的,简单地介绍一下数据库设计中的一种模式——Soft Delete. 可以说,该模式毁誉参半,甚至有非常多的人认为该模式是一个Anti-Pattern.因此在本篇文 ...

- UI设计中的48dp定律【转】

有朋友建议我偶尔写写技术类的文章,所以我打算开始穿插性的写一些偏技术方面的科普文章,尽量往小白能看懂的方向写,今天我来讲讲UI设计中的48dp定律. 那么先说说什么是dp ?其实对于一个非技术人员要把 ...

- 浅谈UI设计中妙用无穷的深色系背景

英文:medium 译者:优设网 - 陈子木 链接:http://www.uisdc.com/ui-benefits-of-dark-background# --------------------- ...

随机推荐

- 软件的NABCD----安装部分

N:需求 有些软件安装需要很多的插件,很很多的安装步骤,甚至文件夹移动等麻烦的步骤 A:做法 做成一键安装的程序 B:好处 默认D盘安装,节省C盘空间,没有赘余插件,一键安装,省时省力. C:竞争 和 ...

- Eclipse中直接双击执行bat时路径问题

之前bat中使用的是 cd %cd% 这样在文件夹中直接运行bat是没问题的 但在eclipse中运行, 取得的路径就是eclipse.exe的所在路径 而如果需要获得bat文件的实际所在路径 应该使 ...

- 通过定位position="fixed"实现网页内容的固定层效果

在网页的顶部或者底部导航栏中经常需要使用到固定层的效果,即紧挨浏览器窗口的顶部或底部而网页其他内容的影响. 一.实现 主要通过设置导航栏元素的位置属性position="fixed" ...

- linux bq20z75 驱动

新的项目中使用到了电池.电池的guage使用TI的bq20z75.kernel的驱动中已经有bq20z75的驱动,只要稍加修改就可以使用. 参考链接 http://www.ti.com/lit/er/ ...

- Redis实现分布式锁

http://redis.io/topics/distlock 在不同进程需要互斥地访问共享资源时,分布式锁是一种非常有用的技术手段. 有很多三方库和文章描述如何用Redis实现一个分布式锁管理器,但 ...

- Java: arr==null vs arr.length==0

当 arr 是一个array时,写Java开始的corner case常常会写类似下面的语句: if(arr == null || arr.length == 0){ return 0; } 其实这是 ...

- each的用法

$(selector).each(function(index,element)) function(index,element) 必需.为每个匹配元素规定运行的函数. index - 选择器的 in ...

- 30天,O2O速成攻略【8.15长沙站】

活动概况 时间:2015年08月15日13:30-16:30 地点:库可咖啡(长沙市岳麓区阜埠河路139号天马都乐街,湖南大学天马学生公寓东侧) 主办:APICloud.爱立示.兰软 网址:www.a ...

- def文件格式

模块定义 (.def) 文件 模块定义 (.def) 文件为链接器提供有关被链接程序的导出.属性及其他方面的 信息.生成 DLL 时,.def 文件最有用.由于存在 ...

- 11月23日《奥威Power-BI报表集成到其他系统》腾讯课堂开课啦

听说明天全国各地区都要冷到爆了,要是天气冷到可以放假就好了.想象一下大冷天的一定要在被窝里度过才对嘛,索性明天晚上来个相约吧,相约在被窝里看奥威Power-BI公开课如何? 上周奥威公开 ...