Cadence套件:Capture + Allegro应用笔记

1、在Allegro中导入Netlist时,需要进行封装路径的设定:

在Setup->User Preference的Path->Library下面,设定所需封装文件(psm)、焊盘文件(pad)的路径。

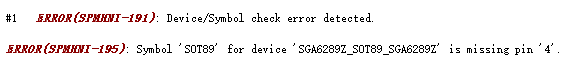

2、在Allegro中导入Netlist时,报错:

ERROR的原因是,搜索封装库的时候先搜索到了Cadence的官方库,所以将它匹配。官方的封装按3个引脚来算,而我在原理图中的器件指定了4个引脚,所以这是一个重名带来的报错。

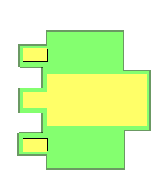

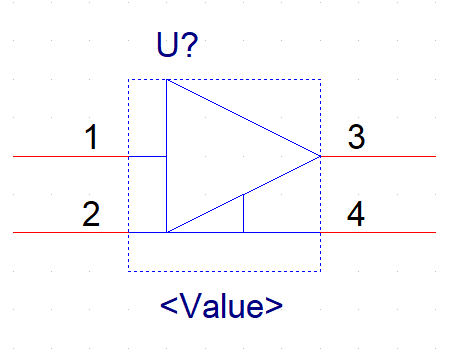

SOT89官方封装(3-Pin) 原理图中器件(4-Pin) 我设计的封装(4-Pin)

3、Shape Polygon如何进行放置和调整?

Polygon可以完成大面积铺铜、整个平面灌铜,实现走险宽度渐变等操作,非常实用,实现办法如下:

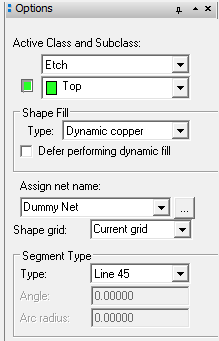

(1)菜单栏Shape->Polygon,然后在Options窗口里面进行参数选定:选择Etch铜皮,选择Polygon需要的层,选择这个Polygon的电气网络。我们还可以指定鼠标画Polygon时候的走线形状(如45度拐角、90度拐角、直线段连接、圆弧线等)。

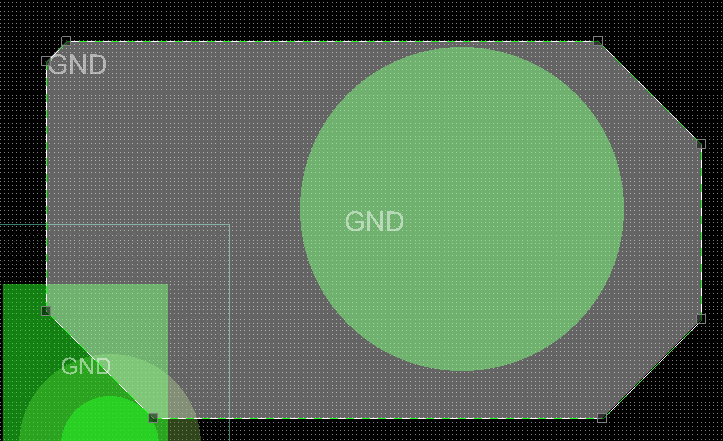

(2)用鼠标或者坐标命令画出Polygon的各个顶点、各个边,如图,画了一个GND的铜皮:

(3)调整铜皮形状:先选中铜皮,菜单栏Shape->Select Shape or Void/Cavity,然后鼠标点选需要更改的铜皮。

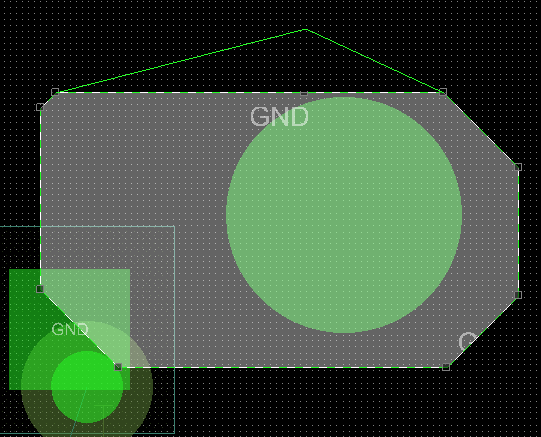

改变形状:此时发现铜皮顶点多了灰色正方形小点,如图:

有几种方式可以进行改变铜皮形状:

(1)改变顶点位置:鼠标在铜皮顶点灰色方块上,左键拖动/左键单击顶点位置,然后进行位置调整。

(2)从某一个边上拉出新的顶点:鼠标在这个边上,左键单击,然后进行位置调整。

(3)平行拖动某一个边:鼠标在这个边上,左键单击并拖动,然后进行拖动。

4、层叠设计。(Layer Stack)

在菜单栏Setup->Cross-section可以进行设定,如图是一个四层板的设定:

右下角还可以根据走线宽度进行阻抗的初步计算。

5、铺铜间距和最小间距调整。(Spacing,Clearance)

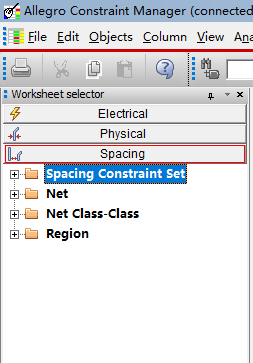

在菜单栏Setup->Constraints->Spacing可以进行选择。间距调整是以“A距离B”的形式设定的。以4层板为例,设定所有Shape到其他的物体的距离,如图:

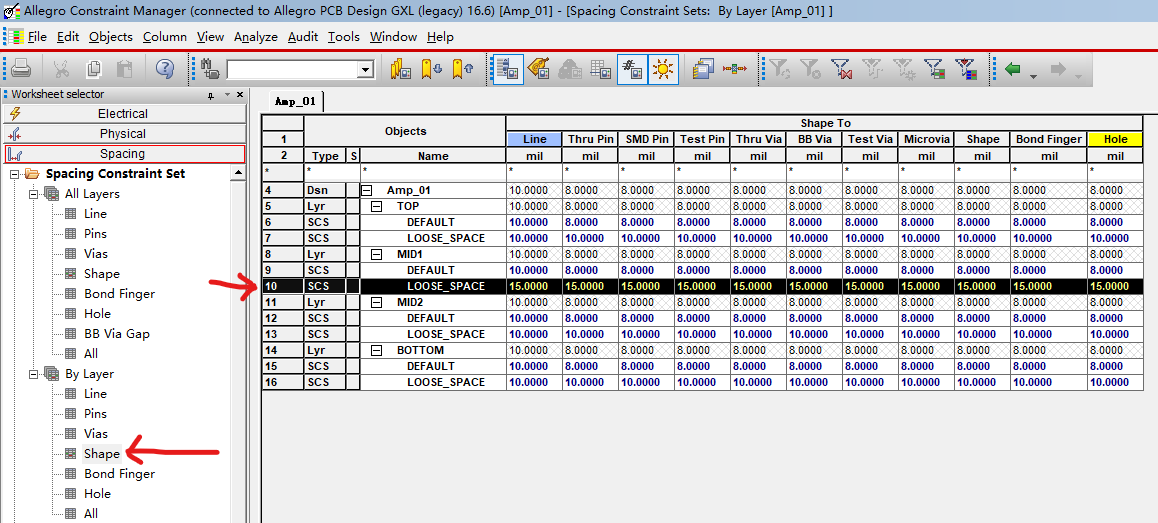

表格中有两套约束,分别是Default和Loose_Space,他们可以分别起作用。

还可以依据网络来分别设定最小间距:如电源层中VCC和GND的Shape间距设定为15mil,而表层信号线和GND的Shape间距设定为8mil,等等。

具体做法:

(1)在这里有四个选项栏,其中第一个Spacing Constraint Set(Spacing Cset,SCS)是用来编辑不同的约束组(Constraint Set)的,每个约束组之间是互不干扰的。比如上面这个图就有两个组,Default和Loose_Space。注意Default是唯一一个不能删除的组。

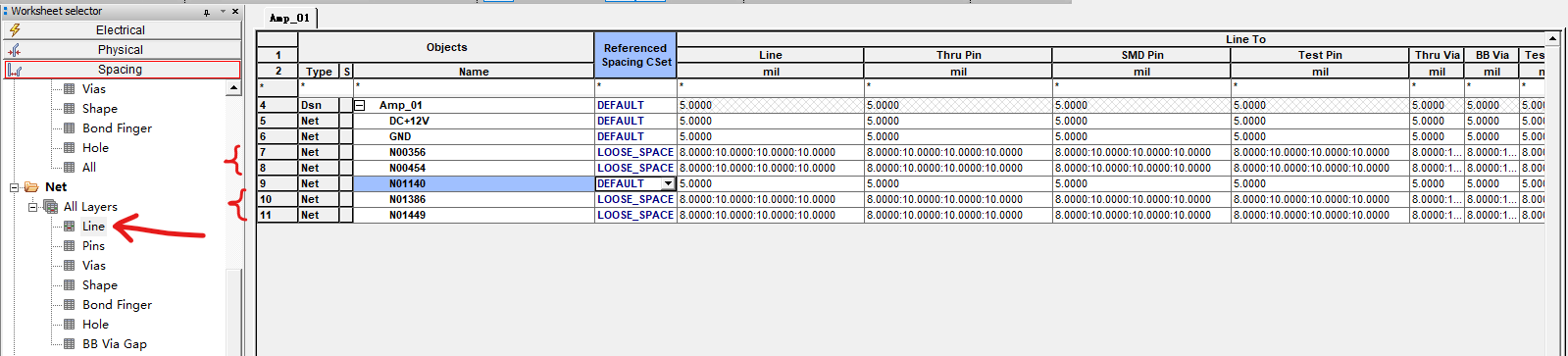

(2)有了SCS,我们可以在下面的Net、Net Class-Class和Region选项框内设定不同的间距。

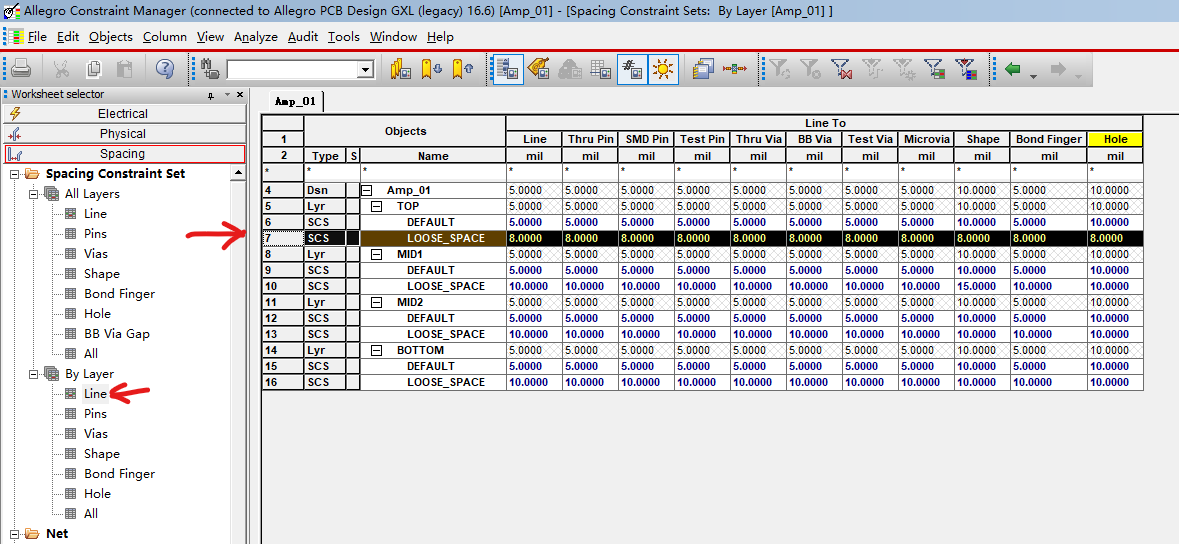

比如,要让电源层(Mid1)中VCC和GND的Shape和其他物体间距设定为15mil,我们先在Spacing Constraint Set中选择By Layer->Shape,编辑Loose_Space,将Shape to ...所有间距改成15mil,如图:

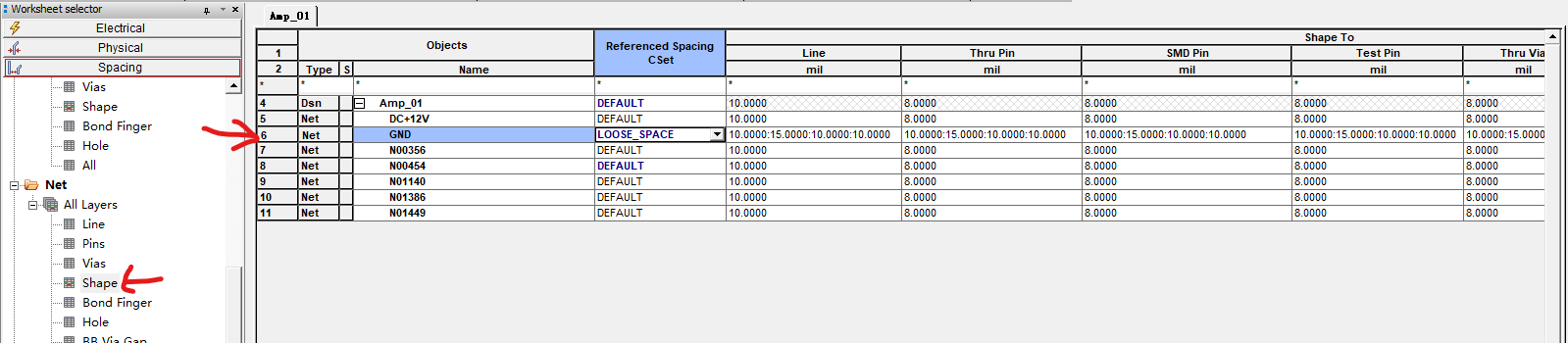

然后在Net选项卡里面,把GND网络需要使用的SCS改成Loose_Space,如图:

将表格列宽度显示展宽,看到Shape to ...都变成了10:15:10:10,符合Loose_Space的设定。

相似地,要完成表层信号线(Line)和GND的Shape间距设定为8mil,先设定SCS中的规则,如图:

然后进行规则选择:

注意到规则选择可以是批量更改的,Ctrl+鼠标左键可以进行复选,Shift+鼠标左键可以进行批量选择。然后进行Edit->Change就可以批量更改。这样表层的信号网络的Line to...间距就变成了8mil.

Cadence套件:Capture + Allegro应用笔记的更多相关文章

- Cadence ORCAD CAPTURE元件库介绍

Cadence ORCAD CAPTURE元件库介绍 来源:Cadence 作者:ORCAD 发布时间:2007-07-08 发表评论 Cadence OrCAD Capture 具有快捷.通用的 ...

- Unable to open ...\tools\capture\allegro.cfg for reading

采用Capture CIS 当生成网表.误: Unable to open ...\tools\capture\allegro.cfg for reading. Please correct the ...

- Cadence原理图与Allegro交互

1:激活orCAD与Allegro的交互程序 打开原理图,Options->Preference在Miscellaneous里勾选 2:打开用到的工程 原理图,还有Allegro PCB Des ...

- 关闭Cadence Orcad Capture CIS原理图弹出startpage页面的方法

打开原理图工具 Orcad Capture CIS 时,总是会弹出startpage 页面,有时候感觉这个东西挺碍事的,还是关了感觉好.解决方法如下:(1) View---Toolbar----Com ...

- cadence学习二----->Allegro基本概念

Class与Subclass 同一根线在不同的Subclass里的含义不一样,下面介绍常用Class和Subclass的含义 1.Etch 包括TOP和BOTTOM,用于走线和覆铜 2.Package ...

- allegro使用汇总 [转贴]

1.如何在allegro中取消花焊盘(十字焊盘) set up->design parameter ->shape->edit global dynamic shape parame ...

- 每天进步一点点------Allegro PCB

Allegro PCB 1.如何在allegro中取消花焊盘(十字焊盘) set up->design parameter ->shape->edit global dynamic ...

- 使用Ultra Librarian将bxl文件转为OrCAD Capture CIS可识别的库文件(OLB)

操作系统:Windows 10 x64 工具1:Ultra Librarian 8.3.89 工具2:OrCAD Capture CIS 16.6-S062 (v16-6-112FF) 关于Ultra ...

- Cadence技巧01:利用Excel速新建原理图元件库

Cadence技巧01:利用Excel速新建原理图元件库 听语音 | 浏览:1698 | 更新:2015-07-02 09:41 | 标签:excel 1 2 3 4 5 6 7 分步阅读 一键约师傅 ...

随机推荐

- leetcode 0216

目录 ✅ 893. 特殊等价字符串组 描述 解答 cpp py ✅ 811. 子域名访问计数 描述 解答 cpp py ✅ 509. 斐波那契数 描述 解答 cpp py ✅ 521. 最长特殊序列 ...

- component:(resolve) => require

resolve => require(['../pages/home.vue'], resolve)这种写法是异步模块获取,打包的时候每次访问这个路由的时候会单调单个文件,按需加载,不过这种写法 ...

- 多项式输出 (0)<P2009_1>

多项式输出 (poly.pas/c/cpp) [问题描述] 一元n次多项式可用如下的表达式表示: 其中,称为i次项,ai称为i次项的系数.给出一个一元多项式各项的次数和系数,请按照如下规定的格式要求输 ...

- vim功能之替换和查找

vim有着强大的替换和查找功能,若能进行熟练的运用,可以让工作效率得到一个很大程度的提高. 替换 语法:[addr]s/源字符串/目的字符串/[option] [addr]表示检索范围,如: &quo ...

- linear-gradient()的用法

linear-gradient() 函数用于创建一个线性渐变的 "图像" 它的语法是 background: linear-gradient(direction, color-st ...

- windows下 DEV-C++无法连接到pthread.h的解决办法

参考的这个博文,原博文有图片:http://lslin.iteye.com/blog/776325 (我只是为了方便写.copy一遍) dev-C++编写C/C++程序时,非常方便轻巧,但是今天学习多 ...

- K8s / Kubernetes 从入门到入门

Kubernetes介绍 1.背景介绍 云计算飞速发展 - IaaS - PaaS - SaaS Docker技术突飞猛进 - 一次构建,到处运行 - 容器的快速轻量 - 完整的生态环境 2.什么是k ...

- SpringBoot之日志记录-专题四

SpringBoot之日志记录-专题四 六.日志管理 6.1使用log4j记录日志 6.1.2新建log4j配置文件 文件名称log4j.properties #log4j.rootLogger=CO ...

- electron-edge-js 环境搭建

确保nodejs环境 为 10.X (因为edge的编译需要node对应版本的支持,太新的node不包含对应edge的编译) 1.创建工程2.使用npm init初始化程序信息3.使用npm ins ...

- spring mvc web应用启动时就执行特定处理(线程启动)

package com.sdt.platform.index.controller; import java.net.URL; import java.util.List; import java.u ...