基于FPGA的三段式状态机

状态机分类:

通常, 状态机的状态数量有限, 称为有限状态机(FSM) 。由于状态机所有触发器的时钟由同一脉冲边沿触发, 故也称之为同步状态机。 根据状态机的输出信号是否与电路的输入有关分为 Mealy 型状态机和 Moore 型状态机。

Mealy 型状态机:

电路的输出信号不仅与电路当前状态有关, 还与电路的输入有关。

Moore 型状态机:

电路的输出仅仅与各触发器的状态, 不受电路输入信号影响或无输入。

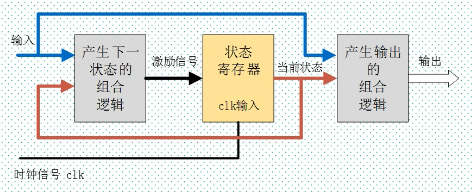

三段式状态机的一般结构:

1)利用参数定义语句 parameter 描述状态机各个状态名称, 即状态编码。一般采用独热码。

2)用时序always模块,格式化描述次态寄存器(下一个状态的寄存器)迁移到现态寄存器。

3)用组合逻辑always模块,描述状态转移条件判断或者状态转移规律。

4)同步时序always模块,格式化描述各个状态的输出。

实现代码:

module test(

input clk,

input rst_n,

output reg out

); //reg define

reg q; //第一步,状态声明和状态编码

reg [:] current_state;

reg [:] next_state;

parameter [:] S0='b0000;

parameter [:] S1='b0010;

parameter [:] S2='b0100;

parameter [:] S3='b1000; //第二部,时序逻辑: 描述状态转换,格式固定

always@(posedge clk)

begin

if(!rst_n)

current_state <= ;

else

current_state <= next_state;

end //第三部,组合逻辑: 描述状态转移条件,即只考虑状态之间的跳转,也就是说各个状态机之间跳转关系。

always @ (current_state or .... ) //电平触发,

begin

next_state = x; //要初始化,使得系统复位后能进入正确的状态

case(current_state)

S0: if(...)

next_state = S1; //阻塞赋值

else

......

S1: if(...)

next_state = S2; //阻塞赋值

else

......

.

.

.

default : .....

endcase

end //第四部,用时序always块输出逻辑: 让输出 out, 经过寄存器 q 锁存后输出, 消除毛刺

always@(posedge clk)

begin

if(!rst_n)

out<='b0;

else

begin

case(current_state)

S0:

out<='b0;

S1:

out<='b1;

.

.

.

default : ....

endcase

end

end

assign q = ou; //让输出 out, 经过寄存器 q 锁存后输出, 消除毛刺

endmodule

基于FPGA的三段式状态机的更多相关文章

- FPGA三段式状态机的思维陷阱

用三段式描述状态机的好处,国内外各位大牛都已经说的很多了,大致可归为以下三点: 1.将组合逻辑和时序逻辑分开,利于综合器分析优化和程序维护; 2.更符合设计的思维习惯; 3.代码少,比一段式状态机更简 ...

- 简单三段式状态机实验2-LCD12864

此实验是在“基于I2C EPPRPM(AT24C02B) + LCD12864实验”基础上,把LCD模块里的一段式状态机改成三段式,I2C EPPROM模块暂时未改出来,一步一步来吧,改完后代码下载到 ...

- 简单三段式状态机实验1-SOS

一直想从一段式状态机切换到三段式状态机,从书上和网上不断搜寻三段式案例及方法,感觉很简单,就想拿之前做过的实验把一段式改成三段式,可是写起来并非那么简单,很棘手,改完后也没有成功,尤其状态机里面的计数 ...

- Verilog笔记.三段式状态机

之前都是用的一段式状态机,逻辑与输出混在一起,复杂点的就比较吃力了. 所以就开始着手三段式状态机. 组合逻辑与时序逻辑分开,这样就能简单许多了. 但是两者在思考方式上也有着很大的区别. 三段式,分作: ...

- 10010序列检测器的三段式状态机实现(verilog)

序列检测器是时序数字电路设计中经典的教学范例,夏宇闻的<verilog数字系统设计教程>一书中有这个例子,用verilog设计一个“10010”序列的检测器.看完后我觉得F和G两个状态多余 ...

- 三段式状态机 [CPLD/FPGA]

状态机的组成其实比较简单,要素大致有三个:输入,输出,还有状态. 状态机描述时关键是要描述清楚前面提高的几个状态机的要素,即如何进行状态转移:每个状态的输出是什么:状态转移是否和输入条件相关等. 有人 ...

- Verilog三段式状态机描述

时序电路的状态是一个状态变量集合,这些状态变量在任意时刻的值都包含了为确定电路的未来行为而必需考虑的所有历史信息. 状态机采用VerilogHDL语言编码,建议分为三个always段完成. 三段式建模 ...

- verilog 三段式状态机的技巧

三段式代码多,但是有时钟同步,延时少,组合逻辑跟时序逻辑分开并行出错少. (1)同步状态转移 (2)当前状态判断接下来的状态 (3)动作输出 如果程序复杂可以不止三个always .always ...

- (原创)Verilog三段式状态机

下面以上图一个简单的FSM说明三段式Verilog状态机范式: `timescale 1ns / 1ps module FSM( clk,rst_n, in1,in2, out1,out2, CS,N ...

随机推荐

- 《运筹学基础及应用》习题1.1(b),1.1(c),1.2(a)

用图解法求解下列线性规划问题,并指出问题具有惟一最优解,无穷多最优解,无界解还是无可行解. 习题1.1(b):$\max z=3x_1+2x_2$$$s.t\begin{cases} 2x_1+x_ ...

- ckeditor深入挖掘吃透

- StartDT_AI_Lab | 开启“数据+算法”定义的新世界

继「数据中台技术汇」栏目推出以来,获得了不少技术极客的喜爱.作为AI驱动的数据中台创导者,深度关注核心算法技术的自研创新.融合探索,故推出全新AI算法栏目「StartDT_AI_Lab」,主要介绍算法 ...

- Euler characteristic

Euler characteristic Euler定理 顶点(v),棱数(edge)(e),面(J) 尽管我们有四个不同的四面体,但是如果我们将顶点数\((v)\)减去棱数\((e)\)再加上四面体 ...

- vue项目中net::ERR_CONNECTION_TIMED_OUT错误

我出错的原因时network地址与我本机ip地址不一致 Network: http://192.168.13.30:8080/ 处理方法: 在vue项目中新建一个vue.config.js文件 配置上 ...

- [LC] 392. Is Subsequence

Given a string s and a string t, check if s is subsequence of t. You may assume that there is only l ...

- proxmox新版本使用了lxc容器,导致以前的vzlist命令无法使用,于是自己写了一个脚本来获取所有半虚拟化主机的信息状态

#!/usr/bin/env python #encoding:utf-8 # desc:用来描述各个主机信息 import os #CTID NPROC STATUS IP_ADDR HOSTNAM ...

- 吴裕雄--天生自然 R语言开发学习:图形初阶

# ----------------------------------------------------# # R in Action (2nd ed): Chapter 3 # # Gettin ...

- python二叉树及叶节点获取 (面试题)

才疏学浅,智商不够,花了一晚上看了二叉树.记录一下: 1.二叉树的遍历 前序遍历:根节点->左子树->右子树 中序遍历:左子树->根节点->右子树 后序遍历:左子树->右 ...

- UML 类图介绍

UML 类图介绍 一. UML 简介 UML ( Unified Modeling Language )即统一建模语言,是 OMG ( Object Management Group )发表的图标式软 ...