[转载]Vivado轻松实现IP封装

Vivado轻松实现IP封装

1、新建一个测试工程

工程化的设计方法是离不开工程的,第一步往往都是新建工程,后面我会学习去工程化的开发方法,可能会更加高效。

2、利用向导完成IP封装

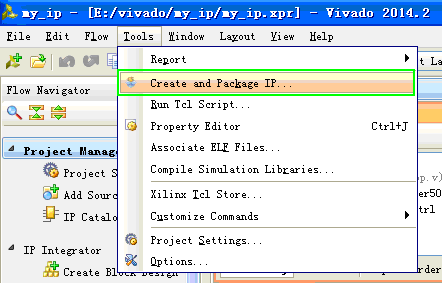

2.1、启动IP向导

方法为:ToolsàCreate and Package IP…,如图1所示。

图1 创建或者打包IP

点击Create and Package IP…命令,弹出向导,如图2所示。

图2 创建和封装IP向导

直接NEXT,进入下一界面,如图3所示。选择操作类型,我们这里不是新建IP,也不是要打包当前工程,而是要把runled_src文件夹下封装成一个IP,所以选择第2项。NEXT。

图3 选择操作类型为封装特定目录

接下来一步要注意了,选择你要打包的资源所在的文件夹,我这里是把要打包的3个文件放在了my_ip/runled_src下面,所以选择了这个路径,如图4所示。

图4 待打包资源所在文件夹

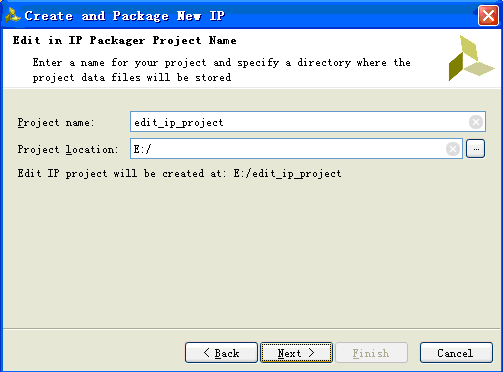

接下来,向导提示需要为IP工程制定一个名字和存储地址,如图5所示。这里采用默认名称即可,这个工程是临时的,IP封装完之后就会消失,再次编辑IP时才会再重新建立。

图5 临时工程名称、存储路径

NEXT,接下来就是最后一步了,是一些提示信息,大家可以自己看一下。点击Finish结束向导。

图6 summary

2.2、IP参数设置

注意,这里已经进入了edit_ip_project工程,是为打包IP核新建的那个工程,我们在上面指定了名称和路径(见图5).

对打包后的IP进行一些参数配置,如供应商,分类(默认是BaseIP,使用时要到该分类下查找我们封装的IP)等信息,这里不一一详述了,需要时,自行修改即可。

图7 IP参数设置

下一步:不做属性上的修改,直接进入最后一步(单击Review and Package),点击图8中的Package IP按钮,开始打包。

图8 开始打包

打包完成后,edit_ip_project工程会自动关闭,返回我们建立的测试工程。

3、查看IP封装结果

在Flow Navigator子窗体下找到Project Manager à IP Catalog,单击IP Catalog,右侧会弹出IP Catalog子窗体,将BaseIP目录展开,发现runled_top_v1_0已经成功导入。

到这里,封装已经完成了,本文要叙述的主题也已经完毕。

------------------------------------------------------分割线---------------------------------------------------------------

但由于是第一次使用,不太放心,所以测试一下,接下爱来各小节是测试用的,不想看的可以直接略过。

4、测试

建立一个Block Design,将runled_top_v1_0添加进去,添加输入输出端口,最终结果如图9所示。

图9 Block Design

5、添加约束、综合、实现、生成Bitstream

约束文件:

#In the following the XDC constraint is matched to the origanal UCF constraint, XDC above, UCF below # Commented

set_property PACKAGE_PIN Y9 [get_ports {iClk}]

set_property IOSTANDARD LVCMOS33 [get_ports {iClk}]

#NET GCLK LOC = Y9 | IOSTANDARD=LVCMOS33; # "GCLK"

# Bank 33, Vcco = 3.3V

#set_property IOSTANDARD LVCMOS33 [get_ports -filter { IOBANK == 33 } ]

set_property PACKAGE_PIN T22 [get_ports {oLed[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[0]}]

#NET LD0 LOC = T22 | IOSTANDARD=LVCMOS33; # "LD0"

set_property PACKAGE_PIN T21 [get_ports {oLed[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[1]}]

#NET LD1 LOC = T21 | IOSTANDARD=LVCMOS33; # "LD1"

set_property PACKAGE_PIN U22 [get_ports {oLed[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[2]}]

#NET LD2 LOC = U22 | IOSTANDARD=LVCMOS33; # "LD2"

set_property PACKAGE_PIN U21 [get_ports {oLed[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[3]}]

#NET LD3 LOC = U21 | IOSTANDARD=LVCMOS33; # "LD3"

set_property PACKAGE_PIN V22 [get_ports {oLed[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[4]}]

#NET LD4 LOC = V22 | IOSTANDARD=LVCMOS33; # "LD4"

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[5]}]

set_property PACKAGE_PIN W22 [get_ports {oLed[5]}]

#NET LD5 LOC = W22 | IOSTANDARD=LVCMOS33; # "LD5"

set_property PACKAGE_PIN U19 [get_ports {oLed[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[6]}]

#NET LD6 LOC = U19 | IOSTANDARD=LVCMOS33; # "LD6"

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[7]}]

set_property PACKAGE_PIN U14 [get_ports {oLed[7]}]

#NET LD7 LOC = U14 | IOSTANDARD=LVCMOS33; # "LD7"

# Bank 34, Vcco = Vadj

#set_property IOSTANDARD LVCMOS18 [get_ports -filter { IOBANK == 34 } ]

set_property IOSTANDARD LVCMOS18 [get_ports {iRst_n}]

set_property PACKAGE_PIN P16 [get_ports {iRst_n}]

#NET BTNC LOC = P16 | IOSTANDARD=LVCMOS18; # "BTNC"

生成Bitstream以便进行板级测试。

6、测试

利用Vivado内置的Hardware Manager向导将Bitstream烧写进FPGA,流水灯顺利出现,OK!

版权声明:

本文由博主“cuter”发布。欢迎转载,但不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和版权声明。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

博客官方地址:

ChinaAET:http://blog.chinaaet.com/cuter521

EDN China: http://bbs.ednchina.com/BLOG_cuter521_356737.HTM

[转载]Vivado轻松实现IP封装的更多相关文章

- Vivado使用技巧:封装自己设计的IP核

概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原理图设计的方式,只需要在其中调用设计好的IP核连线.IP核一部分来自于Xilinx ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- 基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer) 下面是使用MATLAB生成正弦波.三角波.方波的代码,直接使用即可. t=:*pi/^:*pi y=0.5*sin ...

- vivado自定IP例化的问题,怎么生成VHDL的例化

在tools 下面选中project settings.然后选targat language为VHDL .这样就会生成一个以VHDL语言为模板的ip. 转载:https://zhidao.baidu. ...

- ZYNQ笔记(7):AXI从口自定义IP封装

使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用.本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA ...

- ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断

软件的定时中断很难控制精准触发沿的位置,可以通过 PL-PS 的中断完成精准的定时中断.PL 的中断通过 Verilog 代码产生,这样紧密结合 PS-PL 的处理,发挥各自的优势. 一.PL 侧定时 ...

- JavaScript面向对象轻松入门之封装(demo by ES5、ES6、TypeScript)

本章默认大家已经看过作者的前一篇文章 <JavaScript面向对象轻松入门之抽象> 为什么要封装? 封装(Encapsulation)就是把对象的内部属性和方法隐藏起来,外部代码访问该对 ...

- 【转载】 禁止国外IP访问你的网站

在网站的运维过程中,我们通过网站记录的IP列表记录有时候会发现很多国外的IP的访问,如美国的IP等,而很多的服务器攻击行为的发起点很有可能在国外,此时为了服务器安全的考虑,我们可以考虑禁止国外IP访问 ...

随机推荐

- 在 CentOS 7.x / Fedora 21 上面体验 PHP 7.0

编译自:http://linoxide.com/linux-how-to/install-php-7-centos-7-fedora-21/作者: Aun Raza原创:LCTT https://li ...

- Less函数说明

索引 escape(@string); // 通过 URL-encoding 编码字符串 e(@string); // 对字符串转义 %(@string, values...); // 格式化字符串 ...

- android驱动开发前的准备(五)

搭建S3C6410开发板的测试环境 首先安装串口调试工具 第一步:检测当前系统是否支持USB转串口 # lsmod | grep usbserial 第二步:安装minicom # apt-get i ...

- 浅谈五大Python Web框架

转载:http://feilong.me/2011/01/talk-about-Python-web-framework 说到Web Framework,Ruby的世界Rails一统江湖,而Pytho ...

- dependency of static library

一直以来都有一个误区,认为静态库就一定是不含任何依赖的,动态库是含的.这个印象是因为在我们程序中,包含静态库的地方,往往Build好之后直接就可以用,而含DLL的地方,则需要在build好之后的EXE ...

- 第一篇(C#中?与??)

不聊闲话,上干货~!(新手初上路,大牛莫喷,谢谢!) 先说?? 在C#中有个三元运算符 X= A==null?B:A 其中A为bool型.当A为空时,X的值为B;当A不为空时,X的值为A. 现在有个 ...

- Linux运维入门到高级全套常用要点

Linux运维入门到高级全套常用要点 目 录 1. Linux 入门篇................................................................. ...

- bootstrap学习

1. bootstrap使用了less作为预编译器,他是结构清晰层次分明的css页面构建样式,即使你不喜欢bootstrap的样式,你仍然可以借鉴bootstrap编写css的这种方式 2.boots ...

- Python之路,day9-Python基础

回顾:抽象方法@staticmethod 不能访问类的任何属性@classmethod 类方法 只能访问公有属性@property 属性方法 , 把一个方法变成一个静态属性def sayhi() pa ...

- linux下查看系统信息

lspci: 这个工具用来查看所有连接到pci总线上的所有设备信息. 如果有些系统没有lspci,安装后即可使用,有些老死的版本中需要root权限才可使用. 一些用法: lspci 列出所有 ...