Vivado设计二:zynq的PS访问PL中的自带IP核(基于zybo)

1.建立工程

首先和Vivado设计一中一样,先建立工程(这部分就忽略了)

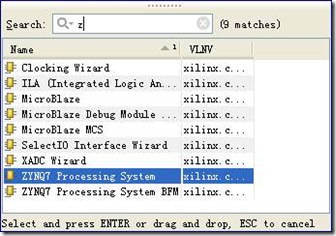

2.create block design

同样,Add IP

同样,也添加配置文件,这些都和设计一是一样的,没什么区别。

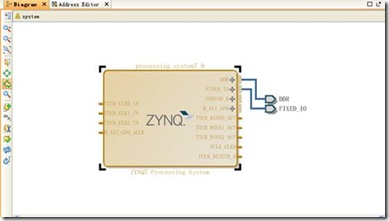

双击,ZYNQ7 Processing System

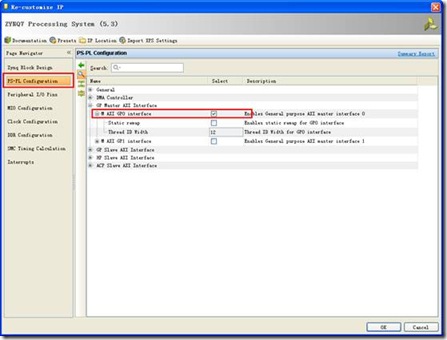

下面的就和设计一中有一些不一样了:

选择PS-PL Configuration,Enable M_AXI_GP0 interface

选择General , Enable Clock Resets 并且选择 FCLK_RESET0_N ,如下:

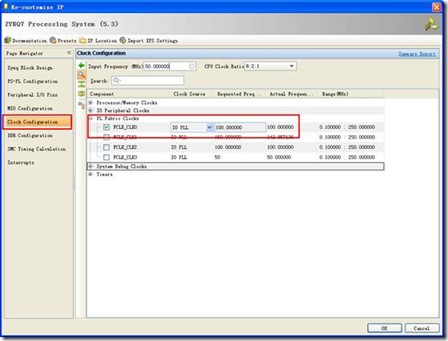

选择Clock Configuration,在PL Fabric Clocks 中 选择 FCLK_CLK0

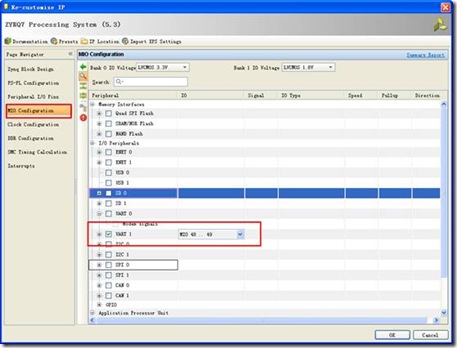

在MIO Configuration中只留下UART1,其他的如ENET0等都不选(这里和设计一一样)

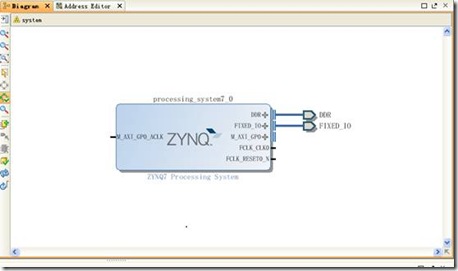

点击ok:

好,现在到我们比较重要的地方了,添加GPIO的IP。点击添加IP按钮

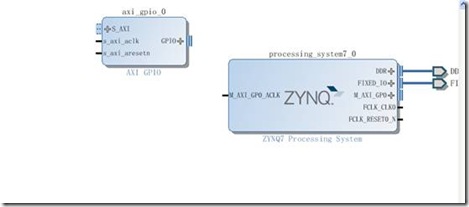

双击添加AXI GPIO后:

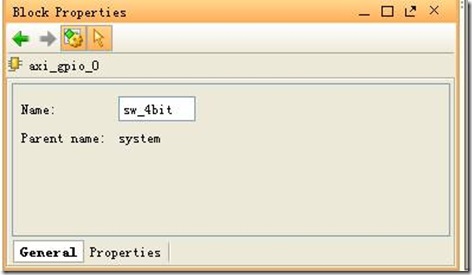

右键 AXI GPIO,选择Block Properties,修改名称

然后双击AXI GPIO,勾上 All Input ,width选择为4

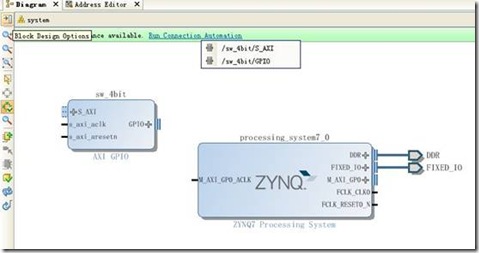

点击ok后,点击Run Connection Automation,选择第一个/sw_4bit/S_AXI

出现

点击ok,自动连接好了:

在添加一个AXI GPIO,过程是一样的,命名为button_4bit

然后设置为all input ,width为4位

再自动连接Run Connection Automation,当然是可以手动拉线的,这里我自动连接了。

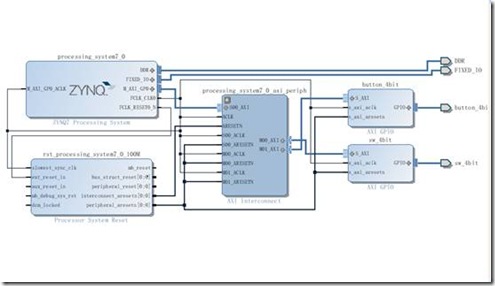

当然,为了能清楚的看到整个系统,我拖动了连接好的几个模块,如下:很清晰:

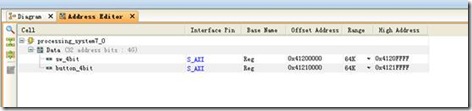

在Address Editor可以看到:

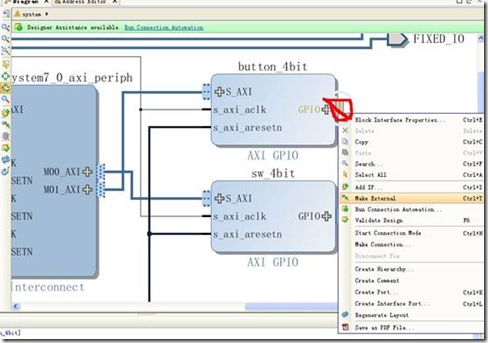

接下来我们需要把PL中的AXI GPIO的GPIO连接到PL的外部IO引脚(zynq的PL的IO口)

选择Make External,并修改名称

整体就是:

选择Tools -> Validate Design,使设计生效,没有error

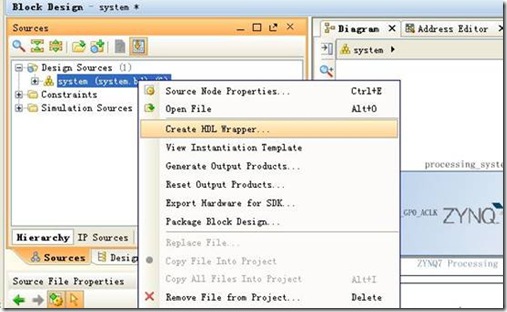

右键system.bd, 选择Create HDL Wrapper

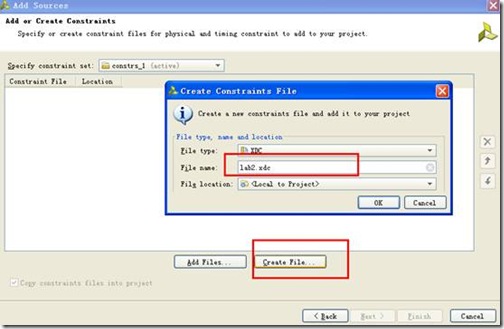

下面添加约束文件,vivado的约束文件的是xdc文件而不是ucf文件

Next,我们create file

接下来肯定是要编写xdc文件了,如下:

set_property PACKAGE_PIN G15 [get_ports {sw_4bit_tri_i[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw_4bit_tri_i[0]}]

set_property PACKAGE_PIN P15 [get_ports {sw_4bit_tri_i[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw_4bit_tri_i[1]}]

set_property PACKAGE_PIN W13 [get_ports {sw_4bit_tri_i[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw_4bit_tri_i[2]}]

set_property PACKAGE_PIN T16 [get_ports {sw_4bit_tri_i[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw_4bit_tri_i[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {button_4bit_tri_i[3]}]

set_property PACKAGE_PIN Y16 [get_ports {button_4bit_tri_i[3]}]

set_property PACKAGE_PIN V16 [get_ports {button_4bit_tri_i[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {button_4bit_tri_i[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {button_4bit_tri_i[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {button_4bit_tri_i[0]}]

set_property PACKAGE_PIN P16 [get_ports {button_4bit_tri_i[1]}]

set_property PACKAGE_PIN R18 [get_ports {button_4bit_tri_i[0]}]

综合

综合完毕,下面几步是可以不做的,但是检查一下也无妨,可以直接跳到产生output products

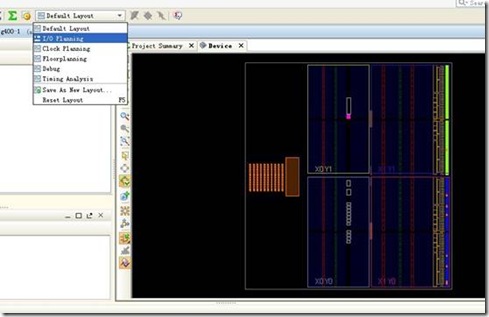

然后选择I/O Planning

如果不是如下的需要修改成如下的:我的没有做任何的修改

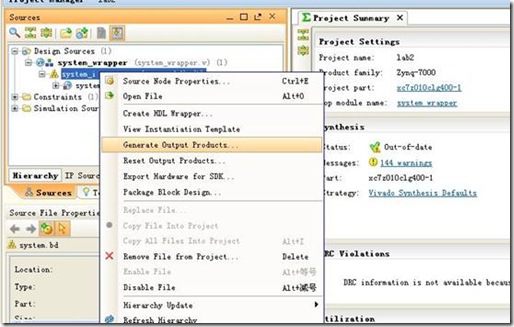

关闭,回到主界面:产生output products

点击Generate

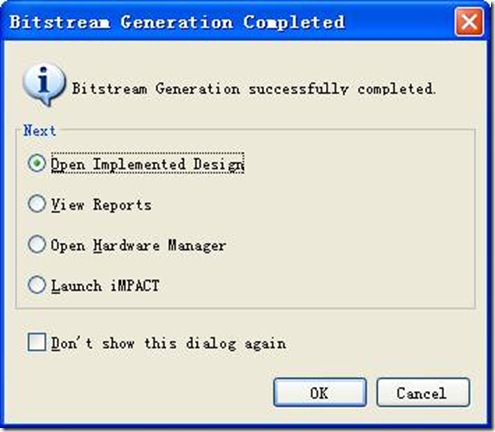

然后就是产生bit流文件了。Open Implemented Design

接下来就是熟悉的导入到SDK了

突然出现错误:

Failed to run "export_hardware" for "system". This diagram is not currently open. "export_hardware" works only for active block diagrams.

提示是没有打开block diagrams.,那就打开呗,双击

这样继续导入到SDK,这样就很欢快的可以了。Go on

然后和设计不一样的是这里我们新建的不是mem_test(之前是利用模板),我们这里使用的空工程,然后我们自己写一个应用程序。

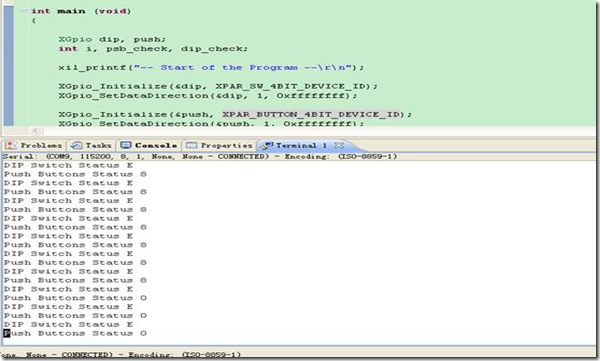

应用程序如下:

#include "xparameters.h"

#include "xgpio.h"

#include "xutil.h" //==================================================== int main (void)

{ XGpio dip, push;

int i, psb_check, dip_check; xil_printf("-- Start of the Program --\r\n"); XGpio_Initialize(&dip, XPAR_SW_4BIT_DEVICE_ID);

XGpio_SetDataDirection(&dip, 1, 0xffffffff); XGpio_Initialize(&push, XPAR_BUTTON_4BIT_DEVICE_ID);

XGpio_SetDataDirection(&push, 1, 0xffffffff); while (1)

{

psb_check = XGpio_DiscreteRead(&push, 1);

xil_printf("Push Buttons Status %x\r\n", psb_check);

dip_check = XGpio_DiscreteRead(&dip, 1);

xil_printf("DIP Switch Status %x\r\n", dip_check); for (i=0; i<9999999; i++);

} }

至于应用程序中的怎么理解我在之前博客说过了,见:

zynq正确的使用GPIO:http://blog.chinaaet.com/detail/34965

zedboard的GPIO实验:http://blog.chinaaet.com/detail/34982

这里就不啰嗦了。

编译生成elf文件

先下载bit流,在下载elf文件,看到下面的结果!!

这篇博客和之前基于zedboard的ISE的内容是类似

zedboard--zynq使用自带外设IP让ARM PS访问FPGA

http://blog.chinaaet.com/detail/34609

感觉这个用vivado来开发zybo和ISE开发zedboard有点类似,上手还挺快的,不过感觉vivado貌似确实比ISE要快些。下一次肯定就是要添加自定义的IP核了,这个用ISE也实现过的,跑完了再与网友一起分享吧。

-

2016-04-22 16:29:01

@xzy610030 您好!能不能给我发一下

xutil.h文件,谢谢!

- 2015-11-30 11:38:30

***此内容已被管理员屏蔽***

-

2015-10-13 16:30:50

请问你还有没有xutil.h这个文件。能麻烦发个我吗?541984342@qq.com谢谢了

@xzy610030 @uniquewan

我现在没有这个环境了,留个邮箱,我给你发个文档。  匿名用户2015-08-24 16:59:19@uniquewan

匿名用户2015-08-24 16:59:19@uniquewan

我也出现了这种情况,想问下你是怎么解决的?"xutil.h是包含在哪个库里面的啊?-

2015-06-09 16:53:58@uniquewan

我现在没有这个环境了,留个邮箱,我给你发个文档。 -

2015-06-08 18:31:01

你好,我在用zybo板做这个gpio实验室时候,为什么在Include "xutil.h"文件就报错,报错说

no such file or directory。想请你帮忙解答下。

注释掉这个include就可以编译通过,但是上板只是打印Start of the Program ,没有后面的dip的状态显示

转载:http://blog.chinaaet.com/xzy610030/p/35795

Vivado设计二:zynq的PS访问PL中的自带IP核(基于zybo)的更多相关文章

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 通过shell查找访问日志中访问量最大的ip

日志格式: /Sep/::: +] /Sep/::: +] /Sep/::: +] - /Sep/::: +] - /Sep/::: +] /Sep/::: +] - /Sep/::: +] /Sep ...

- Quartus设计FIR滤波器的系数文件格式(适用于FIR II的IP核)

对常用的FIR,我们使用MATLAB的fdatool(或者filterDesigner) 设计滤波器,给定指标,生成系数.为了方便,我们将系数保存到文件,其保存格式比较简介,在此进行说明. 1.FIR ...

- Vivado使用技巧(二):封装自己设计的IP核

由 judyzhong 于 星期五, 09/08/2017 - 14:58 发表 概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原 ...

- Vivado使用技巧:封装自己设计的IP核

概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原理图设计的方式,只需要在其中调用设计好的IP核连线.IP核一部分来自于Xilinx ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- PS与PL协同设计

https://blog.csdn.net/Fei_Yang_YF/article/details/79676172 什么是PS和PL ZYNQ-7000是Xilinx推出的一款全可编程片上系统(Al ...

- 使用axi_datamover完成ZYNQ片内PS与PL间的数据传输

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1.传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送: 2.PL端接口为FIFO接口: PS到PL的数据传输流程: PS到 ...

随机推荐

- RapidXml使用方法

一.写xml 文件 [cpp] view plaincopy #include <iostream> #include "rapidxml/rapidxml.hpp" ...

- Maven项目管理:SpringMVC+Mybatis+Velocity整合笔记

Maven创建项目 略…具体过程可参考用Maven创建第一个web项目 配置Spring MVC 导入Spring MVC 需要的包在pom.xml 文件下加入: 123456789101112 &l ...

- 一键建立zookeeper集群

使用yaml文件的好处,通过service name来进行pod间的服务发现, 集群配置dns. [root@k8s-master ~]# cat zookeeper-cluster.yaml api ...

- [转]在Sql Server中将字符串分割成表格数据示例

本文转自:http://www.lmwlove.com/ac/ID718 比如我们有一个字符串 ) select @appName ='UserID=admin,Account=ABC' 然后我们要以 ...

- DIV强制不换行

一.单个DIV:1.用nobr元素 <html> <head> </head> <body> <div><nobr>不换行不换行 ...

- Bayesian statistics

文件夹 1Bayesian model selection贝叶斯模型选择 1奥卡姆剃刀Occams razor原理 2Computing the marginal likelihood evidenc ...

- Spark Streaming ReceiverTracker架构设计

本节的主要内容: 一.ReceiverTracker的架构设计 二.消息循环系统 三.ReceiverTracker具体实现 Spark Streaming作为Spark Core基础 架构之上的一个 ...

- Java Web----EL(表达式语言)详解

Java Web中的EL(表达式语言)详解 表达式语言(Expression Language)简称EL,它是JSP2.0中引入的一个新内容.通过EL可以简化在JSP开发中对对象的引用,从而规范页面 ...

- Android SDK Manager 更新

Android SDK Manager 更新 解决国内访问Google服务器的困难: 1.启动 Android SDK Manager : 2.打开主界面,依次选择「Tools」.「Options…」 ...

- tornado 多进程模式

https://www.douban.com/note/217901726/ 官方文档的helloworld实例中的启动方法: if __name__ == "__main__": ...