ISE联合modelsim功能仿真和综合后仿真1

本文出自 “李海川” 博客,请务必保留此出处http://lihaichuan.blog.51cto.com/498079/984870

补充:http://wenku.baidu.com/link?url=idbSvNzz2fLSl1WXiEmtIL1amhQTHmtqqQ6g1cp-oU1X3W4wF2Wdu5LSe745rwjCrM-btR44-we9zLCyMf2ofjjAt2d8wcBT7LFyIHF8Tym

ISE联合modelsim功能仿真和综合后仿真1的更多相关文章

- ISE联合modelsim功能仿真和综合后仿真

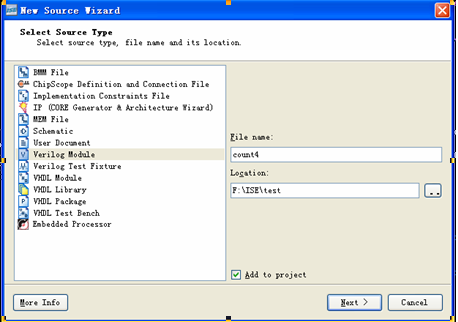

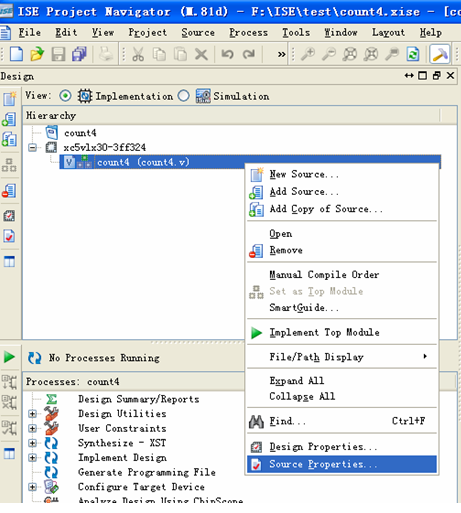

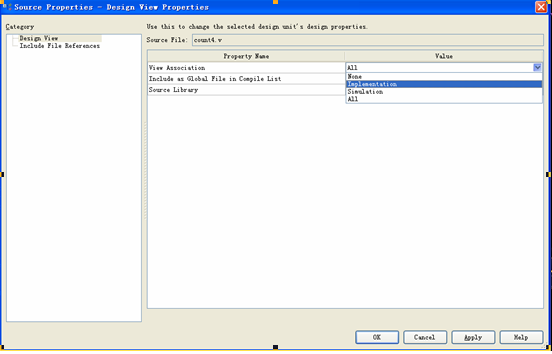

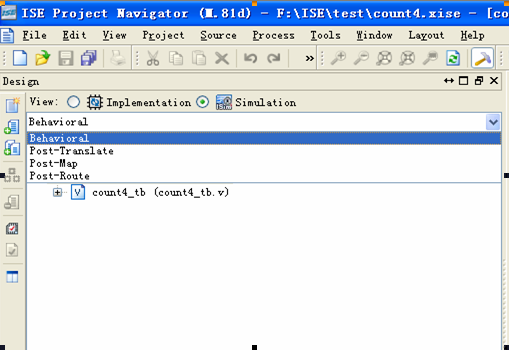

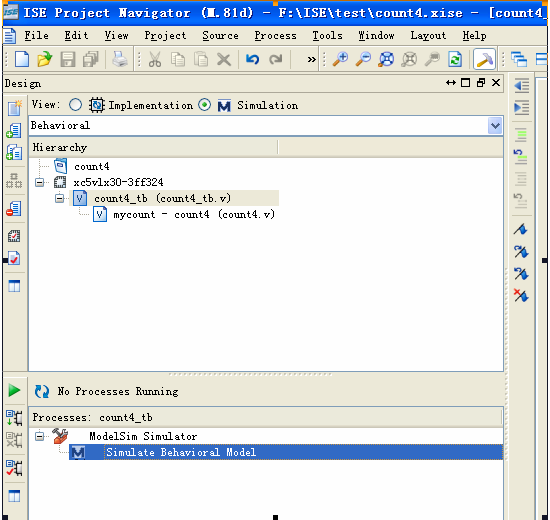

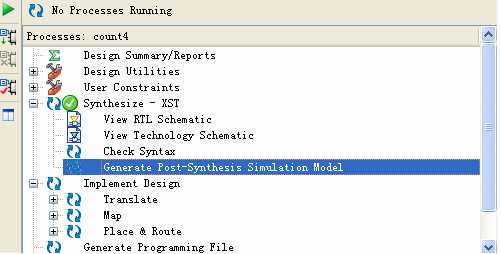

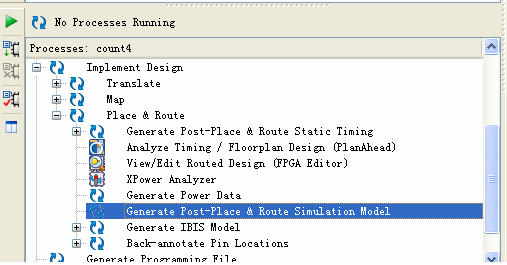

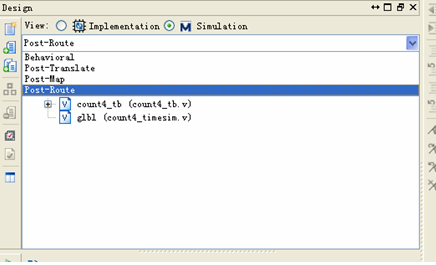

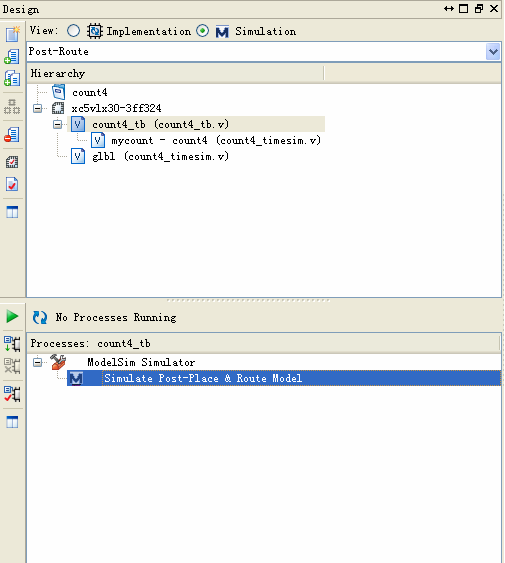

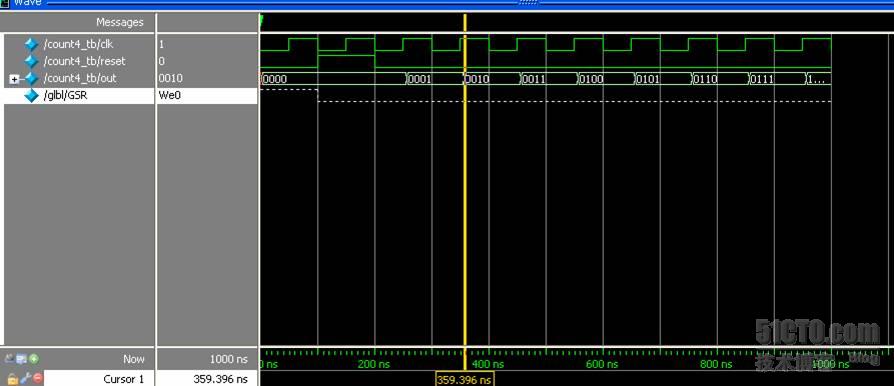

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- 用Modelsim仿真QuartusII综合后网表时库的添加方法(转)

这两天做综合后仿真,发现FPGA器件库又不会加了,无奈上网找方法.说起来不好意思,很早就接触Modelsim这个仿真软件了,可是没有好好琢磨.把这两天找的方法贴出来,再加上自己的理解,以后忘了可以上博 ...

- FPGA功能仿真,门级仿真,后仿真的区别

前言 分清楚各种仿真间的关系,工具采用quartus prime16.0,仿真工具采用modelsim10 ae版:项目:led_display; 流程 1.RTL行为级仿真:也叫功能仿真,这个阶段的 ...

- ISE和Modelsim联合仿真(详细步骤讲解)

ISE和Modelsim联合仿真(转) 地址:http://www.cnblogs.com/feitian629/archive/2013/07/13/3188192.html 相信很多人会遇到过这个 ...

- ISE和Modelsim联合仿真(转)

相信很多人会遇到过这个问题,不知如何让ISE调用Modelsim进行仿真.我也迷糊了不少时间,查查找找,终于弄明白了,所以有了本文,和大家分享一下.我尽量讲得详细点儿,多多上图. 我的环境:Windo ...

- ISE综合后得到的RTL图如何与硬件对应起来,怎么知道每个element的功能

2013-06-23 21:34:03 要知道“我写的这段代码会综合成什么样的电路呢”,就要搞清楚RTL图中每个模块的功能,从而将代码与硬件对应,判断综合后的电路是否与预期的一致.如何做到? 之前查了 ...

- ise和modelsim联合仿真的一些准备

首先要在modelsim中编译xilinx的三个库,分别是unisims库,simprims库,和corelib库,其中unisims库全称为(library of united component ...

- 怎样用modelsim做后仿真

摘要: 怎样用modelsim做后仿(编译工具采用quatus) step1:在qurtus改变编译选项: assignments->EDA tool setting:选择verilog ...

- [原创]Modelsim后仿真

因调试需要,进行后仿真,ISE生成的sim文件和sdf文件 `timescale ns/ ps module lut_dly ( clkout, fpga_clk, config_in ); outp ...

随机推荐

- Fusioncharts的导出图片訪问官网问题

Fusioncharts3.5使用自带的导出功能,须要訪问官网 问题描写叙述:使用fusioncharts自带的exportchart方法来导出图片的时候.要訪问export.api3.fusionc ...

- Python标记去重

预逻辑脚本代码: uniqueList = [] def isDuplicate(inValue): if inValue in uniqueList: return 1 else: uniqueLi ...

- web中的安全编码

个人记录 一.Web安全验证 输入验证 防范跨站脚本XSS攻击 防止SQL注入 图片验证码 二.输入验证 经典的安全法则:永远不要相信用户提交的数据 验证内容: 用户名,密码等格式 验证长度防止数据库 ...

- Java从零开始学九(数组)

一.什么是数组 数组是一组相关数据的集合,一个数组实际上就是一连串的变量,数组按照使用可以分为一维数组.二维数组.多维数组.同一数组中的变量数据类型相同 二.数组的优点 不使用数组定义100个整型变量 ...

- webservice系统学习笔记4-使用工具查看SOAP消息

使用myeclipse的WTP java ee视图里的[web services Explorer]来测试查看webservice传输的SOAP消息 1. 2. 测试getUserByUsername ...

- 类的专有方法(__del__)

# -*- coding: utf-8 -*- #python 27 #xiaodeng #http://www.bubuko.com/infodetail-313791.html #类的专有方法(_ ...

- spring aop的两种写法aspect和advisor

本文转自:https://www.cnblogs.com/leiOOlei/p/3709607.html 首先看个例子,如下 接口代码: package com.lei.demo.aop.schema ...

- nginx的Mainline version、Stable version、Legacy version的版本区别

nginx的Mainline version.Stable version.Legacy version的版本区别 创建时间:2014-01-16 10:30:37最后修改:2014-09-23 20 ...

- flume的memeryChannel中transactionCapacity和sink的batchsize需要注意事项

一. fluem中出现,transactionCapacity查询一下,得出一下这些: 最近在做flume的实时日志收集,用flume默认的配置后,发现不是完全实时的,于是看了一下,原来是memery ...

- elasticsearch5.4体验

Elasticsearch是基于Lucene分布式.实时查询的搜索分析引擎.我目前应用在日志集中化处理上... 01.下载elasticsearch5.4 https://www.elasti ...