FPGA基础学习(8) --内部结构之存储单元

上一篇中提到了SLICEL和SLICEM都可用作ROM,后者还可以作为分布式RAM(Distribute RAM,DRAM)。本篇主要总结的是块状Memory(Block Memory),实际上就是FPGA内部独立于逻辑单元的专用存储器,更像是一种硬核。

1. 基本结构

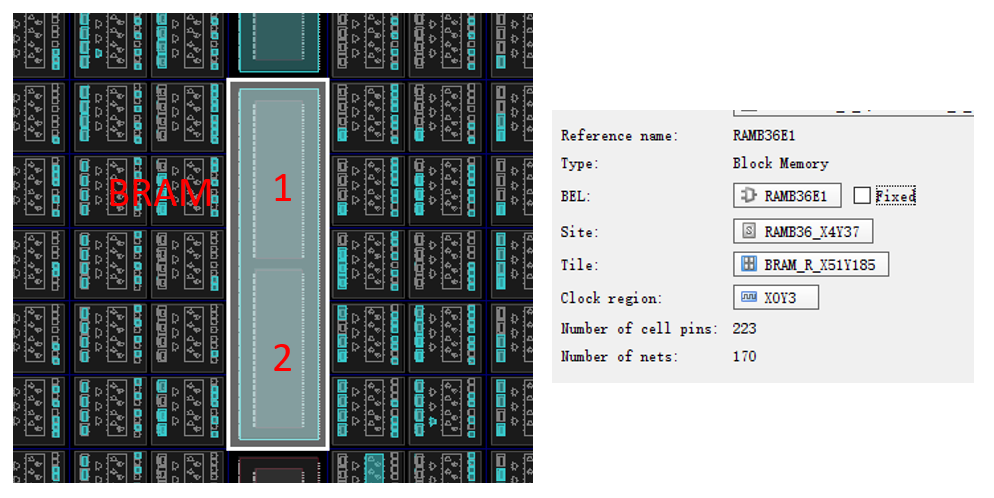

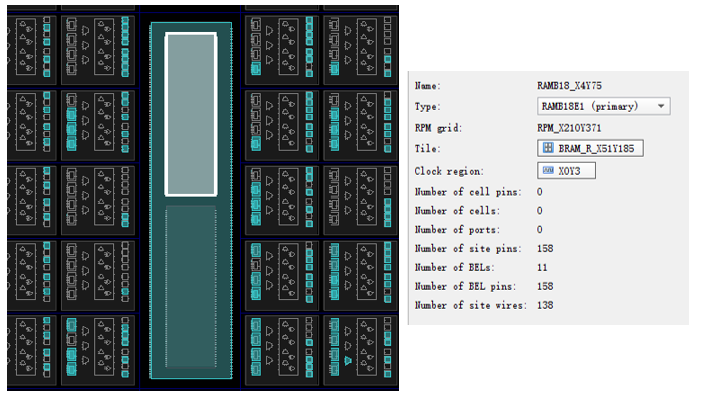

如下图所示,一个Block Memory的大小为36KB(RAMB36E1),由两个独立的18KB BRAM(Block RAM,RAMB18E1)组成。因此一个36K的Block Memory可配置成4中情形:

- 全部用于配置成36KB的BRAM;

- 全部用于配置成36KB的FIFO;

- 配置成18KB的BRAM和18KB的BRAM;

- 配置成18KB的BRAM和18KB的FIFO;

为什么不能配置成两个18KB的FIFO呢?因为一个Block Momery中间有一个叫FIFO Logic的结构,它用于生成FIFO控制信号,包括读/写地址等,由于它只有1个且不能共享,所以最多只能配置一个FIFO。

2. BRAM与DRAM的比较

简单的来说,BRAM就是一块固定存储功能的硬核,而DRAM是由一堆SLICE拼接成,实现存储功能的单元。

尽管BRAM可支持更多功能,但并不表明BRAM在任何场合都具有优势。两者的使用总结如下:

- BRAM一定需要时钟;DRAM可以是纯组合逻辑,即给地址马上出数据(当然上篇说了,为了提高性能,在读出的时候加上触发器更好);

- BRAM有着较大的存储空间;而DRAM实现大的存储空间会消耗很多LUT资源;

较大的存储应用,建议用BRAM;零星的小RAM,一般就用DRAM。但这只是个一般原则,具体的使用得看整个设计中资源的冗余度和性能要求。

3. BRAM的特点

当Block Memory配置成RAM时,有三种工作模式:

- 读优先

- 写优先

- 保持模式

三种模式体现了当对RAM中同一地址同时进行读操作和写操作时的不同。简单的说,当同时对RAM中的同一地址进行读写时,读优先模式将读出该地址内原有的数据,写优先模式将读出当前写入该地址的数据(注意断句,意思是最终会读出的数据是先写入的数据),保持模式则保持之前读出的数据不变。

4. Block Memory的使用

4.1 配置为RAM或ROM

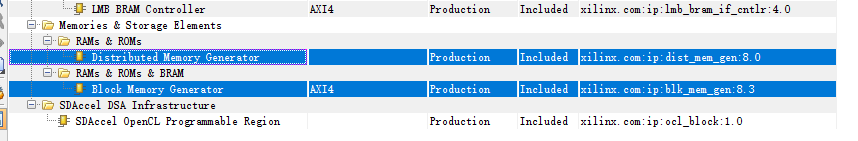

在Vivado的“IP catalog”中搜索“RAM”,会出现如下结果,可以看到想要生成RAM或ROM,可以选择Distributed Memory或Block Memory,即上面提到的分布式和块状存储单元。

选择“Block Memory Generator”,可以看到块存储单元可以用作RAM或ROM,具体配置就不详细展开了。

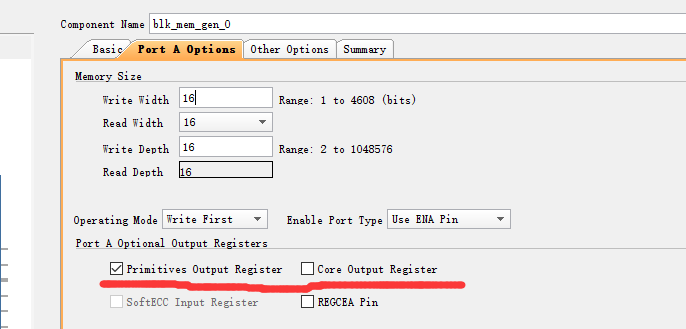

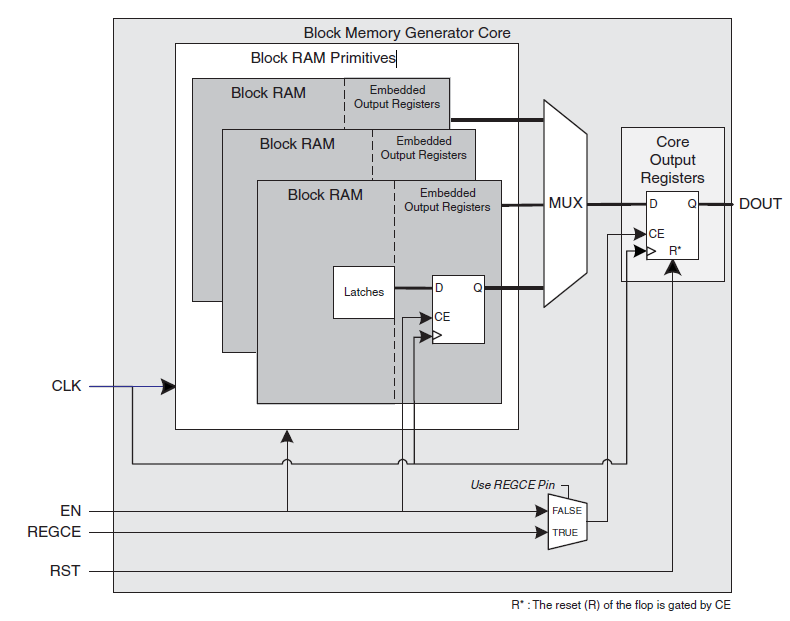

值得一提的是,在“Port A Options”选项卡中,有个Output Registers栏,可以选择Primitive Output Register和Core Output Register。其中前者位于BRAM内部,后者为CLB中的触发器。值得注意的是,在这里这两个触发器只支持同步高有效复位。这两个触发器可大大降低时钟到输出的延迟,在高速设计中,这两个触发器都使用,使用之后读操作的latency会增大为3个时钟周期。

4.2. 配置为FIFO

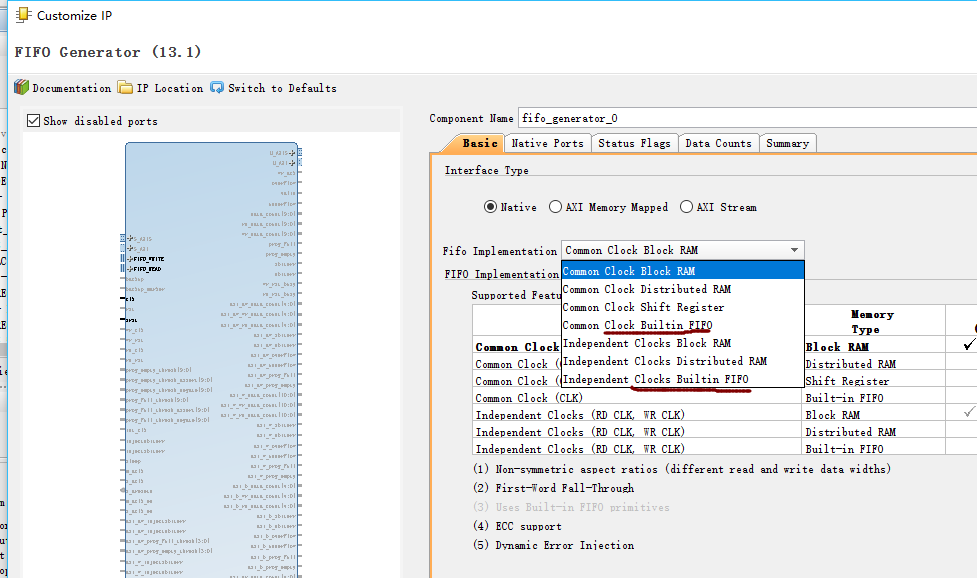

Block Memory中的BRAM还可配置为FIFO(同步或异步),同时提供专用的FIFO Logic用于生成FIFO的控制信号和状态信号。使用专用的FIFO Logic的FIFO称为build-in FIFO。Vivado提供了IP:FIFO Generator,即可以将BRAM配置为build-in FIFO,也可以采用CLB资源生成FIFO控制逻辑,并结合BRAM构成FIFO。

对于7系列FPGA内部未使用的18KB BRAM,Vivado通过Power Gating技术不会对其进行初始化,从而可以有效降低功耗。

参考文献:

- 《Block Memory Generator v8.4》(PG058)

- 《VIVADO从此开始》——高亚军著

FPGA基础学习(8) --内部结构之存储单元的更多相关文章

- FPGA基础学习(7) -- 内部结构之CLB

目录 1. 总览 2. 可配置逻辑单元 2.1 6输入查找表(LUT6) 2.2 选择器(MUX) 2.3 进位链(Carry Chain) 2.4 触发器(Flip-Flop) 参考文献: 一直以来 ...

- FPGA基础学习(9) -- 复位设计

目录 1. 常见问题 2. 常见的复位方式 3. 合理的复位设计 3.1 复位电平 3.2 异步复位同步化 3.3 恰到好处的复位 4. 补充 4.1 所谓的上电初始化 参考文献 一开始接触到FPGA ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA基础学习(5) -- 时序约束(实践篇)

目录 1. 理论回顾 2. 时间裕量 3. 最大延迟和最小延迟 4. 案例分析 参考文献: 距离上一篇有关时序的理论篇已经有一段时间了(可以参考博文FPGA时序约束--理论篇),实际上此段时间,甚至到 ...

- FPGA基础学习(6) -- 原语

目录 1. IBUF和IBUFDS(IO) 2. IDDR(Input/Output Functions) 3. IBUFG和IBUFGDS(IO) 原语,即primitive.不同的厂商,原语不同: ...

- FPGA基础学习(4) -- 时序约束(理论篇)

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- Golang 汇编asm语言基础学习

Golang 汇编asm语言基础学习 一.CPU 基础知识 cpu 内部结构 cpu 内部主要是由寄存器.控制器.运算器和时钟四个部分组成. 寄存器:用来暂时存放指令.数据等对象.它是一个更快的内存. ...

随机推荐

- SqlServer——字符串处理函数

1) ASCII Format:ASCII ( character_expression ) Function:返回表达式最左端字符的ASCII值. eg: select ASCII('abcdef' ...

- 复杂链表的复制(java)

问题描述 时间输入一个复杂链表(每个节点中有节点值,以及两个指针,一个指向下一个节点,另一个特殊指针指向任意一个节点), 返回结果为复制后复杂链表的head.(注意,输出结果中请不要返回参数中的节点引 ...

- Qt程序无法输入中文的问题

问题 在Linux环境下,用Qt编写的程序运行时不能在诸如输入框.文本框中输入中文(不会激活中文输入法). 注意与输入法类型有关(基于iBus或Fcitx) 原因 Qt程序的中文输入支持需要用Qt插件 ...

- 【转】Comprehensive learning path – Data Science in Python

Journey from a Python noob to a Kaggler on Python So, you want to become a data scientist or may be ...

- Part3_lesson2---ARM指令分类学习

1.算术和逻辑指令 mov.mvn.cmp.tst.sub.add.and.bic 2.比较指令 cmp和tst 3.跳转指令 b和bl 4.移位指令 lsl和ror 5.程序状态字访问指令 msr与 ...

- js实现水平伸缩菜单

window.onload=function(){ var aA=document.getElementsByTagName('a'); for(var i=0; i<aA.length; i+ ...

- python str, list,tuple, dir

Python3 字符串 字符串是 Python 中最常用的数据类型.我们可以使用引号('或")来创建字符串. 创建字符串很简单,只要为变量分配一个值即可.例如: var1 = 'Hello ...

- C#事件订阅及触发例子

最典型的事件例子,猫叫了(事件源),老鼠跑了(事件订阅者),惊醒主人(事件订阅者) 源代码: class Program { static void Main(string[] args) { Cat ...

- jenkins持续集成之Global Tool Configuration的配置

Global Tool Configuration的配置过程: 1.点击系统管理2.点击 Global Tool Configuration3.必须配置: jdk git ant maven 1.点击 ...

- Ubuntu16 apt-get更换为阿里源

1.备份系统自带源 mv /etc/apt/sources.list /etc/apt/sources.list.bak 2.修改/etc/apt/sources.list文件 vim /etc/ap ...