【P5】Verilog搭建流水线MIPS-CPU

课下

Thinking_Log

1.为何不允许直接转发功能部件的输出

直接转发会使一些组合逻辑部件增加新的长短不一的操作延迟,不利于计算设置流水线是时钟频率(保证流水线吞吐量?)。

2.jal中将NPC+4/8存入$ra的操作为何需流过全级

不要因为beq指令提前得到结果完成跳转的事情乱了方寸。jal虽然D级即可出NPC地址,但若D级后立即进入W级准备写入,且不说毫无增益,原先还在W级的指令不就被覆盖了嘛!流水线将指令按级传输执行的基本概念都忘掉了!

Technique_Log

1.向量部分选择

可以选择向量的连续几位输出

A[base_expr +: width_expr] //positive offset

B[base_expr -: width_expr] //negative offset

Arr[x -: 2] //意味着取Arr中x x-1这两位

其中base_expr可以是变量,而width_expr必须是常量。

+:表示由base_expr向上增长width_expr位

-: 表示由base_expr向下递减width_expr位

Bug_Log

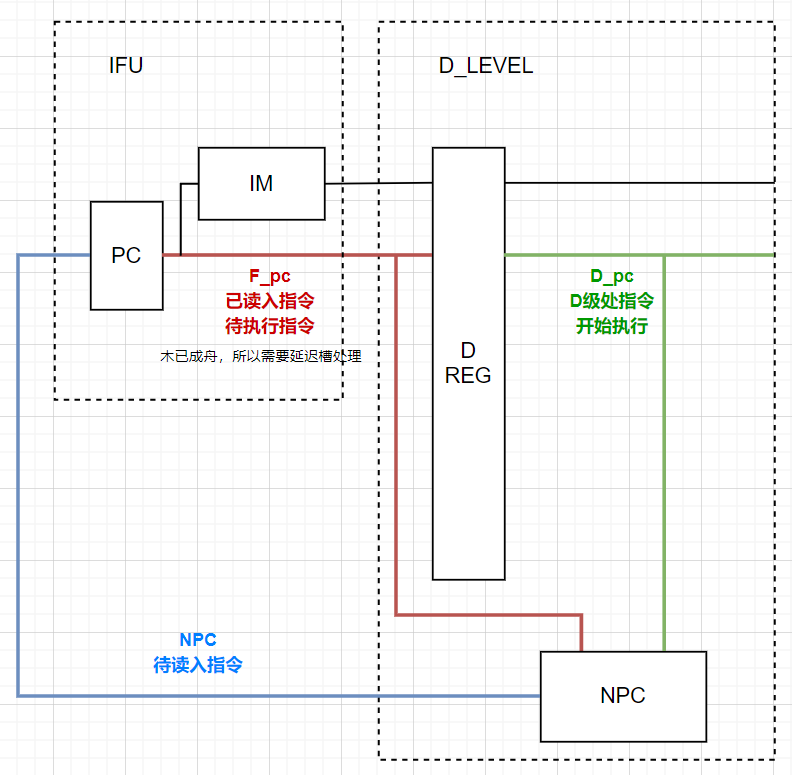

1.NPC信号脱节——F、D寄存器影响

D_pc + 8 并不可以替代 F_pc + 4,在跳转指令时暴露问题

assign NPC = (NPCOp == `NPC_order ) ? PC_F + 4 : //易错,增量是相对于F级的PC而言的;且PC + 8在跳转时无法替代。画图可理解

(NPCOp == `NPC_branch) ? PC_b :

(NPCOp == `NPC_jump ) ? PC_j :

(NPCOp == `NPC_reg ) ? RA :

PC_F + 4 ;

2.相似语句书写变量修改灯下黑

这个错误仅在关于$0的内部转发中显现,十分的隐秘,且粗粗扫一眼,还以为内部转发完全没问题。中测最后一个点WA在这,第12周第1次P5临考前靠同学de出

assign RD1 = (A3 == A1 && RFWr == 1 && A1 != 0) ? WD : grf[A1] ; //D级内部转发

assign RD2 = (A3 == A2 && RFWr == 1 && A2 != 0) ? WD : grf[A2] ; //giao,误写

//上下形式相似,书写时容易忘记修改变量名,例如GRF内部转发第二行 A2 != 0 误抄成A1

3.E级输出的V2信号错误——对T_use的误解

第1次P5课上添加swc计算指令暴露,写DM数据错误

lw $4, 0($0)

sw $4, 0x2000($0)

sw $4, 0x2004($0)

sw $4, 0x2008($0)

sw $4, 0x200c($0)

被转发的数据都是将要写入但还没写入GRF的数据。因此是对错误的GPR[rs] GPR[rt]值进行修正,这两个寄存器值的数据路径分别是

GPR[rs]:D_GRF_RD1 -> E_reg_V1GPR[rt]:D_GRF_RD2 -> E_reg_V2 -> M_reg_V2

当某指令到达某一级,必须使用指定寄存器值时,该级路径上的内容必须正确(接收转发),这也是T_use计算截止的地方。若能达成上述目标(T_use >= T_new),则T_use截止处前的内容无需关心,但这不代表此前转发的值没用。

- T_use = T_new时,代表当前转发修正堪堪在要使用时到来

- T_use > T_new时,代表转发修正在使用前已经到来,此后路径上的内容为正确寄存器值

此前我的设计其实无意间都符合了这些想法。但在E级出现了疏漏。E_reg_V2是从D级流至E的值,若要留到M级,需经过M级、W级转发数据的修正。

我将修正后的寄存器值仅作为ALU的输入,而直接将未修正的数据传到下一级,因而倘若数据在M级得不到修正,便会使用错误的寄存器值。sw指令用到了M_reg_v2(T_use(rt) = 2),使得问题得以暴露。

| time | D | E | M | W |

|---|---|---|---|---|

| 1 | lw $4, 0($0) |

nop |

nop |

nop |

| 2 | sw $4, 0x2000($0) |

lw $4, 0($0) |

nop |

nop |

| 3 | sw $4, 0x2004($0) |

sw $4, 0x2000($0) |

lw $4, 0($0) |

nop |

| 4 | sw $4, 0x2008($0) |

sw $4, 0x2004($0) |

sw $4, 0x2000($0) | lw $4, 0($0) |

| 5 | sw $4, 0x200c($0) |

sw $4, 0x2008($0) |

sw $4, 0x2004($0) | sw $4, 0x2000($0) |

time = 4时,lw指令产生了可转发的数据,便向前转发修正了D、E、M级出GPR[rt]的寄存器值(D级靠内部转发);time = 5时,lw指令完成了寄存器写入,其后D级数据便正确,E、M、W级应为此前经过修正也正确,所以行为正确。然而我将E级处对sw $4, 0x2004($0)的GPR[rt]修正丢失,且到M级时已无法得到修正,因而产生了lw $4, 0($0)生效前的值。

4.Tuse缺省值误判阻塞的错误规避——导致超周期数限制

第3次P5课上添加taddu计算指令暴露,空输出:

...got nothing when we expected @00003f7c: $29 <= 00000108。算是tle吧

对于不需要读寄存器的指令(Tuse不存在)来说,Tuse的缺省值应设为最大值(比如3),否则会和Tuse = 0的指令混合,产生不必要的阻塞从而超周期数。

本人写的时候缺省值设为0,但也并不是没考虑过这种情况。但认为仅加上“是否为合法转发”(M级rt的stall:D_instr[20:16] && (D_instr[20:16] == E_RFA3) && E_RFWr)的判断就能规避,属实疏忽了很多情况。例如

ori $t0, $t0, 0x1234

lw $t0, 0($0)

lw $t0, 0($0)

lw $t0, 0($0)

哎谁又会想道bug出在周期数上呢?当时都绝望死了,只能感谢讨论区hxd。

5.CMP模块信号的流水——适配BGEZAL组合类指令

本身不是bug,但课上再加流水确实很麻烦因而易错。对于选择性link而言,最好将控制信号流水,因为本人使用分布式译码,所以将D级的CMP比较信号流水,每一级去解码使用。

跳转可分为:

- BXXZAL : 无条件link

- BXXZALC: 条件link (conditionally)(mips中的bgezal其实是这一种)

- BXXZALR: link到指定寄存器 (register)

- BXXZALL: 清空延迟槽(likely)

算是对流水有了进一步理解。

【P5】Verilog搭建流水线MIPS-CPU的更多相关文章

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

- 使用Verilog搭建一个单周期CPU

使用Verilog搭建一个单周期CPU 搭建篇 总体结构 其实跟使用logisim搭建CPU基本一致,甚至更简单,因为完全可以照着logisim的电路图来写,各个模块和模块间的连接在logisim中非 ...

- windows10(64位)Anaconda3+Python3.6搭建Tensorflow(cpu版本)及keras

转自:windows10(64位)Anaconda3+Python3.6搭建Tensorflow(cpu版本)及keras 1.本来电脑安装的是anaconda3 5.3.1,但安装的python版本 ...

- 使用logisim搭建单周期CPU与添加指令

使用logisim搭建单周期CPU与添加指令 搭建 总设计 借用高老板的图,我们只需要分别做出PC.NPC.IM.RF.EXT.ALU.DM.Controller模块即可,再按图连线,最后进行控制信号 ...

- 搭建直接通过CPU执行汇编语言的环境

搭建直接通过CPU执行汇编语言环境 我们通过编译写好的汇编语言代码可以生成.bin的机器语言二进制代码.但是这个.bin程序我们该如何运行呢? 这里其实有两个办法: 1: 将其作为一个Windows/ ...

- 手写一个简易的多周期 MIPS CPU

一点前言 多周期 CPU 相比单周期 CPU 以及流水线 CPU 实现来说其实写起来要麻烦那么一些,但是相对于流水线 CPU 和单周期 CPU 而言,多周期 CPU 除了能提升主频之外似乎并没有什么卵 ...

- Unity 渲染流水线 :CPU与GPU合作创造的艺术wfd

前言 对于Unity渲染流程的理解可以帮助我们更好对Unity场景进行性能消耗的分析,进而更好的提升场景渲染的效率,最后提升游戏整体的性能表现 Unity的游戏画面的最终的呈现是由CPU与GPU相互配 ...

- Ubuntu14.04搭建Caffe(仅CPU)

一直以来都没有写博客的习惯,后来发现以前做的工作如果不注意及时整理和记录往往丢失的很快.对我而言这是一篇具有重要意义的文章,好的习惯要持之以恒,以后的日子我会常驻博客园!由于本人水平有限,智商略低,欢 ...

- Jenkins使用六:搭建流水线任务

流水线可以把多个任务串起来,比如发布版本的一系列流程 配置流水线任务 构建语法为Groovy,执行3次test(job名) node { stage("test") { echo ...

- P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2.p3.p4.p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽 ...

随机推荐

- docker.sock: connect: permission denied 解决

问题描述xjun@DESKTOP-L2R4GKN:~$ docker run -it hello-worlddocker: Got permission denied while trying to ...

- unsupported message type: DefaultFullHttpResponse (expected: ByteBuf, FileRegion) 原因以及解决办法

使用netty做http服务器的时候 用android链接 会出现这个错误 原因是http-aggregator顺序有问题 (ps:目前大部分国内博客都是这个排序有点坑爹): 官方文档说明:For c ...

- Qt编写地图综合应用54-动态点位标注

一.前言 动态点位标注是定制的一个功能模块,提供直接地图上选点设置标记点,点位信息用结构体存储,其中包括了经度.纬度.速度.时间等信息,单击对应的标注点可以显示详细的弹框信息,弹框信息采用自定义的ht ...

- Qt编写的项目作品12-简易视频播放器

一.功能特点 多线程实时播放rtsp视频流. 支持windows+linux+mac. 多线程显示图像,不卡主界面. 自动重连网络摄像头. 可设置边框大小即偏移量和边框颜色. 可设置是否绘制OSD标签 ...

- 基于AI底座的数智油气田参考架构

基于AI底座的数智油气田参考架构 Architecture for Intelligent & Digital Oilfileds Based-on AI 王权 2024.12.29 ...

- SpringBoot集成Jwt(详细步骤+图解)

SpringBoot集成Jwt(详细步骤+图解)Jwt简介 JSON Web Token是目前最流行的跨域认证解决方案,,适合前后端分离项目通过Restful API进行数据交互时进行身份认证 Jwt ...

- w3cschool-MyBatis 教程

参考 https://www.w3cschool.cn/mybatis/mybatis-dyr53b5w.html MyBatis 入门 SqlSessionFactoryBuilder用 SqlSe ...

- linux:网络

网络概念 网络发展 1.1969年互联网元年 2.局域网(LAN,Local Area Network).城域网(MAN).广域网(WAN,Wide Area Network) ip地址 网络基础命令 ...

- 《SpringBoot》EasyExcel实现百万数据的导入导出

24年11月6日消息,阿里巴巴旗下的Java Excel工具库EasyExcel近日宣布,将停止更新,未来将逐步进入维护模式,将继续修复Bug,但不再主动新增功能. EasyExcel 是一款知名的 ...

- react事件 报错Cannot read property 'setState' of undefined

import React, { Component } from "react"; export class TestHanderClick extends Component { ...