IP核——PLL

一、Quartus II创建PLL

1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager

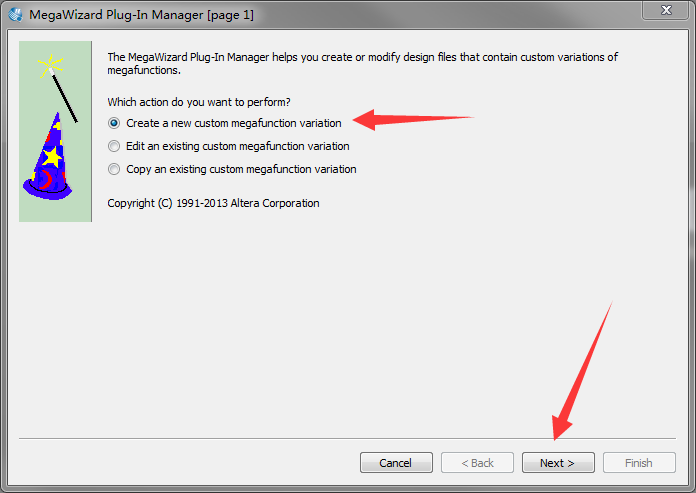

2.弹出创建页面,选择Creat a new custom megafunction variation,点Next

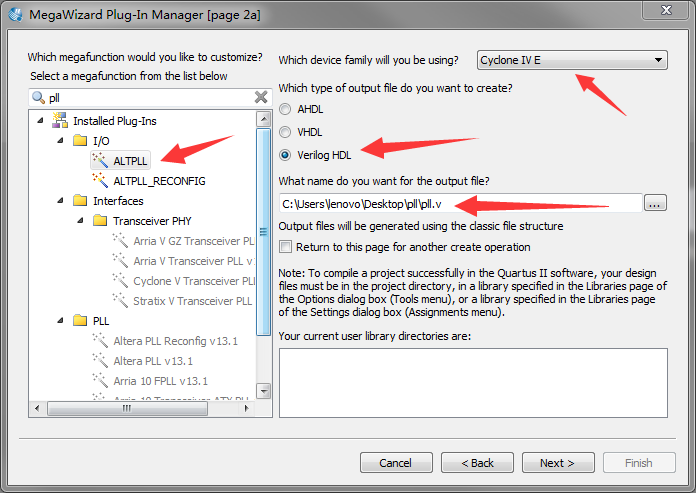

3.选择IP核,可以直接搜索pll,选择ALTPLL,右上方选择器件型号,语言选成Verilog,再填写一下路径名字,点Next,后面就是参数设置了。

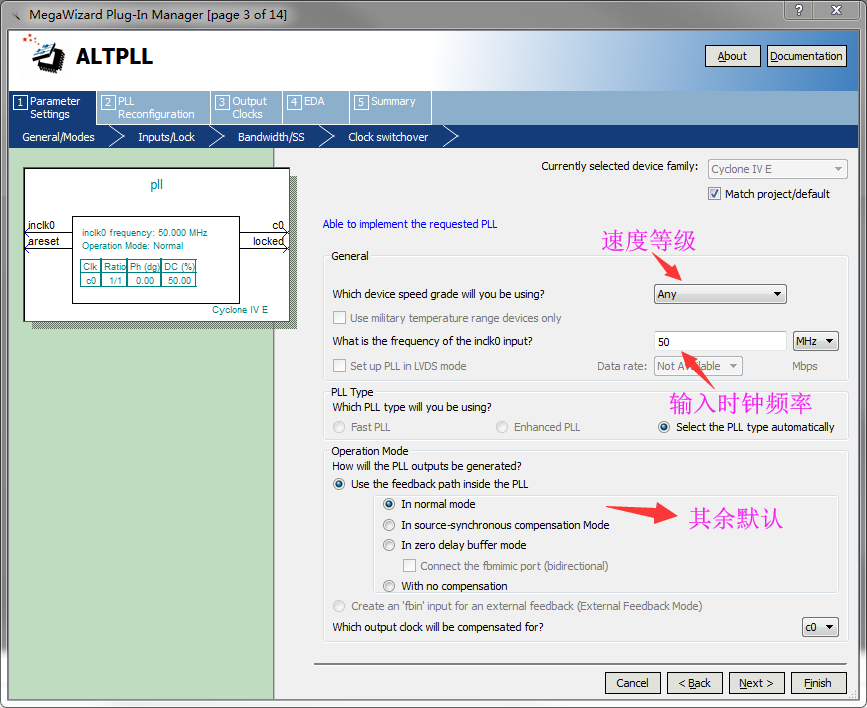

4.设置输入时钟频率,Next

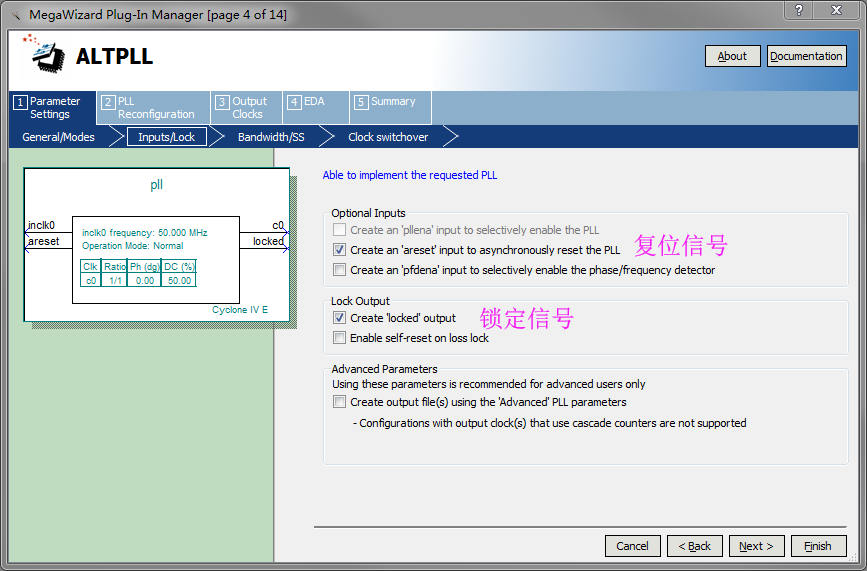

5.复位信号和锁定信号,锁定信号是指为1时,时钟就是稳定输出的状态,一般使用不勾选也行。Next

6.默认,Next

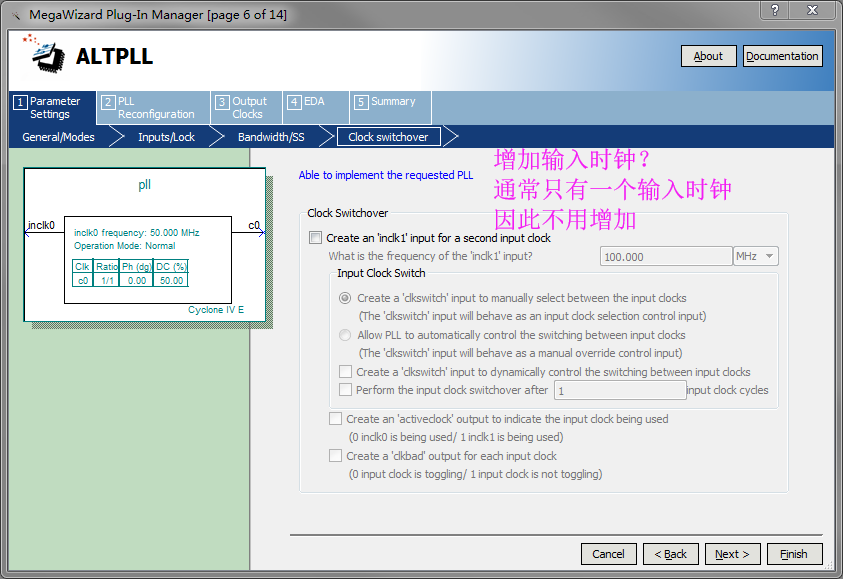

7.增加输入时钟,一般只有一个输入时钟,只用inclk0即可,因此无需增加,Next

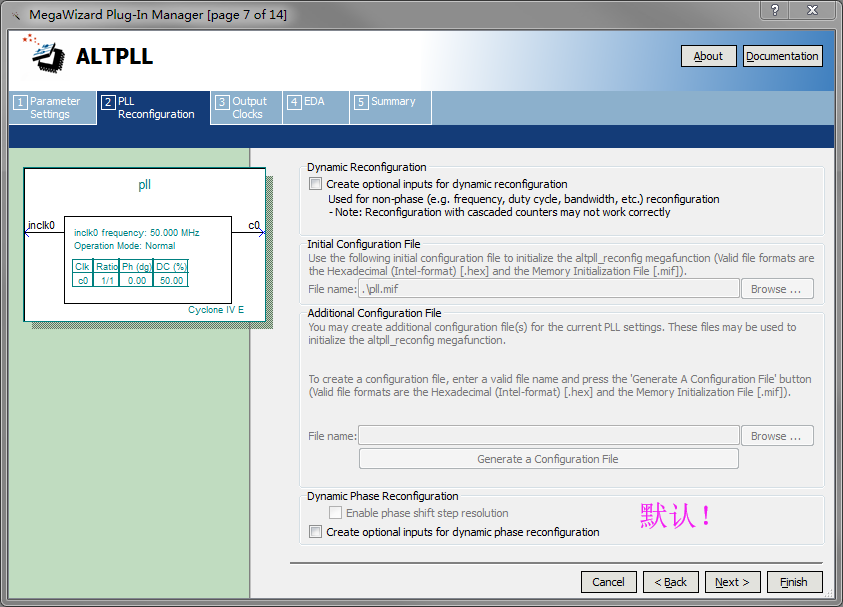

8.默认,Next

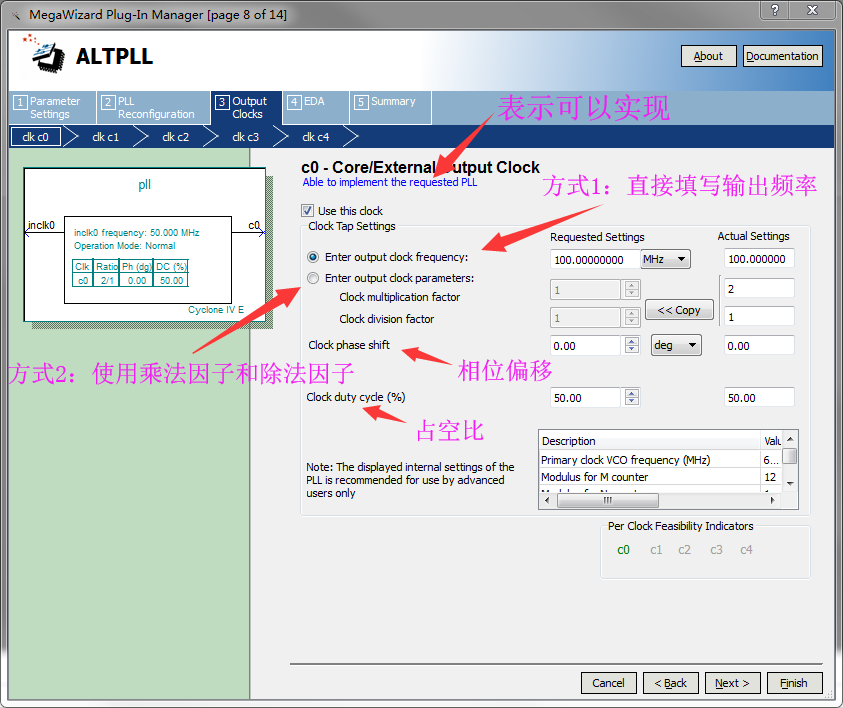

9.设置输出时钟,Next

10.后面是c1,c2,c3,c4,说明总的支持5个输出时钟,我们需要几个填几个就行,Next

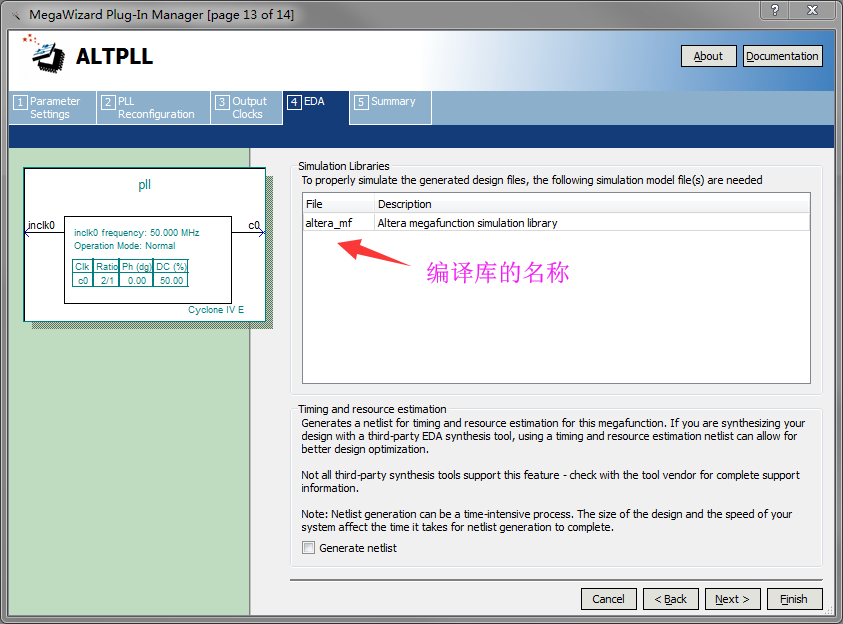

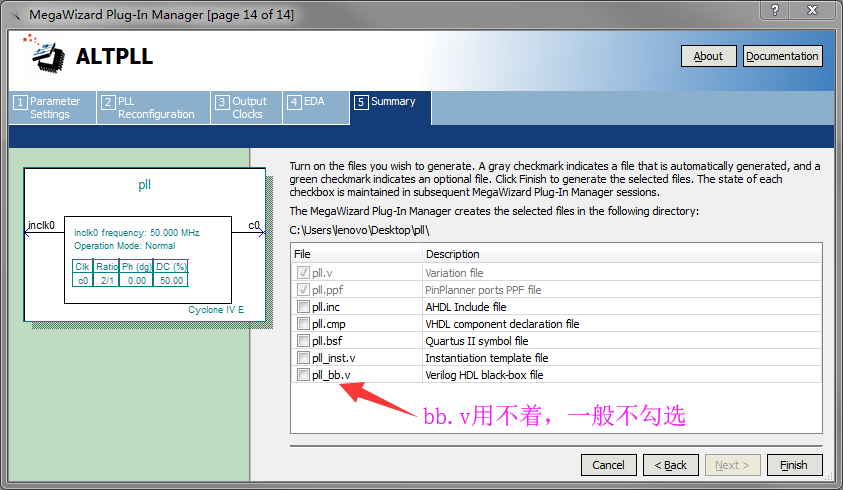

11.告诉你此IP核的编译库是什么,Next

12.输出的文件列表,除了正常IP核,还可以选择例化文件,注意bb.v文件用不到,一般是不勾选的。之后点finish就生成IP核了。

ps

1.Modelsim联合仿真ip核:quartus正常调用Modelsim就行

2.Modelsim独立仿真ip核:上面提示了仿真库名称,该仿真库可以在你的quartus安装目录下搜索到,把它复制出来,和其他文件一起添加到Modelsim中即可。

二、ISE

1.创建

1.创建ISE工程,IP核需要在ISE工程里面进行调用。点击Tools---Core Generator...

2.在新弹出来的界面中创建一个属于IP核的工程:file---new project,并填写文件存储位置和文件名称,一般为ipcore_dir文件夹,点击保存

3.弹出的Part处填写器件的系列、型号、封装以及速度等级,Generation处设置语言为Verilog,点击OK

4.点击文件夹,找到FPGA Features and Design---Clocking---Clocking Wizard,(也可以直接搜索)双击打开,进行参数设置

5.设置模块名和输入的时钟频率,Next

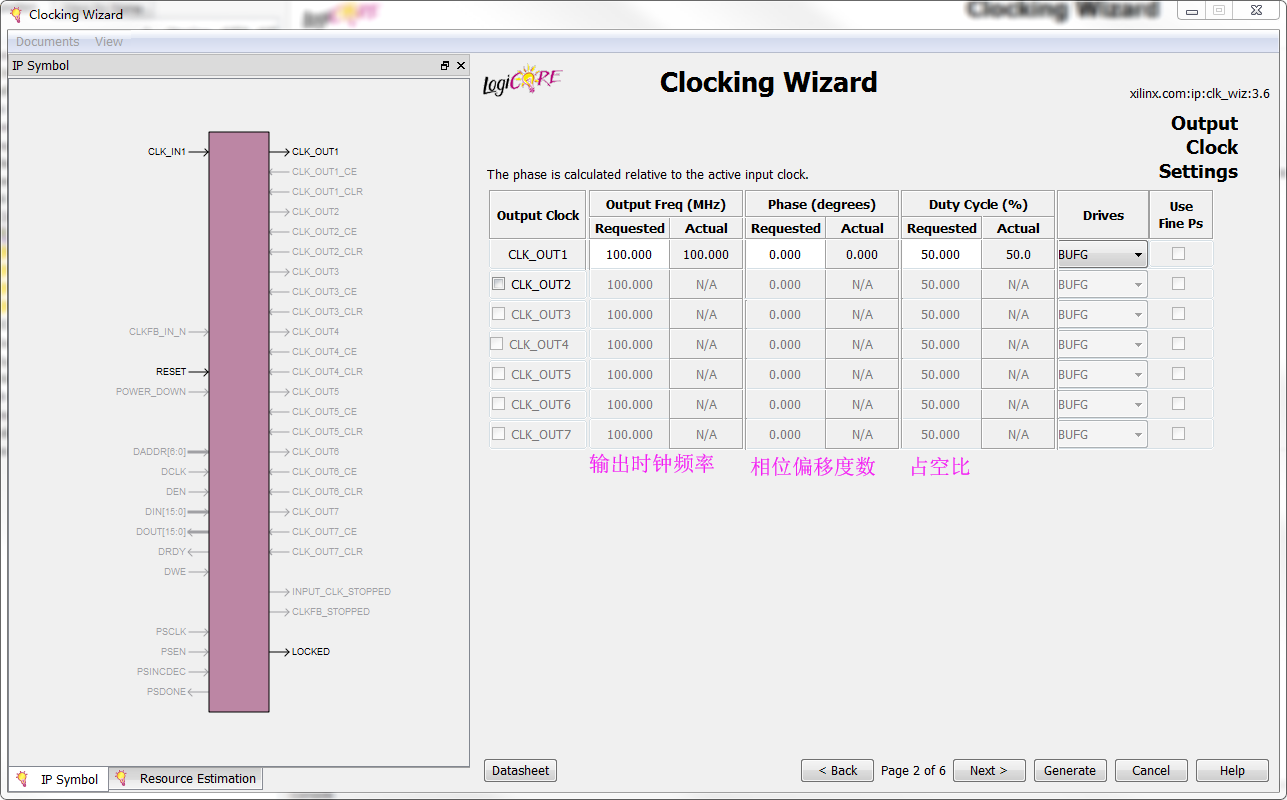

6.设置输出的时钟频率,还可以进行相位偏移度数和占空比,Next

7.设置控制信号,一般的设计不勾选就行,Next

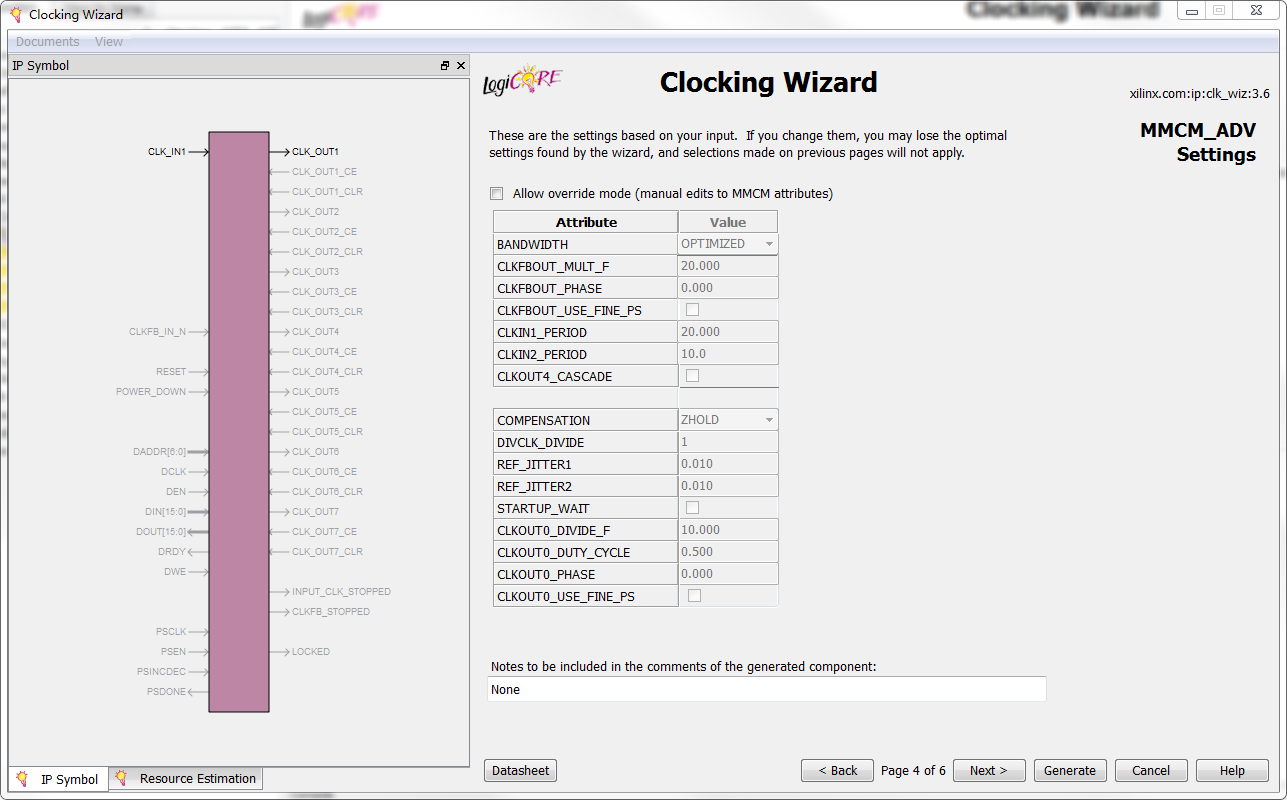

8.预览页面,Next

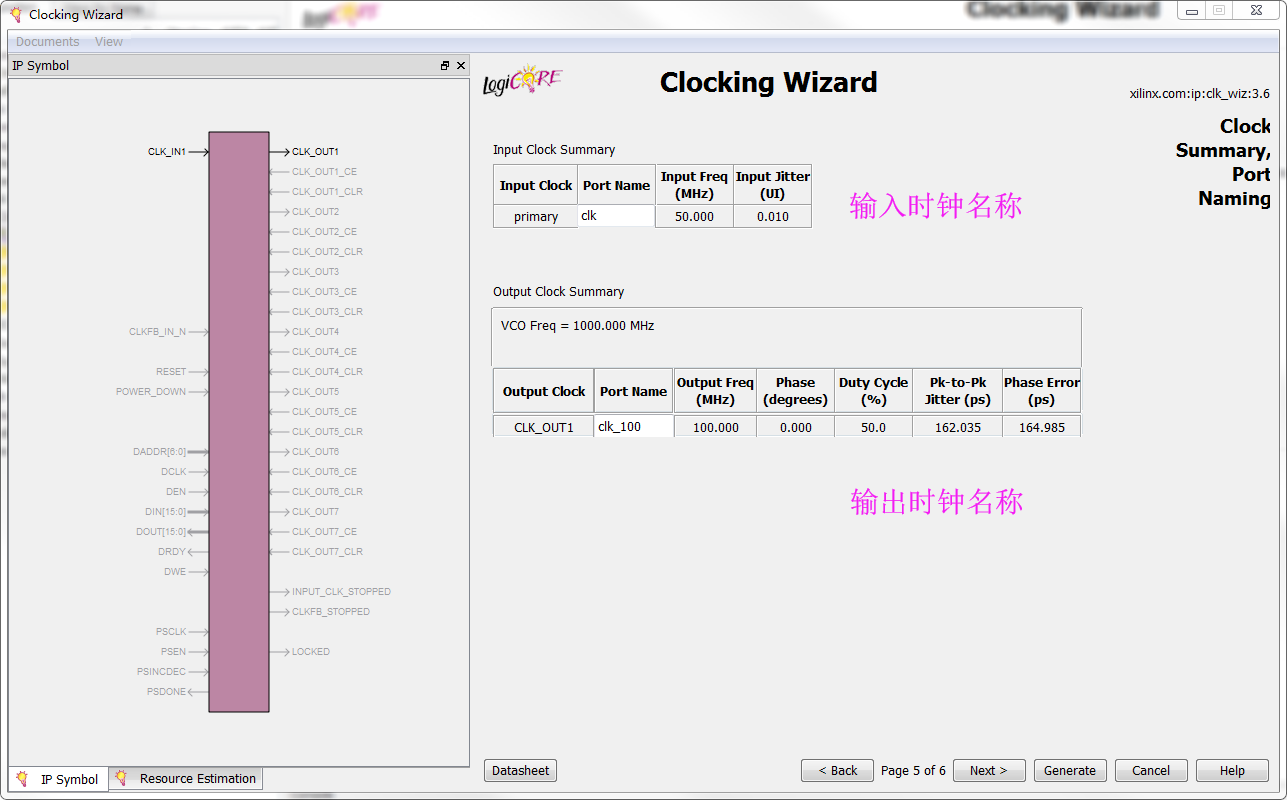

10.设置输入时钟和输出时钟的信号名称,Next

11.预览页面,点击Generate,静静等待IP核生成,生成后关闭弹出的readme.pll页面,关闭Core Generator页面。

2.使用

1.需要把创建好的IP核添加到工程中,创建IP核会生成一些文件,主要看以下三种文件:

①pll.v:IP核模块,看看里面的接口就行,不需要关注具体的代码含义

②pll.xco:进行内部优化后的IP核模块,我们把这个添加到工程中

③pll.veo:此IP核的例化模板文件

2.选中工程,添加pll.xco

3.选中工程,右键New Source,选中Verilog Test Fixture,填写名称和保存路径,一路Next。

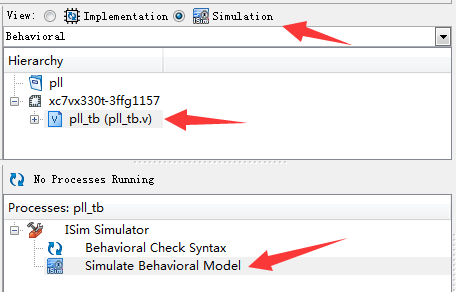

4.主页面切换至Simulation,可以看到生成了testbench文件,但是没有时钟驱动,我们设计一下。

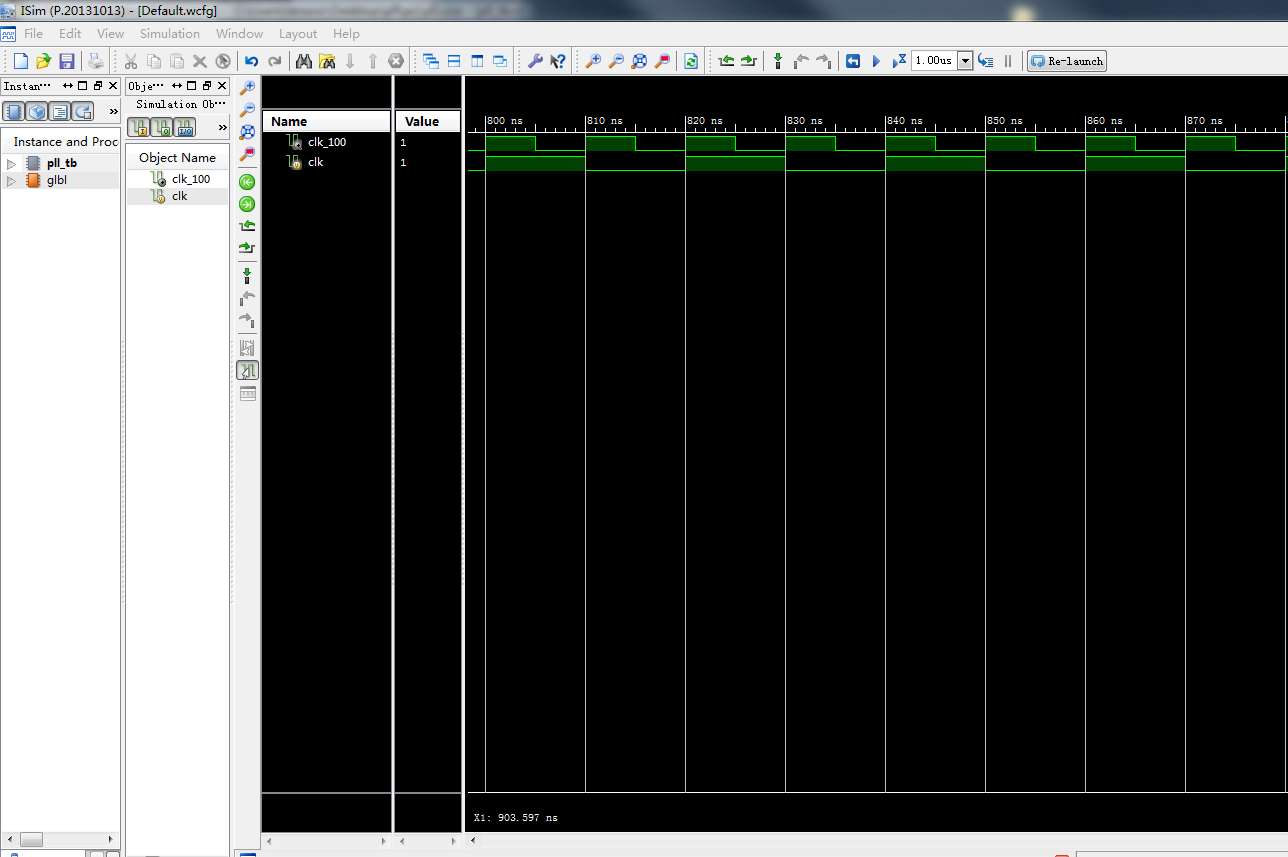

5.点击一下tb文件,下面进程栏中就出现了仿真工具,我们点击Simulate Behavioral Model,即可打开Isim,自动出波形。

PS:ISE也可以直接关联Modelsim,但有ip核的话还需要一个编译库的漫长过程,详细情况可自行百度。

IP核——PLL的更多相关文章

- 如何用ModelsimSE仿真IP核-以PLL为例

我们之前介绍了如何使用Modelsim SE进行仿真和利用do文件的仿真方法,但是其中待仿真的模块是我们自己编写的Verilog模块,但是在实际工作中,我们的设计中会经常用到FPGA厂商给我们提供的现 ...

- FPGA VGA+PLL+IP核笔记

1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ.2.分辨率使用了800*600@72HZ.3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色.VGA图形基 ...

- 7 Series GTP IP核使用总结 IP核配置篇

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级.本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用.本文是 ...

- 7系列高速收发器总结 GTP IP核使用篇

上一篇7系列收发器博文讲解了GTP IP核的基本配置,本文继续分析如何将它使用起来.生成IP核后打开example design,先看看工程中包含的文件结构. 顶层文件下包含了gtp ip核系统顶层文 ...

- Mdoelsim10.4怎么脚本单独仿真ISE14.7 IP核

软件版本: Modelsim10.4SE ISE14.7 仿真IP:时钟管理IP(clock wizard) 流程: 1.对于Modelsim10.4SE,并不自带Xilinx家的仿真库,因此首先 ...

- xilinx IP核配置,一步一步验证Xilinx Serdes GTX最高8.0Gbps

版权声明:本文为博主原创文章,未经博主允许不得转载. https://blog.csdn.net/u010161493/article/details/77658599 目录(?)[+] 之前 ...

- Altera三速以太网IP核使用(下篇)--- 百兆网接口设计与使用

MAC IP核的主要作用是:实现数据链路层协议,分为TX方向与RX方向,TX方向实现的是在原包文的前面加上7个55和1个D5,RX方向则相反.在使用这个 MAC IP核之前,首先确认下自己使用的网卡是 ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- Altera DDR2 IP核学习总结2-----------DDR2 IP核的生成

打开IP核工具,然后选择Verilog HDL选项,填写路径,写入文件名DDR2_IP.V,点击next PLL reference clock frequency填入板子晶振的频率50MHZ,这里设 ...

随机推荐

- lyft amundsen简单试用

昨天有说过amundsen 官方为我们提供了dockerc-compose 运行的参考配置,以下是一个来自官方的 quick start clone amundsen 代码 amundsen 使用了g ...

- tbls ci 友好的数据库文档化工具

tbls 是用golang 编写的数据库文档化工具,当前支持的数据库有pg.mysql.bigquery 此工具同时提供了变更对比.lint 校验,生成是markdown格式的 简单使用 安装 mac ...

- Python 下载超大文件

使用python下载超大文件, 直接全部下载, 文件过大, 可能会造成内存不足, 这时候要使用requests 的 stream模式, 主要代码如下 iter_content:一块一块的遍历要下载的内 ...

- mapreduce数据处理——统计排序

接上篇https://www.cnblogs.com/sengzhao666/p/11850849.html 2.数据处理: ·统计最受欢迎的视频/文章的Top10访问次数 (id) ·按照地市统计最 ...

- 微信小程序 报错Failed to load image

加载网络图片WXML代码: <image class="userinfo-avatar" src="{{avatarUrl}}"></imag ...

- python 安装离线库

(起因:报错找不到一个module,百度也找不到这个module,机智如我找宁博翻墙看怎么解决,毕竟是歪果仁的代码嘛,果真就在git找到了这个module哈哈哈哈机智如我!) 方法: 进入命令行窗口, ...

- Unity创作赛车游戏的四款插件

本文,我们将介绍其中4款:Racing Game Starter Kit.GeNa 2 .NWH Vehicle Physics.Curvy Splines. Racing Game Starter ...

- windows开机自动执行bat脚本

一.以windows下备份sql数据库为例,开机自动执行.bat脚本 1.新建dump.bat文件,文件中的代码如下: set YYYYmmdd=%date:~0,4%%date:~5,2%%date ...

- [LeetCode] 276. Paint Fence 粉刷篱笆

There is a fence with n posts, each post can be painted with one of the k colors. You have to paint ...

- [编程开发]STB image读取学习

为了便于学习图像处理并研究图像算法, 俺写了一个适合初学者学习的小小框架. 麻雀虽小五脏俱全. 采用的加解码库:stb_image 官方:http://nothings.org/ stb_image. ...