Xilinx FPGA编程技巧之常用时序约束详解

1. 基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径为:

- 输入路径(Input Path),使用输入约束

- 寄存器到寄存器路径(Register-to-Register Path),使用周期约束

- 输出路径(Output Path),使用输出约束

- 具体的异常路径(Path specific exceptions),使用虚假路径、多周期路径约束

1.1. 输入约束Input Constraint

OFFSET IN约束限定了输入数据和输入时钟边沿的关系。

1.1.1. 系统同步输入约束System Synchronous Input

在系统同步接口中,同一个系统时钟既传输数据也获取数据。考虑到板子路径延时和时钟抖动,接口的操作频率不能太高。

1‑1简化的系统同步输入SDR接口电路图

1‑2SDR系统同步输入时序

上述时序的约束可写为:

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";

1.1.2. 源同步输入约束Source Synchronous Input

在源同步接口中,时钟是在源设备中和数据一起产生并传输。

1‑3简化的源同步输入DDR接口电路

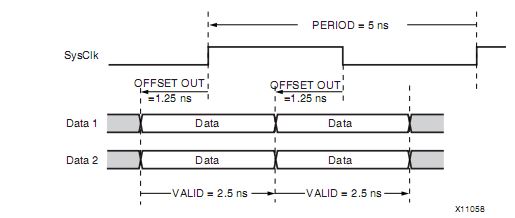

1‑4DDR源同步输入时序

上图的时序约束可写为:

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RISING;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING;

1.2. 寄存器到寄存器约束Register-to-Register Constraint

寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:

- 覆盖了时钟域的时序要求

- 覆盖了同步数据在内部寄存器之间的传输

- 分析一个单独的时钟域内的路径

- 分析相关时钟域间的所有路径

- 考虑不同时钟域间的所有频率、相位、不确定性差异

1.2.1. 使用DLL, DCM, PLL, and MMCM等时钟器件自动确定同步关系

使用这一类时钟IP Core,只需指定它们的输入时钟约束,器件将自动的根据用户生成IP Core时指定的参数约束相关输出,不需用户手动干预。

1‑5输入到DCM的时钟约束

上图的时序约束可写为:

NET “ClkIn” TNM_NET = “ClkIn”;

TIMESPEC “TS_ClkIn” = PERIOD “ClkIn” 5 ns HIGH 50%;

1.2.2. 手动约束相关联的时钟域

在某些情况下,工具并不能自动确定同步的时钟域之间的时钟时序关系,这个时候需要手动约束。例如:有两个有相位关系的时钟从不同的引脚进入FPGA器件,这个时候需要手动约束这两个时钟。

1‑6通过两个不同的外部引脚进入FPGA的相关时钟

上图的时序约束可写为:

NET“Clk1X"TNM_NET=“Clk1X";

NET“Clk2X180"TNM_NET=“Clk2X180";

TIMESPEC"TS_Clk1X"=PERIOD"Clk1X 7 5ns;

TIMESPEC"TS_Clk2X180"=PERIOD"Clk2X180“TS_Clk1X/2PHAS2 +1.25ns;

1.2.3. 异步时钟域

异步时钟域的发送和接收时钟不依赖于频率或相位关系。因为时钟是不相关的,所以不可能确定出建立时间、保持时间和时钟的最终关系。因为这个原因,Xilinx推荐使用适当的异步设计技术来保证对数据的成功获取。Xilinx约束系统允许设计者在不需考虑源和目的时钟频率、相位的情况下约束数据路径的最大延时。

异步时钟域使用的约束方法的流程为:

- 为源寄存器定义时序组

- 为目的寄存器定义时序组

- 使用From-to和DATAPATHDELAY关键字定义寄存器组之间的最大延时

1.3. 输出约束Output Constraint

输出时序约束约束的是从内部同步元件或寄存器到器件管脚的数据。

1.3.1. 系统同步输出约束System Synchronous Output Constraint

系统同步输出的简化模型如图所示,在系统同步输出接口中,传输和获取数据是基于同一个时钟的。

1‑7系统同步输出

其时序约束可写为:

NET "ClkIn" TNM_NET = "ClkIn";

OFFSET = OUT 5 ns AFTER "ClkIn";

1.3.2. 源同步输出约束Source Synchronous Output Constraint

在源同步输出接口中,时钟是重新产生的并且在某一FPGA时钟的驱动下和数据一起传输至下游器件。

1‑8源同步输出简化电路时序图

1‑9源同步小例子时序图

小例子的时序约束可写为:

NET “ClkIn” TNM_NET = “ClkIn”;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” RISING;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” FALLING;

1.3.3. 虚假路径约束False Path Constraint

令SRC_GRP为一组源寄存器,DST_GRP为一组目的寄存器,如果你确定SRC_GRP到DST_GRP之间的路径不会影响时序性能,那么可以将这一组路径约束为虚假路径,工具在进行时序分析的时候将会跳过对这组路径的时序分析。这种路径最常见于不同时钟域的寄存器数据传输,如下图:

1‑10虚假路径

其约束可写为:

NET "CLK1" TNM_NET = FFS "GRP_1";

NET "CLK2" TNM_NET = FFS "GRP_2";

TIMESPEC TS_Example = FROM "GRP_1" TO "GRP_2" TIG;

1.3.4. 多周期路径约束Multi-Cycle Path Constraint

在多周期路径里,令驱动时钟的周期为PERIOD,数据可以最大n*PERIOD的时间的从源同步元件传输到目的同步元件,这一约束降低工具的布线难度而又不会影响时序性能。这种约束通常用在有时钟使能控制的同步元件路径中。

图 1-11时钟使能控制的寄存器路径

必须说明的是上图Enable信号的产生周期必须大于等于n*PERIOD,且每个Enable传输一个数据。假设上图的n=2,MC_GRP为时钟使能Enable控制的多周期同步元件组,则约束可写为:

NET "CLK1" TNM_NET = "CLK1";

TIMESPEC "TS_CLK1" = PERIOD "CLK1" 5 ns HIGH 50%;

NET "Enable" TNM_NET = FFS "MC_GRP";

TIMESPEC TS_Example = FROM "MC_GRP" TO "MC_GRP" TS_CLK1*2;

Xilinx FPGA编程技巧之常用时序约束详解的更多相关文章

- FPGA编程技巧系列之输入输出偏移约束详解

1. 偏移约束的作用 偏移约束(Offset Constraint)用来定义一个外部时钟引脚(Pad)和数据输入输出引脚之间的时序关系,这种时序关系也被称为器件上的Pad-to-Setup或Clo ...

- SPI总线协议及SPI时序图详解

SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口.SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚 ...

- SPI总线协议及SPI时序图详解【转】

转自:https://www.cnblogs.com/adylee/p/5399742.html SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接 ...

- Javascript常用的设计模式详解

Javascript常用的设计模式详解 阅读目录 一:理解工厂模式 二:理解单体模式 三:理解模块模式 四:理解代理模式 五:理解职责链模式 六:命令模式的理解: 七:模板方法模式 八:理解javas ...

- 常用socket函数详解

常用socket函数详解 关于socket函数,每个的意义和基本功能都知道,但每次使用都会去百度,参数到底是什么,返回值代表什么意义,就是说用的少,也记得不够精确.每次都查半天,经常烦恼于此.索性都弄 ...

- Delphi中TStringList类常用属性方法详解

TStrings是一个抽象类,在实际开发中,是除了基本类型外,应用得最多的. 常规的用法大家都知道,现在来讨论它的一些高级的用法. 先把要讨论的几个属性列出来: 1.CommaText 2.Delim ...

- Eclipse或Myeclipse常用快捷键组合详解

Eclipse 是一个开放源代码的.基于Java的可扩展开发平台,就其本身而言,它只是一个框架和一组服务,用于通过插件组件构建开发环境.. Eclipse(Myeclipse)中有很多便于开发的快捷键 ...

- maven常用插件配置详解

常用插件配置详解Java代码 <!-- 全局属性配置 --> <properties> <project.build.name>tools</proje ...

- e lisp 常用缓冲区函数详解

e lisp 常用缓冲区函数详解 函数名 函数概要 buffer-name 返回当前缓冲区的名字 buffer-file-name 返回当前缓冲区所指文件的名字,包括路径 current-buffer ...

随机推荐

- kafka-manager 的编译和使用(附安装包)

kafka-manager 的编译和使用(附安装包) 学习了:https://my.oschina.net/wangjiankui/blog/653139

- Vue中对获取的数据进行重新排序

var Enumerable = require('linq'); // 使用linq 按照RegisterID排序listJust是自己定义的数组,来接收数据.listJust: [] addDat ...

- 加入收藏BUG改善

<script type="text/javascript"> function add_favorite(a, title, url) { url = url || ...

- vim note(5)

.vimrc 的设置 $HOME/.vimrc 的普通设置,例如以下. set nocompatible "" not compatible with VI "" ...

- POJ 2299 Ultra-QuickSort(线段树+离散化)

题目地址:POJ 2299 这题以前用归并排序做过.线段树加上离散化也能够做.一般线段树的话会超时. 这题的数字最大到10^10次方,显然太大,可是能够利用下标,下标总共仅仅有50w.能够从数字大的開 ...

- swift 笔记 (二十一) —— 高级运算符

高级运算符 位运算符 按位取反: ~ 按位与运算: & 按位或运算: | 按位异或运算: ^ 按位左移运算: << 按位右移动算: >> 溢出运算符 自从swif ...

- c# 获取根节点的属性信息

<?xml version="1.0" encoding="UTF-8"?> <!--课程封面信息 --> <GK version ...

- bootrap 手风琴Collapse源码分析

/* ======================================================================== * Bootstrap: collapse.js ...

- 【NOI 2007】 社交网络

[题目链接] 点击打开链接 [算法] 首先,跑floyd,计算最短路和最短路径数 然后,计算答案,枚举k,s,t,若dist[s][k] + dist[k][t] = dist[s][t], 那么,点 ...

- 4. extjs中form中的frame:true表示什么

转自:https://blog.csdn.net/qiu512300471/article/details/23737217 设置为true时可以为panel添加背景色.圆角边框等,如下图 下面的是f ...