自建AXI4的IP核的地址问题

自建AXI4的IP核的地址问题

1、问题概述

在AXI4中,对应的操作通过对对应的寄存器设置来完成。其中的寄存器又分为数据寄存器和地址寄存器。其中,如果只是想要操作数据的话,只需要使用数据寄存器即可。在自建AXI4的IP时,会选择数据寄存器的个数。在打开封装文件时也可以看到数据寄存器。一般是slv_reg0·····等编号。其中slv代表从机,reg0代表寄存器0.这里有一个如何操作寄存器的问题。

2、问题解决

可以看出,这个数据寄存器既可以接收AXI的数据,也可以发送数据到AXI上。这里的功能十分类似一个三态门。只不过这里的控制信号也是一个可控寄存器的输出。主机通过设置配置寄存器决定输入还是输出,通过地址读取或者写入数据。严格来说,如果要使用这个寄存器的作为输入输出口,是需要和控制信号也就是配置寄存器的状态关联的。比如,作为接收主机数据时的输入寄存器,该寄存器作为正常的输入口,可以直接输出到所需的PL模块。当作为发送数据到主机的输出口,则需要接受来自PL模块的信号。显然,这里是有矛盾的。一个寄存器不可能同时有两个输入和输出。所以,虽然AXI总线是可以设置从机的通信模式:接收或者发送,但是,在设计时,具体到某个数据寄存器时,只能作为输入或者输出,不可更改。作为向主机输入的输出寄存器,甚至可以直接采用wire型变量,实时等待发送。而作为向主机接收数据的输入寄存器,只需要用reg向其他变量赋值即可将数据导出到PL。显然,发送到主机是比较困难的,需要等待主机的读取。主机是可以对每个特定的寄存器设置输入输出模式的。所以在PS端需要提前设置模式以便寄存器正确的工作。当然,如果一定要实现某个寄存器的输入输出灵活转换,则可以牺牲另外一个寄存器用于配置PL的寄存器。如果对AXI总线的信号比较熟悉的话,也可以直接读取对应的从地址进行判断,这就是需要更加复杂的结构。现在暂时不涉及。

3、问题总结

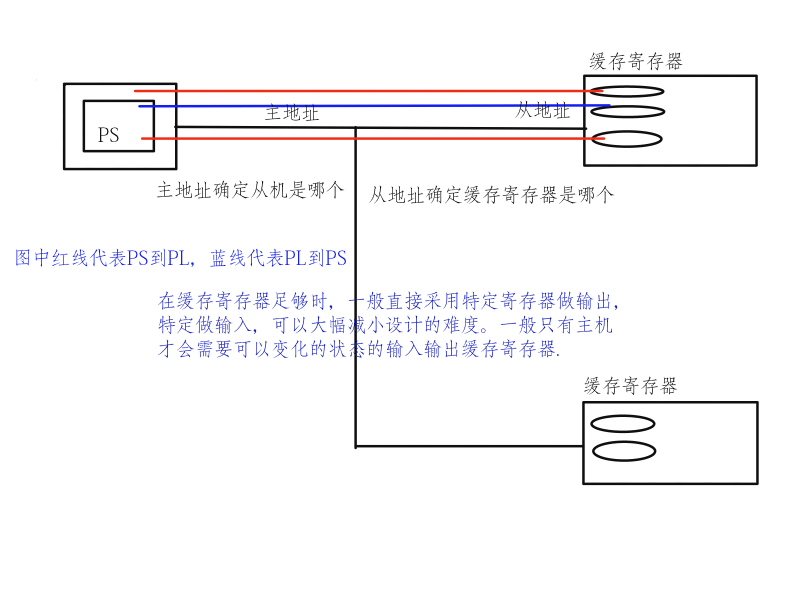

这里主要通过对主地址和从地址的对应的物理信号出发,分析所需要的数据操作。下面给出一个AXI数据传输的关系图。

这只是用于理解PS端设计时的示意图。如果想要完全理解AXI的从机逻辑,必须要五个通道和辅助的模块出发。后面会逐渐涉及数据的读写、地址的读写、响应信号的构建、优先级判断、数据缓存等各种细节的问题。

自建AXI4的IP核的地址问题的更多相关文章

- 基于AXI4总线卷积FPGA加速IP核的尝试

本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面.使用的硬件平台是Zedboard. 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块 ...

- Xilinx IP核的根目录地址,有datasheet 和仿真相关的资料

C:\Xilinx\14.7\ISE_DS\ISE\coregen\ip\xilinx\dsp\com\xilinx\ip Xilinx IP核的根目录地址,有datasheet 和仿真相关的资料

- NIOS II 自定义IP核的静态地址对齐和动态地址对齐

如果使用静态地址对齐(每个寄存器在Avalon总线上占4个字节的地址)设置IP使用静态地址对齐的方式为,在hw.tcl脚本里加上一局话:set_interface_property as addres ...

- AXI-Lite总线及其自定义IP核使用分析总结

ZYNQ的优势在于通过高效的接口总线组成了ARM+FPGA的架构.我认为两者是互为底层的,当进行算法验证时,ARM端现有的硬件控制器和库函数可以很方便地连接外设,而不像FPGA设计那样完全写出接口时序 ...

- 理解AXI Quad Serial Peripheral Interface(SPI) IP核

reference : PG153-AXI Quad SPI v3.2 LogiCORE IP Product Guide.pdf 在使用MicroBlaze过程中,调用了此IP,所以有必须仔细学 ...

- Vivado中xilinx_BRAM IP核使用

Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3 BRAM IP核包括有5种类型: Single-port RA ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- (转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)

原地址modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核) 1.打开D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\compxlibgui.e ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

- Lattice 的 Framebuffer IP核使用调试笔记之IP核生成与参数设置

本文由远航路上ing 原创,转载请标明出处. 这节笔记记录IP核的生成以及参数设置. 先再IP库里下载安装Framebuffer 的ipcore 并安装完毕. 一.IP核的生成: 1.先点击IP核则右 ...

随机推荐

- Annotation-specified bean name conflicts with existing

问题说明 Annotation-specified bean name conflicts with existing,non-compatible bean definition of same n ...

- spring boot实现邮箱验证码注册

最近在设计自己的博客系统,涉及到用户注册与登录验证. 注册这地方我先采用最传统的邮箱验证码方式.具体的实现方式如下: 1.有关如何配置spring boot发送邮件,请参考我的另一篇文章: https ...

- docker清理已停止的容器

docker rm -v $(docker ps -aq -f status=exited) 可以将该命令写成shell脚本或者alias.-v参数表示同时清理数据卷

- Jenkins配置SpringBoot项目启动脚本

目录 背景 脚本编写 变量说明 使用说明 Q&A jenkins部署时错误 背景 上一篇Jenkins配置介绍了Jenkins远程部署的相关配置和步骤,但是最后的部署脚本只适用于部署原始tom ...

- DataGear 数据可视化看板整合前端框架Vue

DataGear 看板JS对象的loadUnsolvedCharts()函数,用于异步加载页面端动态生成的图表元素,利用它,可以很方便整合Angular.React.Vue等前端框架. 本文以Vue为 ...

- 【Azure 环境】AAD 注册应用获取AAD Group权限接口遇 403 : Attempted to perform an unauthorized operation 错误

问题描述 通过Azure AD的注册应用获取到Token后,访问AAD Group并查看日志信息时候,遇见了 {"error":{"code":"Un ...

- 【Azure 应用服务】Azure Function 部署槽交换时,一不小心把预生产槽上的配置参数交换到生产槽上,引发生产错误

问题描述 部署Function代码先到预生产槽中,进行测试后通过交换方式,把预生产槽中的代码交换到生产槽上,因为在预生产槽中的设置参数值与生产槽有不同,但是在交换的时候,没有仔细检查.导致在交换的时候 ...

- 回顾 2023,NebulaGraph 的这一年的变化

一年又过去了,感谢你和 NebulaGraph 一起又走过一个春夏秋冬.在这 365 天里,我们一起见证了 214 个 commit 带来的 NebulaGraph 3 个中版本的上线,它们分别是 v ...

- 基于 Nebula Graph 构建百亿关系知识图谱实践

本文首发于 Nebula Graph Community 公众号 一.项目背景 微澜是一款用于查询技术.行业.企业.科研机构.学科及其关系的知识图谱应用,其中包含着百亿级的关系和数十亿级的实体,为了使 ...

- Windows NFS 真弱 → 中文乱码导致文件找不到

开心一刻 正睡着觉,然后来了个电话 对方说:你好,方便面是吗 我愣了一下,以为是恶作剧 回了句:我不是,我是火腿肠! 就挂了电话 又躺了好一会,忽然琢磨过来...... 不对呀,她好像说的是:你好,方 ...