Xilinx原语学习之时钟资源相关原语

一直来,都是使用Vivado中自带的GMIItoRGMII IP核来完成GMII转RGMII的功能;尽管对GMII及RGMII协议都有一定的了解,但从没用代码实现过其功能。由于使用IP时,会涉及到MDIO配置IP寄存器的问题,觉得麻烦。因此决定用代码实现GMII转RGMII的功能。

参考Lattice的开源代码,进行移植。移植后在Vivado中进行编译时没有问题,但一旦进行实现(Implementation)时就会有如下错误:

[Place 30-574] Poor placement for routing between an IO pin and BUFG.

实在纳闷,于是深入挖掘原因。

从编译的原理图来看,rgmii_rclk在输入端已被Vivado自动添加了一个IBUF以及BUFG;通过Vivado中的Synthesis的Settings,取消自动添加BUFG的选项;再实现时没有错误了,且可以生成bit文件;但时序严重不满足。

查看之前使用GMIItoRGMII的IP工程中的Schematic,发现rgmii_rclk输入后添加了三个原语模块:IBUF、BUFR以及BUFG。其中IBUF是在信号输入端处添加了,BUFR是紧跟着IBUF,然后其输出的信号被内部的D触发器所使用,其中有一路直接连接到BUFG,然后通过BUFG输出到管脚(作为GMII的时钟输出)。

藉此机会,想更进一步学习这几个原语的不同之处:

-------------------------------------------------------------------------------------------------------------

在Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及由他们所衍生出来的各种变种。它们之间的特点和区别如下:

>>>BUFIO

BUFIO是IO时钟网络,顾名思义,它只能驱动IO Block里面的逻辑,不能驱动CLB里面的LUT,REG等逻辑。BUFIO可以被如下节点驱动:

1、SRCCs and MRCCs in the same clock region

2、MRCCs in an adjacent clock regionusing BUFMRs

3、MMCMs clock outputs 0-3 driving the HPC in the same clock region

>>>BUFR

BUFR是regional时钟网络,顾名思义,它的驱动范围只能局限在一个clock region的逻辑,但是它可以同时驱动IO和内部逻辑。BUFR可以被如下节点所驱动:

1、所有能驱动BUFIO的节点

2、MMCMs clock outputs 0-3

3、General interconnect

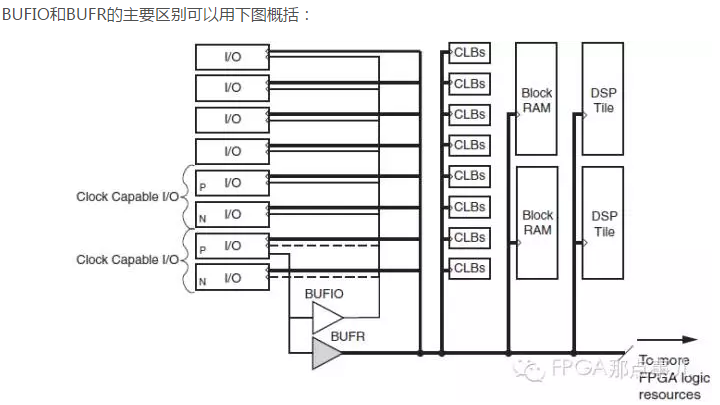

BUFIO和BUFR的主要区别可以用下图概括:

>>>BUFG

BUFG是全局时钟网络,这个大家最熟悉了,它可以驱动所有的IO和逻辑,并且可以被Transceiver所驱动。如果时钟信号要走全局时钟网络,必须通过这个BUFG来驱动,BUFG可以驱动所有的CLB,RAM,IOB。Zynq一共有22个BUFG全局时钟线。

BUFR相比BUFG的最大优势是skew和功耗都比较小,在源同步的设计中,这一点也是很关键的。

>>>BUFR和BUFMR有什么区别?

BUFMR是7系列才有的时钟buffer,它是在有些源同步设计中逻辑IO跨上中下三个Bank;而BUFR仅仅能够驱动一个Bank,所以需要BUFMR级联BUFR来完成每个Bank的功能功能,如下图:

>>>BUFH怎么用?

BUFH,BUFH驱动区域中的水平全局时钟树,Xilinx的时钟是通过时钟树来分布的。可用于互联逻辑、SelectIO逻辑,DSP48E1模块或者Block RAM资源的时钟驱动。

>>>时钟资源选择上是不是BUFG最优?

这个要根据设计,很多AD DA需要源同步设计,如果上了BUFG由于时钟走线延迟较大;完全跟数据不同步,很难再进行正确的采样。接口设计的逻辑量一般比较小,不建议上全局。

下面介绍下Xilinx时钟的管理:

Xilinx芯片全局时钟资源的使用方法主要有下面5种:

A、GCLK——>IBUFG——>BUFG

IBUFG后面连接BUFG的方法是最基本的全局时钟资源的使用方法,其等效于BUFGP

B、GCLKP&GCLKN——>IBUFGDS——>BUFG

当输入时钟为差分信号时候,需要使用IBUFGDS原语。

C、IBUFG+DCM+BUFG

通过DCM(Digital clock manage)不仅能对时钟进行同步、移相、分频、倍频等变换,而且可以使用全局时钟的输出无抖动和小延迟。

D、Logic + BUFG

BUFG不但可使用IBUFG的输出,还可以驱动其他普通信号的输出。当某个信号的扇出非常大,并且要求抖动延迟最小时,可以使用BUFG驱动该信号,使得该信号利用全局时钟资源。

E、Logic + DCM + BUFG

DCM可以改变也可以控制变换普通时钟信号。

-----------------------------------------------------

附录,参考链接:

《Xilinx FPGA器件中时钟资源的说明以及使用》

https://www.jianshu.com/p/3da8c9eca03a

Xilinx原语学习之时钟资源相关原语的更多相关文章

- Xilinx FPGA的专用时钟引脚及时钟资源相关

主要参考了https://www.eefocus.com/liu1teng/blog/12-02/237897_4533d.html .Xilinx UG471.UG472以及Xilinx Forum ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- Xilinx约束学习笔记(二)—— 定义时钟

2. 定义时钟 2.1 关于时钟 为了获得最佳精度路径覆盖信息,必须正确定义时钟. 时钟要定义在时钟树的根 pin 或 port 上,称为 source point. 时钟的边缘应该由周期和波形进行组 ...

- Spartan6系列之Spartan6系列之芯片时钟资源深入详解

1. 时钟资源概述 时钟设施提供了一系列的低电容.低抖动的互联线,这些互联线非常适合于传输高频信号.最大量减小时钟抖动.这些连线资源可以和DCM.PLL等实现连接. 每一种Spartan-6芯片提 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- Xilinx约束学习笔记(一)—— 约束方法学

<Xilinx约束学习笔记>为自己阅读 Xilinx 官方 UG903 文档后的学习笔记,大多数为翻译得来,方便大家学习. 1 约束方法学 1.1 组织约束文件 Xilinx 建议将时序约 ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

随机推荐

- 剑指Offer_编程题_11

题目描述 输入一个整数,输出该数二进制表示中1的个数.其中负数用补码表示. class Solution { public: int NumberOf1(int n) { int size = 3 ...

- Struts2_配置文件

1.结果跳转方式 <struts> <constant name="struts.devMode" value="true"></ ...

- java io系列04之 管道(PipedOutputStream和PipedInputStream)的简介,源码分析和示例

本章,我们对java 管道进行学习. 转载请注明出处:http://www.cnblogs.com/skywang12345/p/io_04.html java 管道介绍 在java中,PipedOu ...

- springboot中通用mapper结合mybatis generator的使用

通用mapper就是指的是 tk.mybatis 包下的.这个是通用mapper就是说自动生成的dao层需要继承这个框架提供的mapper类.而我们之前用的org.mybatis这个最开始是普通的 ...

- 不存数据库的token验证

不需要数据库存,纯粹通过计算来判断是否相等 {name:chuck,id:1}|自己加密方式加密后的内容 截取加密内容,反解,判断反解内容与{name:chuck,id:1}是否相同,只会耗费计算资源 ...

- C# 数据类型之 String(字符串)

Ø 简介 在开发中最常见的数据类型就是 String 类型,即字符串类型.为什么要单独讨论下这个类型,是因为:它是系统内置的基础数据类型:它的使用频率非常高:它是一个特殊的引用类型.其实大家都会使用 ...

- udp_connect函数

#include <netdb.h> #include <stdlib.h> #include <unistd.h> #include <string.h&g ...

- 小试XML实体注入攻击

基础知识 XML(Extensible Markup Language)被设计用来传输和存储数据.关于它的语法,本文不准备写太多,只简单介绍一下. XML基本知识 1 2 3 4 5 <?xml ...

- core.net 创建coreclass 项目出现一些问题

错误如下: Project CoreTest does not have a lock file. Please run "dotnet restore" to generate ...

- 阿里云CentOS7.2卸载CDH5.12

#####################删除前最好将之前的下载的rpm包和parcels包备份一下##################### 1.停止serviceservice cloudera- ...