Loongson Log

就看看能坚持多久吧

22/2/2及以前:

- 参照想象中的p7内容增添部分版CP0、部分中断/异常机制;

- 改sram接口:查阅文档func_test、sram相关内容;查阅vivado bram IP核相关内容;似乎有了进一步理解;PC地址未定

22/2/8:修bug

- 补上SU缺失的M_mfc0信号;

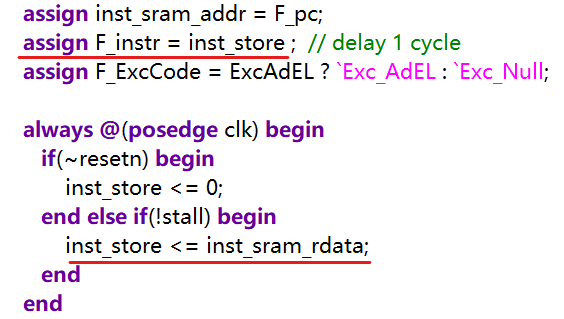

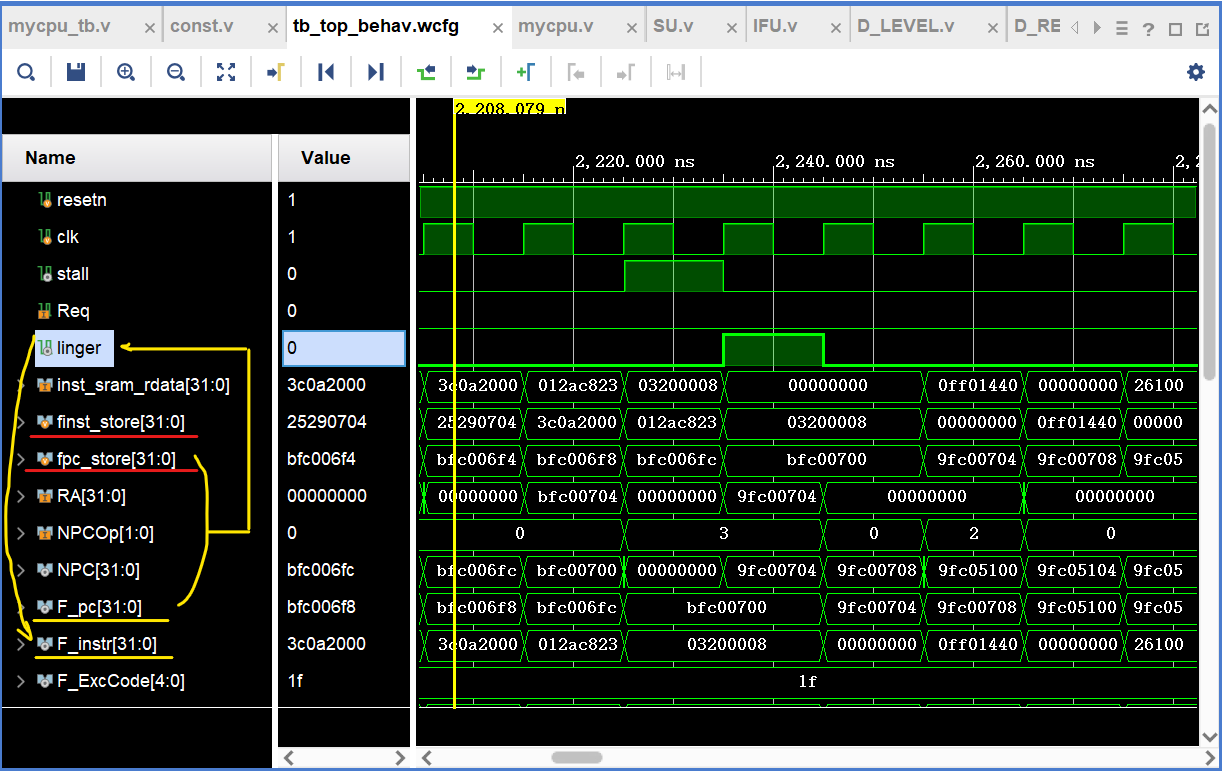

- inst_sram使用了IP核。bram IP核请求读取后,不仅在下一拍返回数据,且数据只保持一拍。因而在stall时若不保存上一拍信息,将会将会丢失上一拍已取回的D_instr

不可取的写法:

inst_store会比inst_sram_rdata慢一拍,原因在于inst_sram_rdata将在clk上升沿时更新,因而该上升沿被写入inst_store的是旧值

解决方案:

linger为组合逻辑结果,不知是否有漏洞

22/2/9:修bug

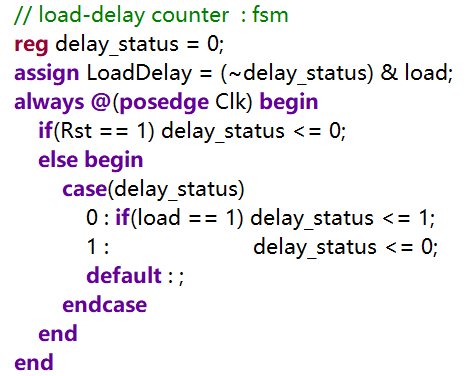

- 作为data_sram的同样是bram IP核。解决load类指令延一拍获取rdata的问题。

设计简单的2状态mealy型fsm,产生组合信号LoadDelay使全流水(M级前,W级无关可放过)均暂停一周期

- 功能测试过64个点

22/2/10:修bug

- 阅读分析异常处理代码

- 结合文档增修CPO寄存器,暂时将sel默认为0,之后扩展需要改二维数组

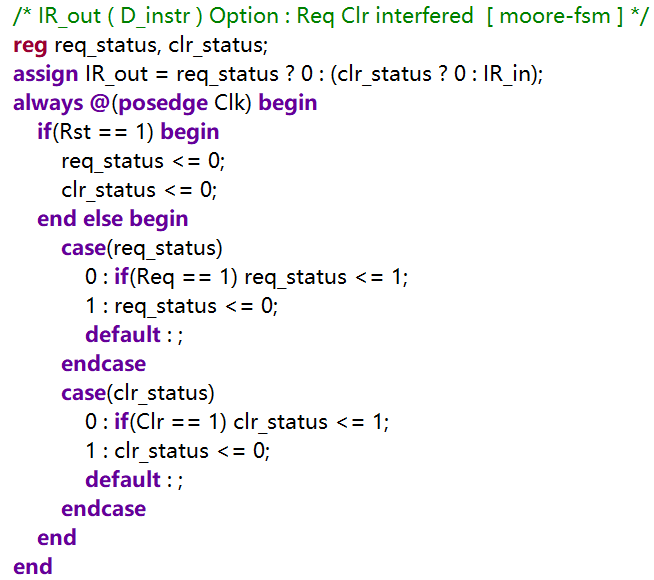

- 由于对D级D_instr逻辑的修改(适配inst_sram IP核),导致其为同F_instr的组合逻辑,不受Reset、We等通用信号的控制,因而需增加逻辑控制

设计简单的2状态moore型fsm,产生组合信号reg_status。当Req==1时,下一时钟上升沿reg_status <= 1,此时D_instr转接为0信号。

由于实现精确异常,Req信号1时,不能写DM

暂停与异常同时存在时,PC写使能应置1

功能测试过72个点

expect:

- 上层信号(Stall、Req等)的传输和命名形式需优化

- 增添CP0-Count寄存器,以及理解CP0-Compare寄存器、计时器中断相关机制

22/2/11:修bug

具体记在P7贴里了

- 功能测试过了76个点;

- 发现中断相关机制理解有偏差(所以没过第77个点),重新阅读文档,增加Count、Compare寄存器及相关机制,增加Req响应机制,设置CP0各寄存器信号的读写性(尤其是只读位)

22/2/12:修bug-小成

- 调通了软件中断和计时器中断;sram功能测试89个点通过。

22/3/29:改AXI接口

- 解决了获取不到数据的问题,是arvalid、awvalid误接(一开始理解就是错的);能运行了

- stall和等待rdata冲突未解决,开局就崩

22/3/30: 修bug

- 解决了昨日bug,不是stall的原因,是跳转指令在未能生效的情况下反而继续流水

- 今日新bug:写地址时,读指令未被接收而漏过

22/4/13及之前:过AXI测试

总算调通了

cache结构理解记录

22/7/13

不行不行,之前每天接近中午才起床,下午才会开始干点活,还经常被b站方舟原神干扰,晚上吃完饭还要捧手机在床上赖一个多小时,有时弥补性的弄到一两点,躺床上还翻手机。完全是没在好好工作嘛,怎么对的起队友和自己的本愿捏!

之前在ubuntu虚拟机搭好了大概的环境(vivado用vcs仿真还崩了,内存调8GB了不知道还好不好),看了pmon的代码(仅大概搞清启动的流程),然后看了soc_up的部分代码,着实是在摸鱼了。

当下的目标:

- core代码阅读:先偏重icache部分,然后进行必要的重写和修正,添加icache指令;最终cpu core必须读完并能掌握!

- soc各部分外设/接口/控制器理解并准备书写

- pmon/linux进一步深入,为添加外设+调试cpu核做理论准备

不能再烂了,借此机会养成较好的开发习惯!我不正在做自己乐意做的事情嘛,这样还摸鱼的话,未来痴心妄想吧

| Working Schedule (工作期间不得娱乐,思想上的苗头必须掐灭) |

|---|

| 晨起(早饭期间可以清一下方舟日常,摆摆心境) |

| 每日规划写博客上 |

| 08:30 ~ 12:00 工作-上午 |

| 中饭,休息 |

| 14:00 ~ 18:00 工作-下午 |

| 晚饭时间不确定,加上一些可能的小摸鱼,不得超限 |

| 20:00 ~ 24:00 工作-晚上 |

| 每日总结写博客上 |

22/7/14

起迟了些。。昨晚还是睡迟了。今天主要就是读完icache相关代码,开始修改/重写;再去了解一个接口。

小结

- 早上边开个会边瞅了会儿代码。

- 中饭时玩了会儿原神,结果心又没收住,下午又躺床上翻手机看漫画去了。临近傍晚才正常了,一旦看进去了就有了惯性,而且理解一块代码后心情也很是舒畅,所谓良性循环和凉性循环。

- 晚上状态良好,icache代码基本厘清了(受益匪浅但也有好些可以改进),axi以前没太弄清的burst终于好好解决了(还是得静下心来读文档),sdpram的xpm宏也熟悉了些;可以着手加icache指令和重构

- 临近11点又松懈打开了b站,一看又是一个多小时,堤溃蚁穴。人性的缺陷要尽可能规避

22/7/15

小结

- 还是起迟了,就是醒了有睡然后睡过头,晚上睡太迟;中午金苹果群岛收集了13个海螺,之后又犯病咯,下午过半时才开始工作

- 看pipeline相关的内容,尝试加的icache相关指令应该有三,一时又迷糊了,得把前后端熟悉了才好加指令及相关流水情况;不了解axi_crossbar,查半天无果,后来察觉应该就是AXI Interconnection;总之感觉时间不等人,要有点执念和狠劲儿啊。

- 鹿鸣的直播挺赞的,一时又激起“这才是充实人生该做的事情”这一情感;技术本身是令人兴奋的,但期间的绝境是不能逃避的。

22/7/16

小结:

每天都得经历一边所谓“人生”,阅尽浮世喧嚣,才甘墨守寂寥本心;人话就是白天玩够了后才干活

- 今天下午准点开干了,因为中午即时缓冲了;然后随后被刀剑神域进击篇吸引了,感觉挺棒的

- 主要还是pipeline的阅读,rt,rs,imm等在icache后的fifo中预解码(preDecoder),tWB1/tWB2没太搞懂,应该是AT法转发相关的;而后续在backend中正式解码(decoder)主管功能相关信号;cache指令还不知道解出什么值,尚需浏览pipeline搞清流水级事项

- 晚上田神讲解Linux移植、SoC设置相关内容(启动linux的cpu需求、Linux内核编译配置Kconfig等、Linux目录结构、设备树、U-Boot移植、SoC结构),只能说这玩意儿又多又杂,真自己钻研估计最好得看官方英文文档,难顶

22/7/18

昨天是群魔乱舞了,就是静不下心来。

今日下午久违的平静了下来,只能说icache照着原版重写了一下,对于指令的时序设计还是迷糊,卡了这么久;系统部分不能荒废,以后一半一半要保证。珍爱理智,远离b站。

22/7/19

每次小会都会让人精神一振,然而随之的又有放松,今天又浮躁又摸鱼(x

- 交流一下明确了一些事情,还需参考下dcache(_controller和_datapath)

- ubuntu上跑了遍perf_test;想打算生成下相关test的golden_trace文件,此次契机下才切实体会soft目录中书写、编译生成指令和导入vivado的流程,也了解了些tcl使用和vivado仿真时的具体进程和命令

22/7/20

本身若每天抓紧阅读core代码现在应该比较熟悉核然后加好icache指令了吧,当然这又是老样子的后话了;pyq今天似乎还是ICPC亚洲总决赛,又想起曾经对算法竞赛的痴想(然后b站上看了看19的ACM直播),但反正时间都更愿意花在摸鱼上,所以自己的能力越来越不得劲儿。这次loongson绝不能拖后腿

- 看了一点data_cache_controller.sv的代码,先按自己的想法写吧,头疼的还是时序和接口;CP0缺了TagLo寄存器,且加上后需考虑cache和mfc0的指令冲突(producer:

cache-> consumer:mfc0,是cache写操作倒和icahce没太大关系;mtc0->cache则是在PageGrain寄存器冲突),译码的各信息含义尚不明 - 有新的更重要的任务,于是又开始阅读各接口控制器文章,之后需配合田学长工作,为各队做外设接口维护

22/7/21

- 借哲哥询问的契机,了解了遇险防护指令(

sync、synci、eret等);新架构inst_info_t相关阅读追踪到score_board转发AT表上;关注接口控制器IP - 早上就动工了,下午上工迟缓,晚上还是受了大影响;卡西米尔的剧情永远诙谐而引人共鸣,罗伊莫妮卡好甜;阿尼亚わくわく

22/7/22

- 阅读了解I2C总线协议,小有所获;不过关于控制器的IP核究竟怎么获取维护抱有疑惑

- 阅读完score_board相关逻辑,下一步是读execute_pipe模块,要串起控制数值

22/7/23

- 尝试查看了MAC控制器,没多少收获(没看多少)

- 阅读了execute_pipe部分,并总算理解了preDecoder中tWB1和tWB2的含义(分别对用ex级可写回,和dex级可写回,一个处理ALU运算一个延迟ALU);inst_cache指令有写的具体想法了

22/7/24

还是间接性摸鱼,哀其意志之不坚

- 终于是查看了清华nontrivial-mips的设计文档,有些收获,但更多的是对自己浪费时间的恐惧

- 方案:inst_cache的第一级检测到cache_cmd时,进入exec,内部状态机开始运作,flow_en被置0外部流水终止直至相应cache操作结束(学习miss的处理方式)

22/7/25

一句话,还得靠一些手段让自己能几乎按自我意志进入“投入”的状态,之后就没事了。

- 下午总算是把inst_cache内部指令通路写完了,打算接到有tlb的版本上先测无指令的,再加上解码相关模块测有指令的;不过似乎已经先复用了data_cache,这个inst_cache倒是可有可无,但测还是要测一下,然后data_cache要把它好好给看一看懂

- 晚上在哲哥的指导下终于是用vivado跑起了vcs仿真(仿真了下soc_up的tb,明天尝试导入gzrom.bin),又对vivado和vcs的真实结构有了深一些的了解;感觉良好又充实,果然自己对短期直接需求可以保持百分百投入,一旦接下长期任务并且没有及时的需求监督就会摸起鱼来。

22/7/26

- gzrom.bin加到spi_flash模块的初始化中去了,不过仿真好像没有预期的输出反应

- 阅读了nand flash的原理和接口,倒是和之前sdram有所联系;重新了解了nmos以及verilog中该类原语的使用

22/7/27

- 又装了vivado2020.2,虚拟机已经扩容到150GB了,本机容量清理了很久,勉强够用了;gparted分区设置时新发现,被截断(顺序)的分区不能扩展,嗯这很物理;

- 晚上田学长的上板与跑操作系统指导,受益匪浅,只是没有开发板板后面内容就不是太清楚了

之后至结束

- 返校,做一些上板验证,毕竟后来拿到了板子(很好玩)

- 写tcl script脚本方便快速测试——中道崩殂;本身龙芯提供了官方的script,再者vcs那块各种参数/步骤尚未完全了解,找来的Makefile未改完

- SoC上增加VGA控制器通路,linux添加相应配置(设备树等),调试(AXI总线理解问题,控制器没用上id和last信号便忘记回传,导致cpu卡住;未解之谜--设备树读取的结果大小端相反,最后是姑且手动换了大小端解决的,但不知原因);如此耽误了其他外设和应用添加/调试的时间

- 添加framebuffer read/write通路,不过没有用上的需求

- 基于litenes项目进行移植,输出改为直接写framebuffer;不过似乎由于该模拟器本身实现不佳,最后在自己cpu上运行帧率感人,便没用上(幸好没用上,后来翻往届答辩ppt发现这个litenes似乎就是18年龙芯杯南大的产物),换成了infones,似乎本身就是针对framebuffer移植好的,跑起来很流畅,马里奥很好玩

- 展示、答题、答辩相关协助,总之只能尽自己微薄之力了

一等奖纯属意外,多亏队长、队员和学长的带带,本人有挂件之嫌;还得广泛涉猎提高水平早日独当一面

Loongson Log的更多相关文章

- X86上搭建交叉工具链,来给龙芯笔记本编译本地工具链(未完待续)

故事的背景是,我买了一台龙芯2F的笔记本来装B. 为什么说是装B呢?因为不但操作系统是Linux,而且CPU还是龙芯的. 一般人有这么酷的装备吗?简直是装B大圣啊. 这里一定要申明一点,本人不是IT技 ...

- X86给龙芯笔记本编译本地工具链(未完待续)

我买了一台龙芯2F的笔记本来当玩具. 买回来发现,这台笔记本上没法安装软件,因为既没有软件仓库,也没有GCC. 因此需要构建交叉工具链和构建本地工具链. 下面是我研究如何搞定着一切的笔记. 工具链组件 ...

- 如何正确使用日志Log

title: 如何正确使用日志Log date: 2015-01-08 12:54:46 categories: [Python] tags: [Python,log] --- 文章首发地址:http ...

- UWP开发之Mvvmlight实践七:如何查找设备(Mobile模拟器、实体手机、PC)中应用的Log等文件

在开发中或者后期测试乃至最后交付使用的时候,如果应用出问题了我们一般的做法就是查看Log文件.上章也提到了查看Log文件,这章重点讲解下如何查看Log文件?如何找到我们需要的Packages安装包目录 ...

- const let,console.log('a',a)跟console.log('a'+a)的区别

const 创建一个只读的常量 let块级作用域 const let重复赋值都会报错 console.log('a',a) a console.log('a'+a) a2 逗号的值会有空格:用加号的值 ...

- CYQ.Data V5 从入门到放弃ORM系列:教程 - Log、SysLogs两个日志类使用

Log 静态类介绍: Public Static (Shared) Methods GetExceptionMessage 获取异常的内部信息 WriteLogToDB Overloaded. 将日志 ...

- your password has expired.to log in you must change it

今天应用挂了,log提示密码过期.客户端连接不上. 打开mysql,执行sql语句提示密码过期 执行set password=new password('123456'); 提示成功,但客户端仍然连接 ...

- console.log("A"-"B"+"3")=?

(点击上方的订阅号,可快速关注,关注有惊喜哦^_^) 前不久看到一道JS基础题目,做了一下竟然错了一半...在此分享一下: 先把题目放上来,大家可以自己测试一下再看答案哦^_^ ①console.lo ...

- 监视EntityFramework中的sql流转你需要知道的三种方式Log,SqlServerProfile, EFProfile

大家在学习entityframework的时候,都知道那linq写的叫一个爽,再也不用区分不同RDMS的sql版本差异了,但是呢,高效率带来了差灵活性,我们 无法控制sql的生成策略,所以必须不要让自 ...

- 关于Quartz.NET作业调度框架的一点小小的封装,实现伪AOP写LOG功能

Quartz.NET是一个非常强大的作业调度框架,适用于各种定时执行的业务处理等,类似于WINDOWS自带的任务计划程序,其中运用Cron表达式来实现各种定时触发条件是我认为最为惊喜的地方. Quar ...

随机推荐

- 不为人知的网络编程(十八):UDP比TCP高效?还真不一定!

本文由LearnLHC分享,原始出处:blog.csdn.net/LearnLHC/article/details/115268028,本文进行了排版和内容优化. 1.引言 熟悉网络编程的(尤其搞实时 ...

- IIS通过URL重写配置http跳转https,排除部分域名

<rewrite> <rules> <rule name="http to https" stopProcessing="true" ...

- vue的element,el-select与el-tree配合使用,实现下拉树状

HTML <el-select ref="stlectTree" v-model="treeSelectText" placeholder="请 ...

- Redis 实战篇——Redis 客户端(Jedis,Luttece,Redisson)

一.Jedis,Redisson,Lettuce三者的区别 共同点:都提供了基于Redis操作的Java API,只是封装程度,具体实现稍有不同. 不同点: 1.1.Jedis 是Redis的Java ...

- 压力测试-jmeter-copy

1. 场景描述 新申请的服务器,要压测下python算法程序最多能执行多少条数据,有几年没用压力测试工具-jmeter了,重新下载了最新版本,记录下,也希望能帮到准备使用jmeter做压测的朋友. 2 ...

- Mysql死锁问题如何排查和解决

Mysql 查询是否存在锁表有多种方式,这里只介绍一种最常用的. 1.查看正在进行中的事务SELECT * FROM information_schema.INNODB_TRX2.查看正在锁的事务SE ...

- linux:shell

关于shell 什么是shell? shell,是用c编写的,既是命令语言,也是一种程序设计语言 shell指一种应用程序,该程序提供一个界面,用户可通过该界面访问操作系统 什么是脚本? 脚本是一条文 ...

- 《SpringBoot》自动装配原理(简单易懂)

引入 先看SpringBoot的主配置类 @SpringBootApplication public class DemoApplication{ public static void main(St ...

- args = parser.parse_args()报错 解决

args = parser.parse_args()报错 解决 问题: 如题. 解决方法: args = parser.parse_args(args=[]) args = parser.parse_ ...

- 所生成项目的处理器架构“MSIL”与 “x86”不匹配

在 .net 生成时如果修改过某个类库的平台目标,那么通常会出现下面的警告: 之所以产生这个问题是因为类库的"平台目标"不统一,如果选择了 x86, 那么解决方案中所有的项目都应设 ...