04-Verilog基础_3

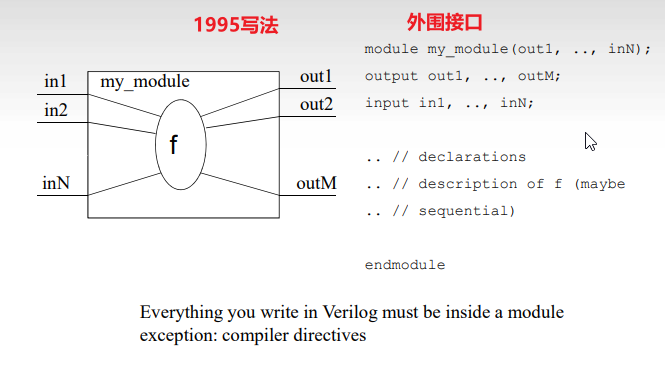

Module

Module是verilog中的关键字,是对电路建模的最小单元。verilog中构建一个电路,对于一个硬件进行描述在module中进行。

半加器

module half_adder(S,C,A,B);

output S,C;

input A,B;

wire S,C,A,B;

assign S = A ^ B;

assign C = A & B;

endmodule

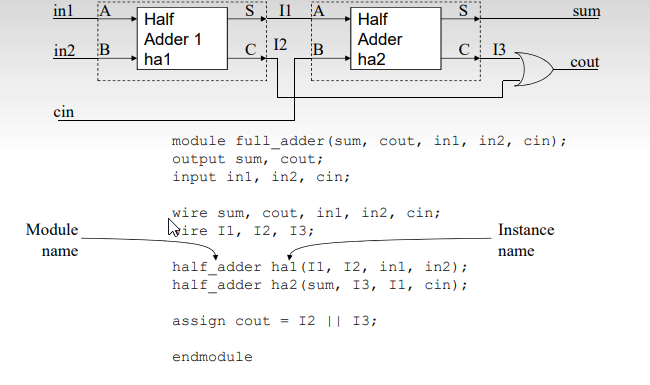

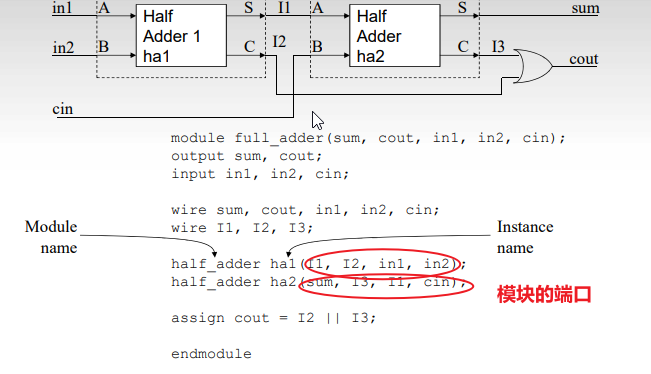

全加器

module full_adder(sum,cout,in1,in2,cin);

output sum,cout;

input in1,in2,in3;

wire sum,cout,in1,in2,cin;

half_adder ha1(I1,I2,in1,in2);

half_adder ha2(sum,I3,I1,cin);

assign cout = I2 || I3;

endmodule

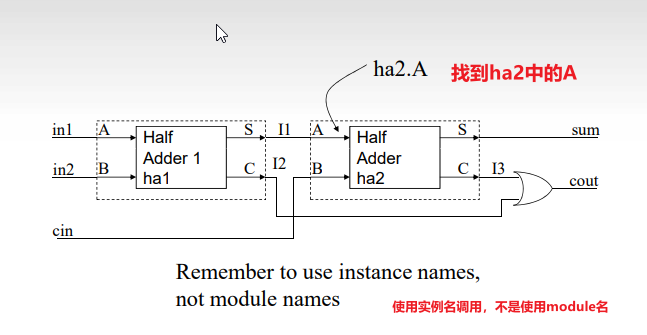

Hierachical Names

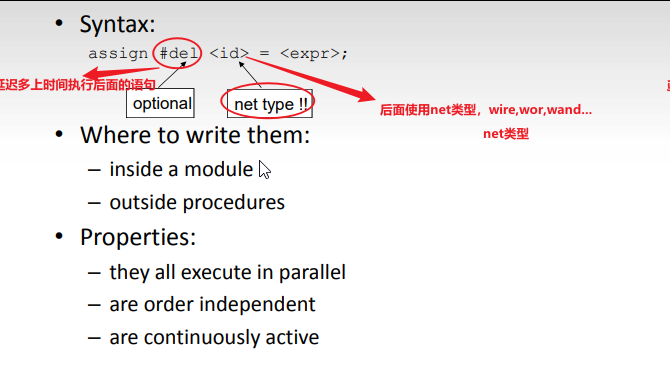

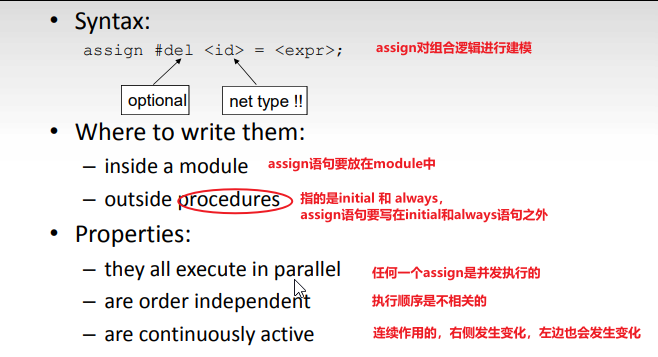

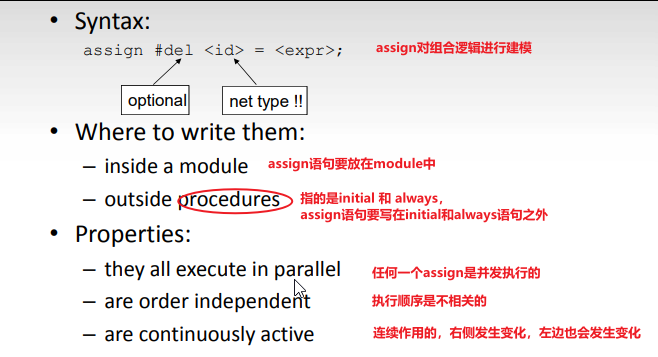

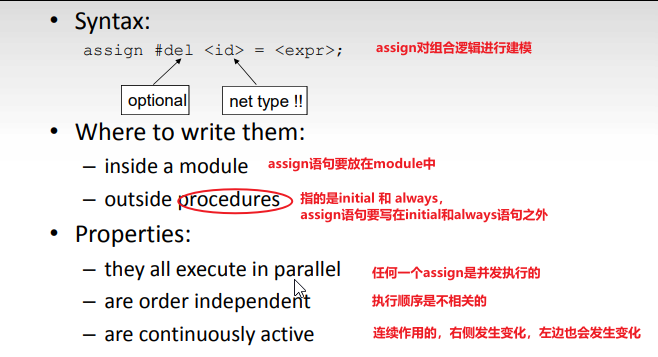

Continuous Assignments(连续赋值语句)

- 将左侧和右侧连起来,建立连接关系

- 线网类表示逻辑门与模块之间的连接,具体的类型有:wire、wand、wor、tri、triand、trior、tri0、tri1、trireg、uwire、supply0、supply1

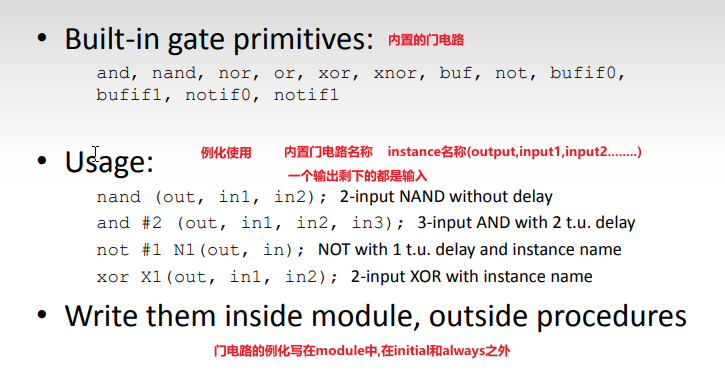

Structural Model(Gate Level)

- 组合逻辑电路是没有DFF的,触发器如何描述,取决于综合逻辑工具。

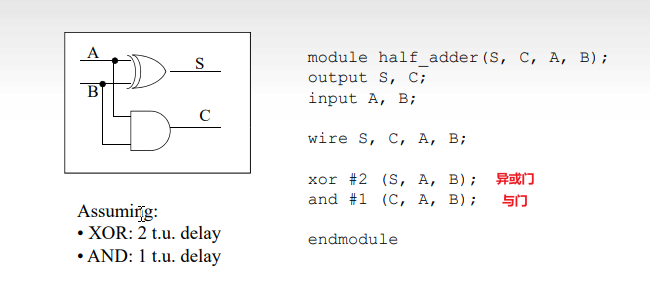

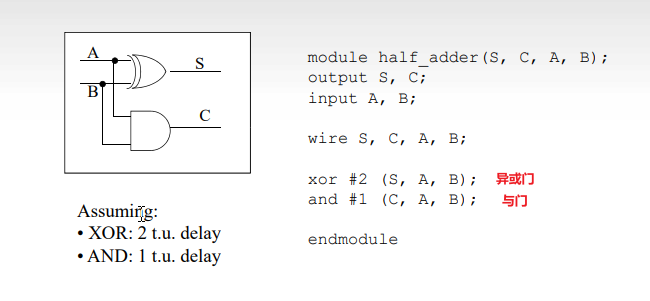

半加器的实现

- 使用verilog中的门电路实现半加器

module half_adder(S,C,A,B);

output S,C;

input A,B;

wire S,C,A,B;

xor #2 (S,A,B);

and #1 (C,A,B);

endmodule

- 这种门电路的实现是不推荐的,这里的门电路相当于将RTL代码进行逻辑综合之后映射到特定工艺库中的东西。

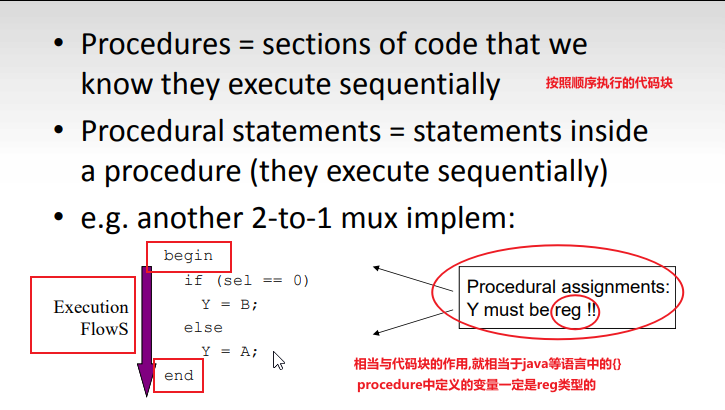

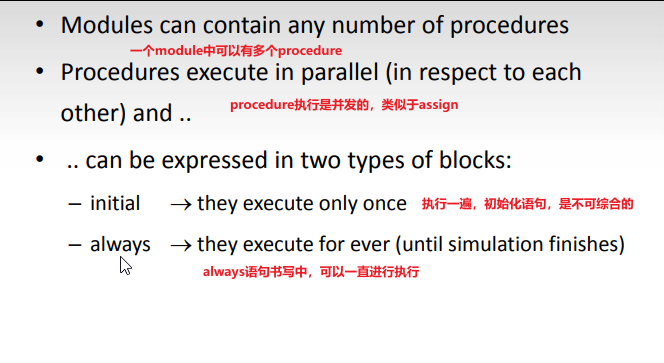

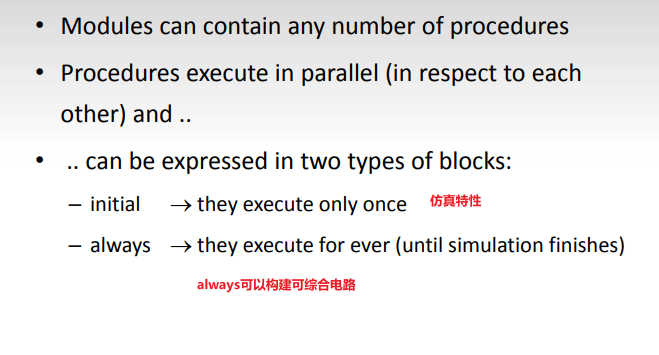

Behavioral Model-Procedure(i)

- 实现二选一的mux

begin

if(sel == 0)

Y = B;

else

Y = A;

end

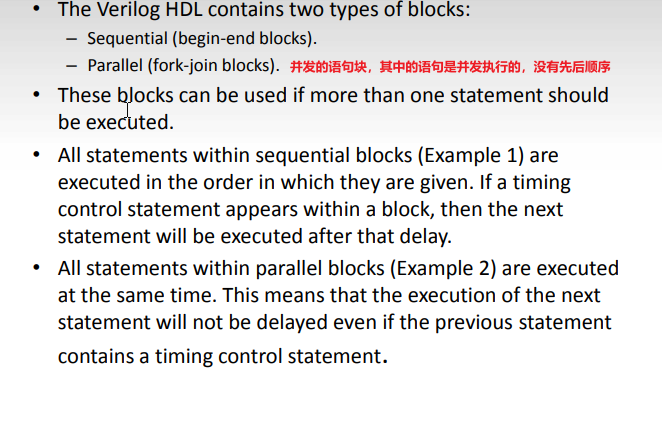

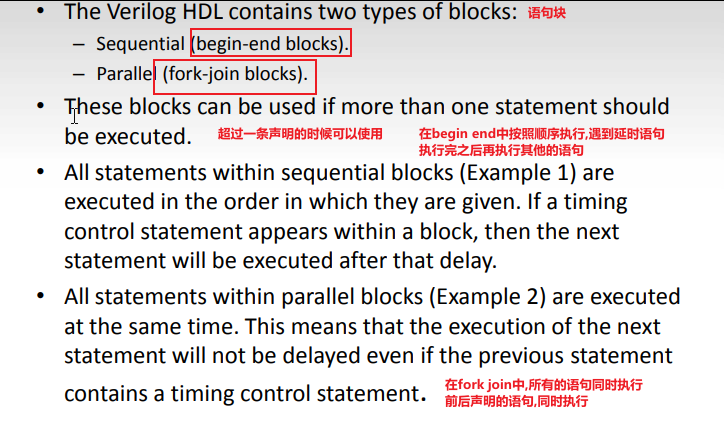

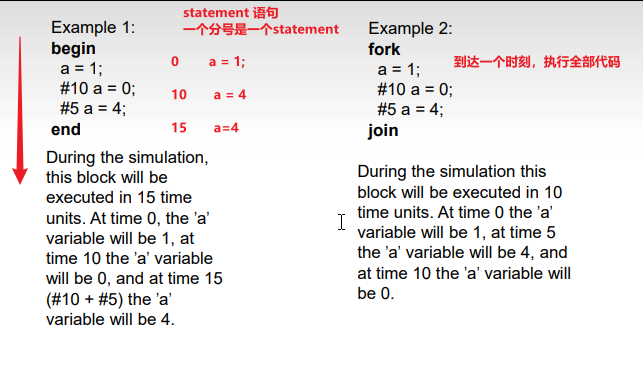

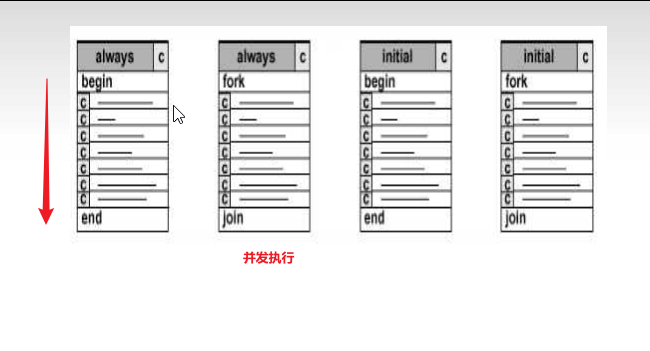

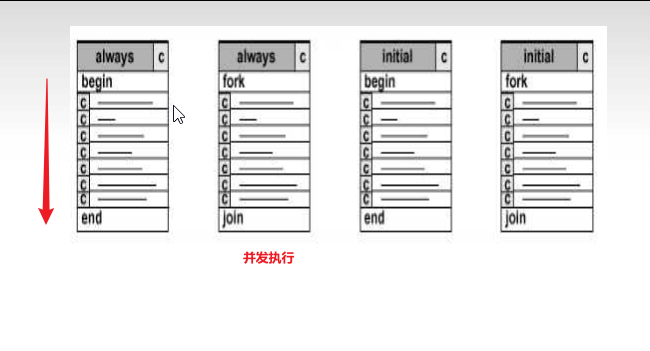

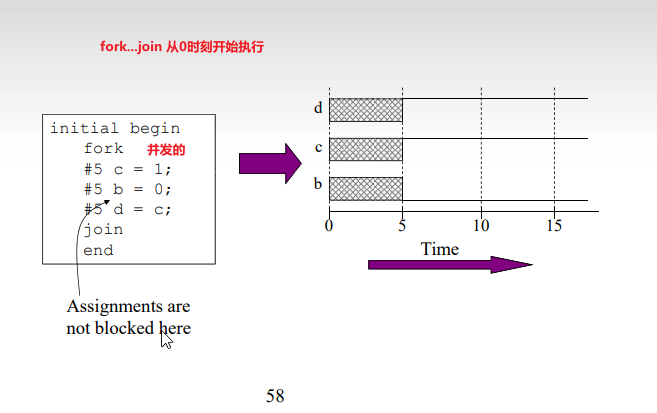

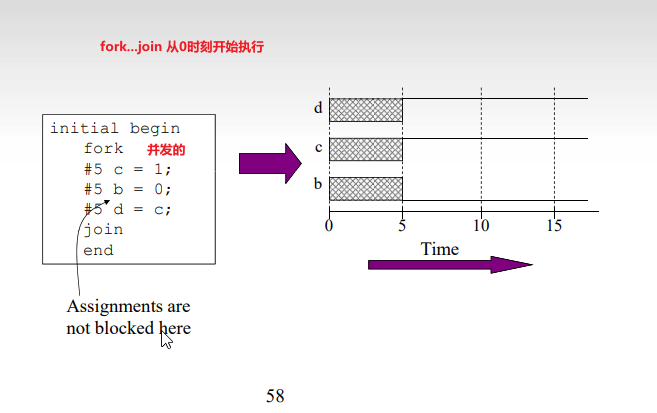

Block statement

- fork-join是不可综合的,不能用于构建电路

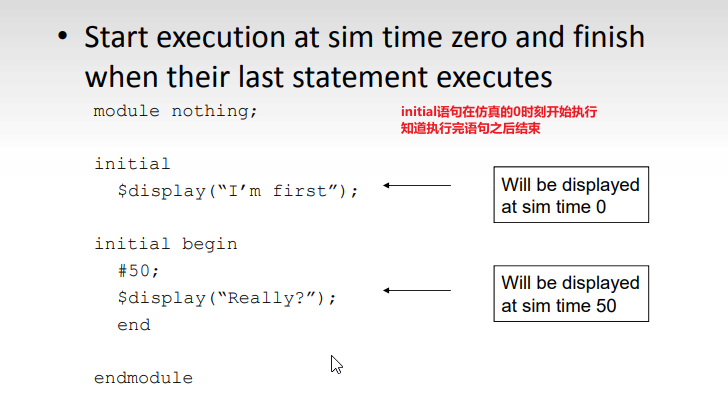

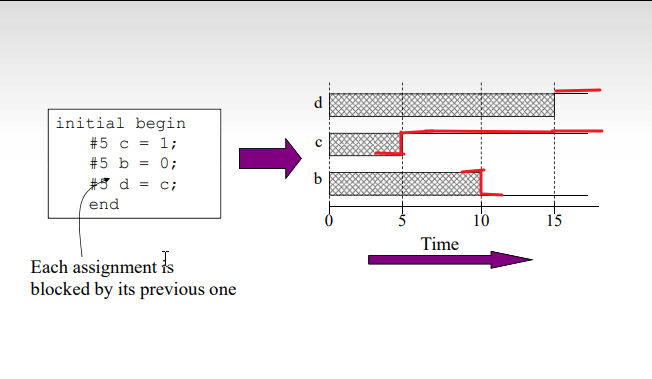

Initial & Always

- @--等的意思

event

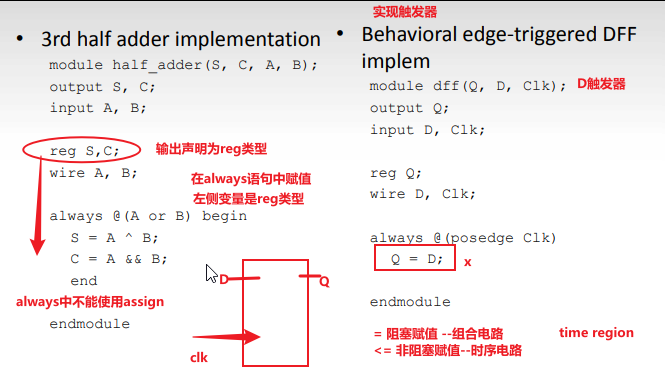

半加器实现--always语句

- 半加器和DFF

// half adder

module half_adder(S,C,A,B);

output S,C;

input A,B;

reg S,C;

always @(A or B){

S = A ^ B;

C = A && B;

}

endmodule

//DFF

module dff(Q,D,Clk);

output Q;

input D,Clk;

reg Q;

wire D,Clk;

always @(posedge Clk){

Q = D; //这里这种写法是错误的,应该使用非阻塞赋值写法

}

endmodule

Timing

- verilog语言中特有的

if

四选一mux实现

// 4-to-1 mux

module mux 4_1(out,in,sel);

output out;

input [3:0] in;

input [1:0] sel;

reg out;

wire in,sel;

always @(in or sel)

if(sel == in[0])

out = in[0];

else if(sel == in[1]

out = in[1];

else if(sel == in[2]

out = in[2];

else

out = in[3];

endmodule

- 还可以使用三目运算符

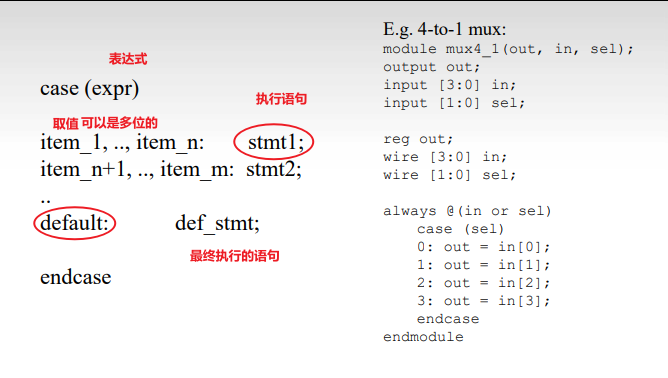

case

实现四选一

module mux 4_1(out,in,sel);

output out;

input [3:0] in;

input [1:0] sel;

reg out;

wire [3:0] in;

wire [1:0] sel;

always @(in or sel)

case (sel)

2'b00 : out = in[0];

2'b01 : out = in[1];

2'b10 : out = in[2];

2'b11 : out = in[3];

endcase

endmodule

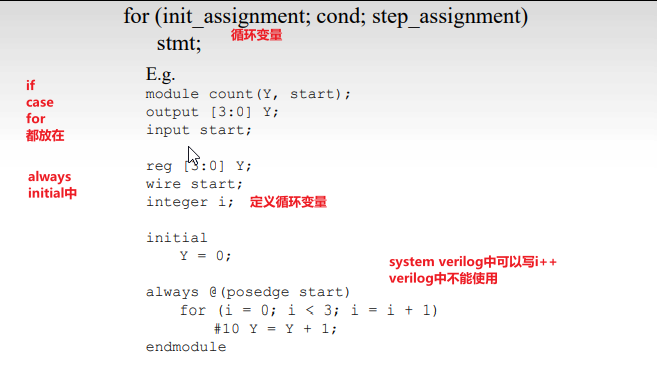

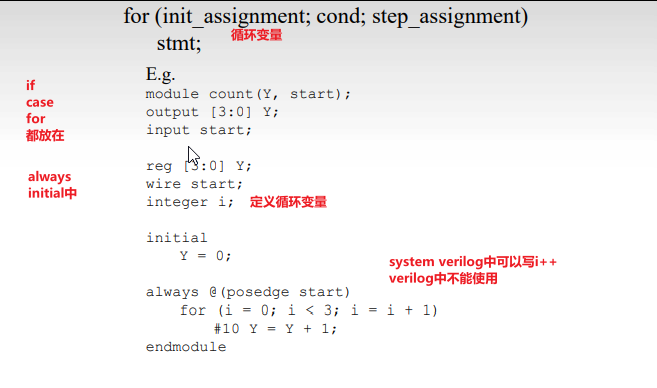

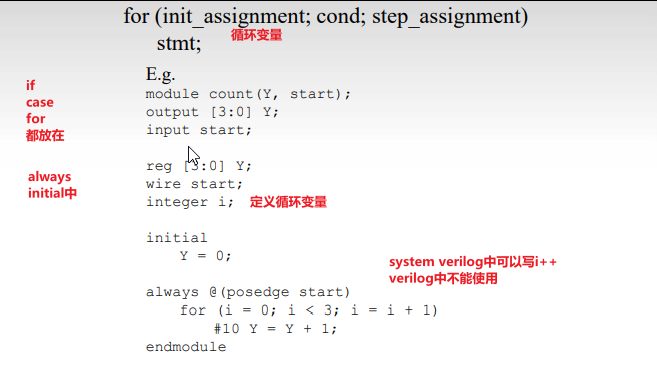

for

- 可以实现计数器

module count(Y,start);

output [3:0] Y;

input start;

reg [3:0] Y;

wire start;

integer i;

initial

Y = 0;

always @(posedge start)

for(i = 0;i < 3;i = i+1)

#10 Y = Y + 1

endmodule

- for循环是不是可综合的,取决于循环变量是不是固定的

while

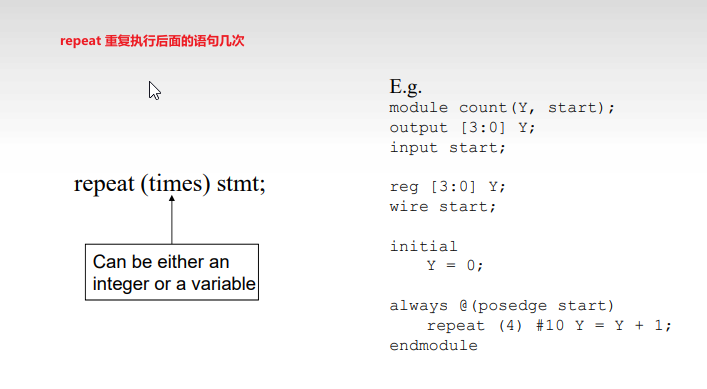

repeat

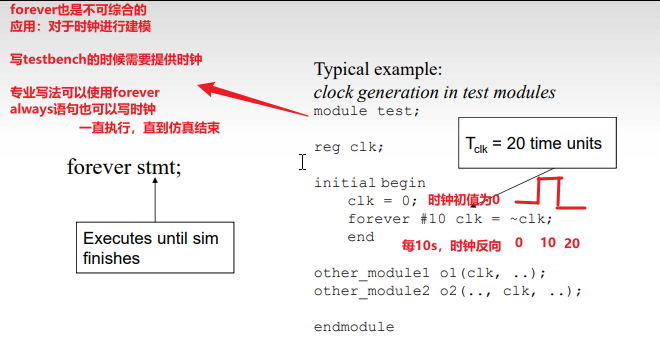

forever

- 时钟建模

module test;

reg Clk;

initial begin

clk = 0;

foever #10 clk = ~clk;

end

other_module o1(clk,....);

other_module o2(...,clk,...);

endmodule

04-Verilog基础_3的更多相关文章

- Verilog基础入门——Vivado工程创建(三)

Verilog基础入门--Vivado工程创建(三) Vivado是Verilog语言的一个集成环境,目前使用的版本为英文版,简单介绍一下在Vivado中创建一个工程并写入源文件 [配置] win10 ...

- [分享]Ubuntu12.04安装基础教程(图文)

[分享]Ubuntu12.04安装基础教程(图文) 原文地址: http://teliute.org/linux/Ubsetup/lesson21/lesson21.html 1.进入 live cd ...

- 【第一季】CH06_FPGA设计Verilog基础(三)

[第一季]CH06_FPGA设计Verilog基础(三) 一个完整的设计,除了好的功能描述代码,对于程序的仿真验证是必不可少的.学会如何去验证自己所写的程序,即如何调试自己的程序是一件非常重要的事情. ...

- 【第一季】CH05_FPGA设计Verilog基础(二)Enter a post title

[第一季]CH05_FPGA设计Verilog基础(二) 5.1状态机设计 状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路.通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态 ...

- 【第一季】CH04_FPGA设计Verilog基础(一)Enter a post title

[第一季]CH04_FPGA设计Verilog基础(一) 4.1 Verilog HDL 代码规范 u 项目构架设计 项目的构架用于团队的沟通,以及项目设计的全局把控 u 接口时序设计规范 模块和模块 ...

- [Java 教程 04] Java基础语法

在上一篇文章中我们已经运行了个简单的java程序,但是没有给大家讲解代码部分的内容与含义.学习,我们要做到知其然而知其所以然,所以本篇文章我们就来讲解java程序的基本语法,学完这篇文章你再回头看上篇 ...

- DLL技术应用04 - 零基础入门学习Delphi47

DLL技术应用04 让编程改变世界 Change the world by program 利用DLL实现窗体重用 利用 Delphi 的 DLL 功能,不但能够实现过程和函数重用,而且还可以实现窗体 ...

- 04: linux基础总结

目录: 1.1 Red Hat Linux 安装及服务控制 1.2 目录和文件管理 1.3 安装及管理程序 1.4 账号和权限管理 1.5 磁盘和文件管理 1.6 进程和计划任务管理 1.7 Linu ...

- System Verilog基础(二)

这一篇笔记主要记录Procedural,Process,Task and function,Interface和Communication中值得注意的点. 1.Procedural 写testbenc ...

- Verilog 基础回顾 (一)

Verilog 大小写敏感,且所有关键字都是小写 1 寄存器 register = storage,是数据存储单元的抽象,可视为能够存储数值的变量 (variable that can hold v ...

随机推荐

- python操作elasticsearch-全文检索、拼写纠错、补全提示

1.首先安装elasticsearch包 pip install elasticsearch (一般会包含新旧版本,如果想要特定的版本,比如5.x 可以在后面加5数字) ""&qu ...

- bash shell笔记整理——linux时钟和hwclock命令

Linux中的时钟 在linux中,分为了如下两种时钟: 系统时钟:由linux内核通过CPU的工作频率进行的计时. 硬件时钟:主板上的cmos芯片时钟,就是可以在bios中设定的时间.(RTC,re ...

- bash shell笔记整理——外部命令和内部命令区别

linux命令的类别: 外部命令 内部命令 什么是内部命令 bash shell程序内部自带的命令. 什么是外部命令 不是bash shell内建命令,bash会根据用户给定的命令从PATH环境变量中 ...

- 数字孪生结合GIS会为智慧农业带来怎样的改变?

数字孪生是一种创新的技术,它通过将现实世界的物理实体与数字模型相结合,实现了实时.动态的仿真和预测.而地理信息系统(GIS)则是一种用于收集.管理.分析和展示地理数据的工具.当这两种技术相互融合时,将 ...

- NetSuite 开发日记:如何管理多环境自定义列表值

在 NetSuite 中可以创建自定义列表,列表可用于为其他(自定义)记录上的下拉选项列表值. var rec = record.create({ type: 'customrecord_xx' }) ...

- ElasticSearch之Get index settings API

获取指定索引的参数的值. 获取指定索引的全部参数,命令样例如下: curl -X GET "https://localhost:9200/testindex_002/_settings?pr ...

- 如何使用Redisson实现分布式锁?

在分布式系统中,当多个线程(或进程)同时操作同一个资源时,为了保证数据一致性问题,所以就需要一种机制来确保在同一时间只有一个线程(或进程)能够对资源进行修改,这就是分布式锁的作用. 分布式锁是一种在分 ...

- Ubuntu 命令使用方法

apt-get 用作于deb包 yum作用于tar包(也可以运作于rpm包) 首先用yum list wget检查一下你的虚拟机有没有安装wget,如果安装了下面图中会显示 @dvd ,我的没有安装所 ...

- VisionPro学习笔记(6)——如何使用QuickBuild

如果需要了解其他图像处理的文章,请移步小编的GitHub地址 传送门:请点击我 如果点击有误:https://github.com/LeBron-Jian/ComputerVisionPractice ...

- docker: 'buildx' is not a docker command

解决方法 sudo apt install docker-buildx-plugin