USB中TOKEN的CRC5与CRC16校验(神奇的工具生成Verilog实现)

USB2.0IP设计

最近,在学习USB2.0IP的设计,其中包含了CRC校验码的内容,之前学习千兆以太网曾经用到过CRC32校验(https://www.cnblogs.com/Xwangzi66/p/14185143.html),CRC详细原理可见括号的链接,今天则从怎么用工具快速生成Verilog代码的角度介绍。

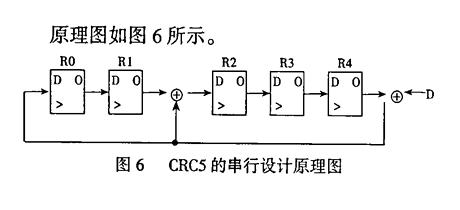

一 确定CRC5的多项式

G(X)= X^5 + X^2 + 1,输入数据的位宽为11bit,即CRC5中的输入信号[10:0]data_i.

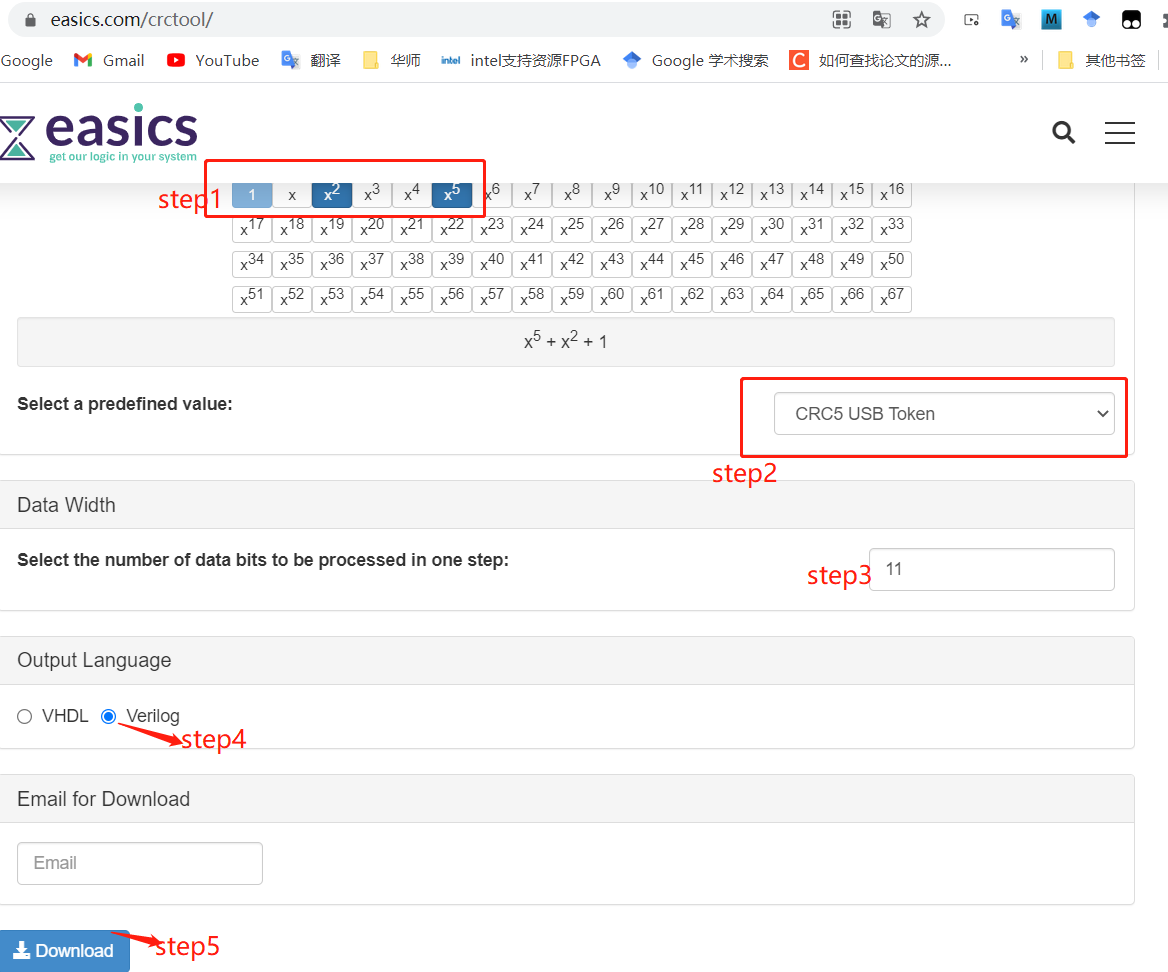

二 在线网页生成CRC5的Verilog代码

链接如下:https://www.easics.com/crctool/

在线生成CRC5校验代码如下图:第一步是确定多项式,此处是CRC5的多项式。第二步选择CRC的类别,如CRC16,CRC32等。第三步,选择待校验数据的位宽。第四步,选择输出的编程语言,用Verilog实现。第五步,下载打开就。注意填好邮箱,此处为了保护本人隐私则空着。

2.在线工具生成CRC5的Verilog代码

1 module CRC5_D11;

2

3 // polynomial: x^5 + x^2 + 1

4 // data width: 11

5 // convention: the first serial bit is D[10]

6 function [4:0] nextCRC5_D11;

7

8 input [10:0] Data;

9 input [4:0] crc;

10 reg [10:0] d;

11 reg [4:0] c;

12 reg [4:0] newcrc;

13 begin

14 d = Data;

15 c = crc;

16

17 newcrc[0] = d[10] ^ d[9] ^ d[6] ^ d[5] ^ d[3] ^ d[0] ^ c[0] ^ c[3] ^ c[4];

18 newcrc[1] = d[10] ^ d[7] ^ d[6] ^ d[4] ^ d[1] ^ c[0] ^ c[1] ^ c[4];

19 newcrc[2] = d[10] ^ d[9] ^ d[8] ^ d[7] ^ d[6] ^ d[3] ^ d[2] ^ d[0] ^ c[0] ^ c[1] ^ c[2] ^ c[3] ^ c[4];

20 newcrc[3] = d[10] ^ d[9] ^ d[8] ^ d[7] ^ d[4] ^ d[3] ^ d[1] ^ c[1] ^ c[2] ^ c[3] ^ c[4];

21 newcrc[4] = d[10] ^ d[9] ^ d[8] ^ d[5] ^ d[4] ^ d[2] ^ c[2] ^ c[3] ^ c[4];

22 nextCRC5_D11 = newcrc;

23 end

24 endfunction

25 endmodule

三 修改成自己USB的IP设计的CRC5校验模块

通过在线工具生成后,自己可以修改模块名,输入输出信号名,寄存器名,以更好地用在自己的FPGA项目中,本人CRC5修改如下:

1 module usbh_crc5

2 (

3 input [4:0] crc_i,

4 input [10:0] data_i,

5 output [4:0] crc_o

6 );

7

8 //-----------------------------------------------------------------

9 // Implementation

10 //-----------------------------------------------------------------

11 assign crc_o[0] = data_i[10] ^ data_i[9] ^ data_i[6] ^ data_i[5] ^ data_i[3] ^ data_i[0] ^

12 crc_i[0] ^ crc_i[3] ^ crc_i[4];

13

14 assign crc_o[1] = data_i[10] ^ data_i[7] ^ data_i[6] ^ data_i[4] ^ data_i[1] ^

15 crc_i[0] ^ crc_i[1] ^ crc_i[4];

16

17 assign crc_o[2] = data_i[10] ^ data_i[9] ^ data_i[8] ^ data_i[7] ^ data_i[6] ^ data_i[3] ^ data_i[2] ^ data_i[0] ^

18 crc_i[0] ^ crc_i[1] ^ crc_i[2] ^ crc_i[3] ^ crc_i[4];

19

20 assign crc_o[3] = data_i[10] ^ data_i[9] ^ data_i[8] ^ data_i[7] ^ data_i[4] ^ data_i[3] ^ data_i[1] ^

21 crc_i[1] ^ crc_i[2] ^ crc_i[3] ^ crc_i[4];

22

23 assign crc_o[4] = data_i[10] ^ data_i[9] ^ data_i[8] ^ data_i[5] ^ data_i[4] ^ data_i[2] ^

24 crc_i[2] ^ crc_i[3] ^ crc_i[4];

25

26 endmodule

通过修改后,代码更简洁高效,更方便调用,直接在USB中调用即可!

后续的CRC16的Verilog实现,同CRC5生成方法一样,先用在线工具生成,再修改一些模块名,输入输出信号即可。

CRC16代码如下:

1 module usbh_crc16

2 (

3 input [15:0] crc_i,

4 input [7:0] data_i,

5 output [15:0] crc_o

6 );

7

8 //-----------------------------------------------------------------

9 // Implementation

10 //-----------------------------------------------------------------

11 assign crc_o[15] = data_i[0] ^ data_i[1] ^ data_i[2] ^ data_i[3] ^ data_i[4] ^

12 data_i[5] ^ data_i[6] ^ data_i[7] ^ crc_i[7] ^ crc_i[6] ^

13 crc_i[5] ^ crc_i[4] ^ crc_i[3] ^ crc_i[2] ^

14 crc_i[1] ^ crc_i[0];

15 assign crc_o[14] = data_i[0] ^ data_i[1] ^ data_i[2] ^ data_i[3] ^ data_i[4] ^ data_i[5] ^

16 data_i[6] ^ crc_i[6] ^ crc_i[5] ^ crc_i[4] ^

17 crc_i[3] ^ crc_i[2] ^ crc_i[1] ^ crc_i[0];

18 assign crc_o[13] = data_i[6] ^ data_i[7] ^ crc_i[7] ^ crc_i[6];

19 assign crc_o[12] = data_i[5] ^ data_i[6] ^ crc_i[6] ^ crc_i[5];

20 assign crc_o[11] = data_i[4] ^ data_i[5] ^ crc_i[5] ^ crc_i[4];

21 assign crc_o[10] = data_i[3] ^ data_i[4] ^ crc_i[4] ^ crc_i[3];

22 assign crc_o[9] = data_i[2] ^ data_i[3] ^ crc_i[3] ^ crc_i[2];

23 assign crc_o[8] = data_i[1] ^ data_i[2] ^ crc_i[2] ^ crc_i[1];

24 assign crc_o[7] = data_i[0] ^ data_i[1] ^ crc_i[15] ^ crc_i[1] ^ crc_i[0];

25 assign crc_o[6] = data_i[0] ^ crc_i[14] ^ crc_i[0];

26 assign crc_o[5] = crc_i[13];

27 assign crc_o[4] = crc_i[12];

28 assign crc_o[3] = crc_i[11];

29 assign crc_o[2] = crc_i[10];

30 assign crc_o[1] = crc_i[9];

31 assign crc_o[0] = data_i[0] ^ data_i[1] ^ data_i[2] ^ data_i[3] ^ data_i[4] ^ data_i[5] ^

32 data_i[6] ^ data_i[7] ^ crc_i[8] ^ crc_i[7] ^ crc_i[6] ^

33 crc_i[5] ^ crc_i[4] ^ crc_i[3] ^ crc_i[2] ^

34 crc_i[1] ^ crc_i[0];

35

36 endmodule

Crc16 Code

总结,一直都是根据多项式,确定硬件电路的形式,然后查表,如V3学院千兆以太网的CRC32校验教程,很繁琐,得理解原理,今天意外知道一种新的方法,通过在线工具生成Verilog实现:

USB中TOKEN的CRC5与CRC16校验(神奇的工具生成Verilog实现)的更多相关文章

- 最详细易懂的CRC-16校验原理(附源程序)(转)

最详细易懂的CRC-16校验原理(附源程序) from:http://www.openhw.org/chudonganjin/blog/12-08/230184_515e6.html 最详细易懂的CR ...

- 最详细易懂的CRC-16校验原理(附源程序)

from:http://www.openhw.org/chudonganjin/blog/12-08/230184_515e6.html 最详细易懂的CRC-16校验原理(附源程序) 1.循环校验码( ...

- C# 实现CRC16校验

前言 本文将使用一个NuGet公开的组件技术来实现CRC16校验功能,提供了一些简单的API,来方便的实现. 在Visual Studio 中的NuGet管理器中可以下载安装,也可以直接在NuGet控 ...

- CRC-16校验原理

最详细易懂的CRC-16校验原理(附源程序) 1.循环校验码(CRC码): 是数据通信领域中最常用的一种差错校验码,其特征是信息字段和校验字段的长度可以任意选定. 2.生成CRC码的基本原理: 任意一 ...

- Delphi CRC16校验算法实现(转)

循环冗余码校验英文名称为Cyclical Redundancy Check,简称CRC.它是利用除法及余数的原理来作错误侦测(Error Detecting)的.实际应用时,发送装置计算出CRC值并随 ...

- 基于Modbus三种CRC16校验方法的性能对比

目录 1.背景介绍 2. CRC校验的三种方法 2.1. 直接计算CRC校验 2.2. 查短表法计算CRC16校验 2.3.查大表法计算CRC16校验 3.三种校验方式的测试方法 3.1.直接计算CR ...

- 讨论两种Redis中Token的存储方式

摘要:本文讨论一个问题:存储token时,token与对应用户id谁来作为key? 问题起源问题起源于要给公司的后台管理系统添加权限管理,选用的是开源框架shiro,而原本系统上是采用token做了登 ...

- usb中的传输模式

别人总结的一个usb传输模式,保存一下 usb中的endpoint(端点)和传输模式 端点: 端点位于USB 外设内部,所有通信数据的来源或目的都基于这些端点,是一个可寻址的FIFO. 每个USB 外 ...

- struts2中token防止重复提交表单

struts2中token防止重复提交表单 >>>>>>>>>>>>>>>>>>>&g ...

随机推荐

- Crackme_003

功能: 拿到文件,先执行一下.功能如下: 1.nag窗口 会先出现如下nag窗口,持续几秒 2.注册窗口: 出现错误会提示:You Get Wrong Try Again 破解: 1.查壳: 无壳, ...

- SHA256sum系列命令检测文件完整性

1 sha256sum sha256sum是一个检测文件完整性的命令,一般下载的文件都会附带一个哈希值,使用sha256sum计算下载文件的哈希值再与目标哈希值比较即可确定文件是否完整,类似的命令还有 ...

- 16. Vue2.4+新增属性$attrs

vm.$attrs简介 首先我们来看下vue官方对vm.$attrs的介绍: 包含了父作用域中不作为 prop 被识别 (且获取) 的特性绑定 (class 和 style 除外).当一个组件没有声明 ...

- Java代理简述

1.什么是代理? 对类或对象(目标对象)进行增强功能,最终形成一个新的代理对象,(Spring Framework中)当应用调用该对象(目标对象)的方法时,实际调用的是代理对象增强后的方法,比如对功能 ...

- ASP.NET CORE使用WebUploader对大文件分片上传,并通过ASP.NET CORE SignalR实时反馈后台处理进度给前端展示

本次,我们来实现一个单个大文件上传,并且把后台对上传文件的处理进度通过ASP.NET CORE SignalR反馈给前端展示,比如上传一个大的zip压缩包文件,后台进行解压缩,并且对压缩包中的文件进行 ...

- 微信小程序底部实现自定义动态Tabbar

多图警告!!! 最近在工作中遇到这样一个需求:微信小程序底部的Tab需要通过判断登录人的角色动态进行改变,想要实现这个功能依靠小程序原生的Tabbar是不可能实现的了,所以研究了一下自定义Tab,这里 ...

- shellcode隐写到像素RGB免杀上线到CS

利用把Shellcode隐写到图片像素RGB进行免杀上线到CS --by:chenw 0x01 前言 前几天跟一个朋友一起搞一个站的时候,发现那个站点开了很多杀软,使用CS的powershell马无法 ...

- 1026 Table Tennis

A table tennis club has N tables available to the public. The tables are numbered from 1 to N. For a ...

- 1075 PAT Judge

The ranklist of PAT is generated from the status list, which shows the scores of the submissions. Th ...

- 【ORM】Mybatis与JPA的区别

Mybatis与JPA的区别: 1.ORM映射不同: Mybatis是半自动的ORM框架,提供数据库与结果集的映射: JPA(Hibernate)是全自动的ORM框架,提供对象与数据库的映射: 2.可 ...