第一章 MIZ701 VIVADO 搭建SOC最小系统HelloWorld

本章内容是MIZ701中的第五章,本来也是要过渡一下FPGA部分的,但是由于MIZ701没有单独提供PL部分的晶振时钟,时钟必须通过PS产生,所以本章内容作为Miz701的第一章内容。本章的目的是搭建一个最小的SOC系统,并且测试串口输出,千兆以太网回路测试。本章先让PS部分搭建最小系统,这样可以从PS部分获取到时钟,然后为后面章节中PL部分提供时钟源。

1.0本章难度系数★★☆☆☆☆☆

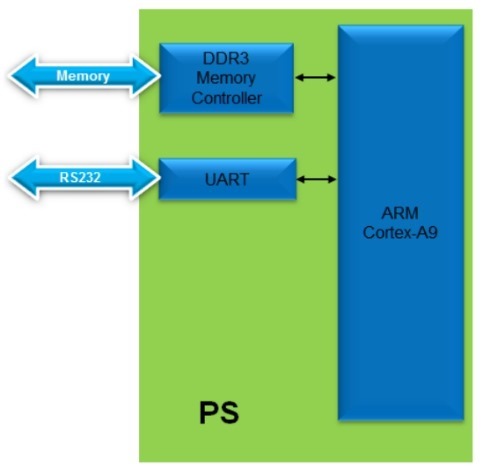

1.1最小系统分析

这张图展示了我们需要构建的最小系统。并且下面的嵌入式实验会基于这个最小系统进行添加外设。

本实验中将会只使用到PS部分资源包括了ARM Cotrex-A9、 DDR3内存、一个UART串口。这就是我们的最小系统。首先我们程序会加载到DDR内存中,然后CPU一条一条执行,那么执行的情况我们可以通过串口打印观察。

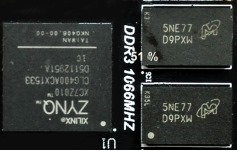

1.2板子使用的硬件

红色线框内就是本次实验需要用到的资源,分别为CPU XC7Z010、2片512MB内存、一个Micro接口的USB 转 UART,内存型号实际焊机MT41K256M16RE-125 M

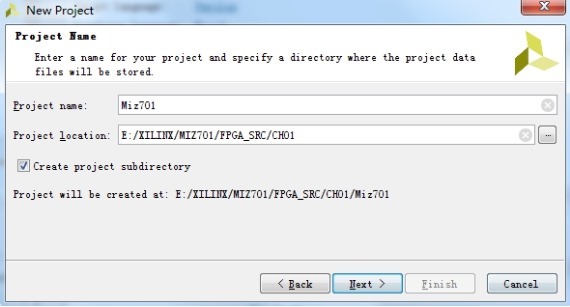

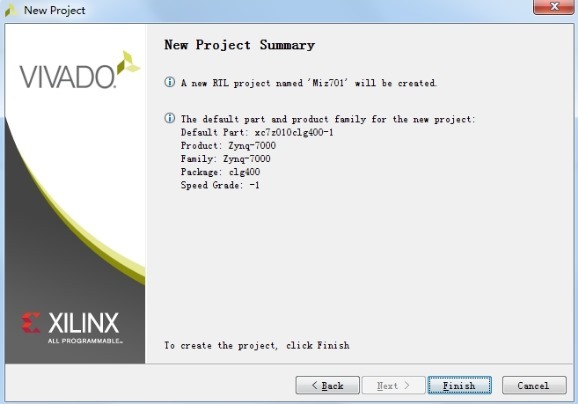

1.3新建一个VIVADO工程

Step1:新建一个名为为Miz701的工程

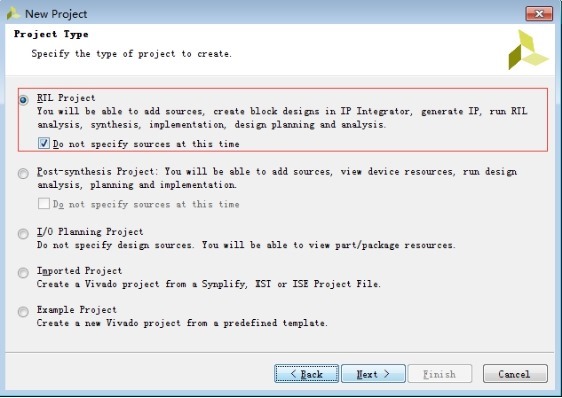

Step2:

Step3:

Step4:

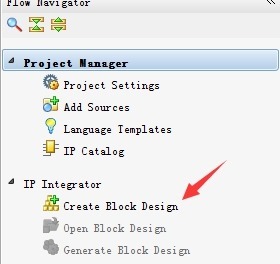

1.4使用IP Integrator创建硬件系统

Step1:单击Create Block Design

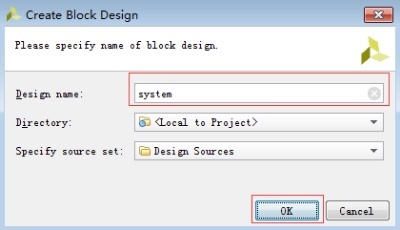

Step2:输入system

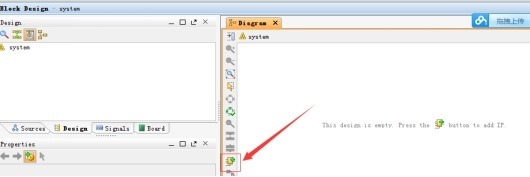

Step3:单击下图中 添加IP按钮

添加IP按钮

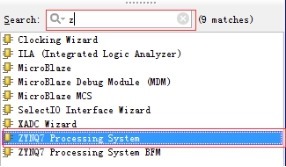

Step4:搜素单词z选择ZYNQ7 Processing System,然后双击

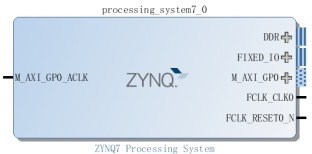

Step5:添加进来了ZYNQ CPU IP,然后双击下图

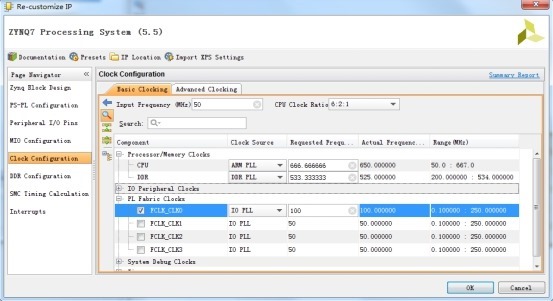

Step6:修改时钟输入为50MHZ,可以看到ARM时钟为650MHZ DDR为525MHZ(1050MHZ),并且修改FCLK_CLK0 为100MHZ

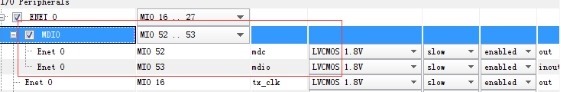

Step7:修改MIO的配置 修改IO电压,增加ENT0 和UART1接口,下面会测试这2个接口,之后单机OK.

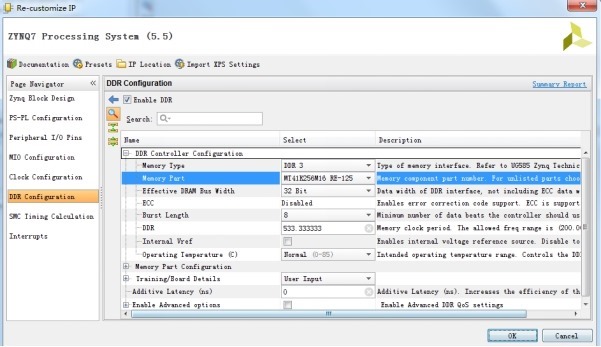

Step8:修改内存型号为MT41K256M16RE-125 M

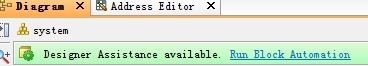

Step9:单机Run Block Automation 进行自动连线,VIVADO软件会根据信号的命名规则智能连线。

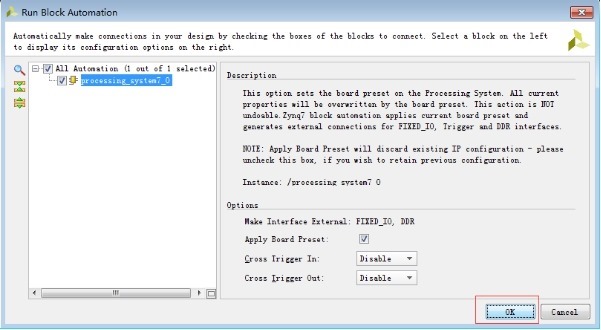

Step10:勾选如下,直接单机OK

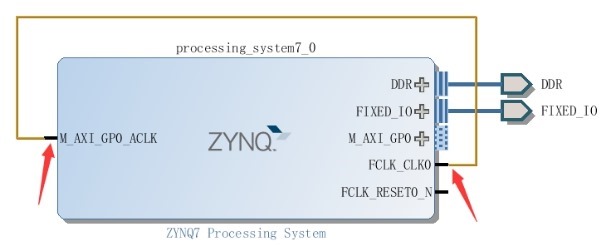

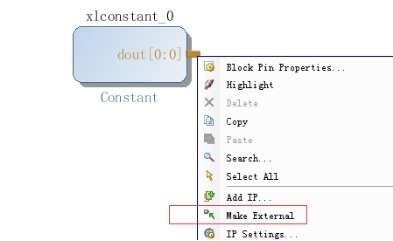

Step11:在你点击了OK后,你会发现DDR以及FICED_IO自劢的延伸出来,然后把时钟FCLK_CLK0和M_AXI_GPI0_ACLK连接。方法:当把鼠标靠近的时候会自动连接。

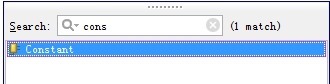

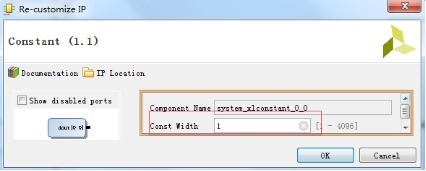

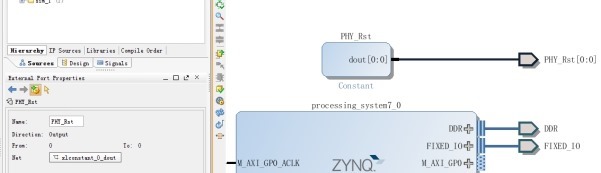

Step12:为了让以太网PHY RTL8211E-VL可以工作,必须让其复位PIN脚设置为1,只要简单添加一个常量IP并且映射到PL部分的PIN脚(复位脚在FPGA 部分(PL)),和添加CPU方法一样

Step13:双击设置常量为1

Step14:右击PIN脚选择Make External

Step15:取个有意义的名字如下图,只要单击相应的模块就可以在右手边修改

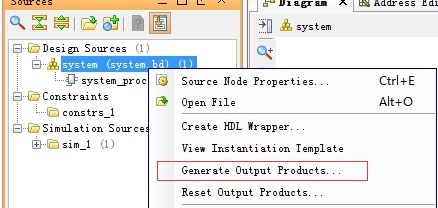

Step16: 右击 system.bd, 单击Generate Output Products

Step17:支部操作会产生执行、仿真、综合的文件,可以看出来最后的硬件设计步骤还是回到了我们前面的FPGA开发上来了。

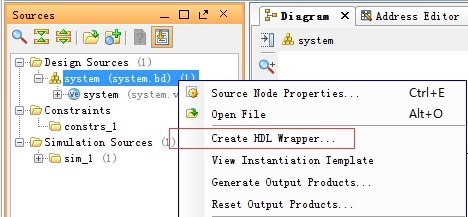

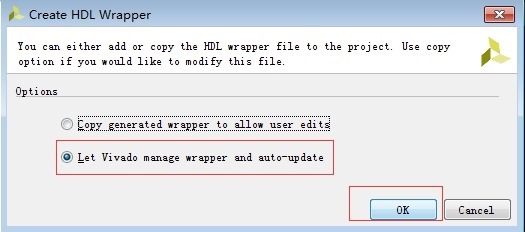

Step18:右击system.bd 选择 Create HDL Wrapper 这步的作用是产生顶层的HDL文件

Step19:选择Leave Let Vivado manager wrapper and auto-update 然后单击OK

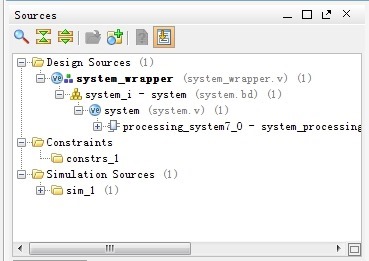

Step20:之后我看下源码的层次结构,可以看到system_wrapper.v就是顶层文件,调用了CPU.

Step21:查看system_wrapper.v源码

|

//Copyright 1986-2015 Xilinx, Inc. All Rights Reserved. //-------------------------------------------------------------------------------- //Tool Version: Vivado v.2015.4 (win64) Build 1412921 Wed Nov 18 09:43:45 MST 2015 //Date : Sun Aug 28 12:47:04 2016 //Host : Administrator running 64-bit Service Pack 1 (build 7601) //Command : generate_target system_wrapper.bd //Design : system_wrapper //Purpose : IP block netlist //-------------------------------------------------------------------------------- `timescale 1 ps / 1 ps module system_wrapper (DDR_addr, DDR_ba, DDR_cas_n, DDR_ck_n, DDR_ck_p, DDR_cke, DDR_cs_n, DDR_dm, DDR_dq, DDR_dqs_n, DDR_dqs_p, DDR_odt, DDR_ras_n, DDR_reset_n, DDR_we_n, FIXED_IO_ddr_vrn, FIXED_IO_ddr_vrp, FIXED_IO_mio, FIXED_IO_ps_clk, FIXED_IO_ps_porb, FIXED_IO_ps_srstb, PHY_Rst); inout [14:0]DDR_addr; inout [2:0]DDR_ba; inout DDR_cas_n; inout DDR_ck_n; inout DDR_ck_p; inout DDR_cke; inout DDR_cs_n; inout [3:0]DDR_dm; inout [31:0]DDR_dq; inout [3:0]DDR_dqs_n; inout [3:0]DDR_dqs_p; inout DDR_odt; inout DDR_ras_n; inout DDR_reset_n; inout DDR_we_n; inout FIXED_IO_ddr_vrn; inout FIXED_IO_ddr_vrp; inout [53:0]FIXED_IO_mio; inout FIXED_IO_ps_clk; inout FIXED_IO_ps_porb; inout FIXED_IO_ps_srstb; output [0:0]PHY_Rst; wire [14:0]DDR_addr; wire [2:0]DDR_ba; wire DDR_cas_n; wire DDR_ck_n; wire DDR_ck_p; wire DDR_cke; wire DDR_cs_n; wire [3:0]DDR_dm; wire [31:0]DDR_dq; wire [3:0]DDR_dqs_n; wire [3:0]DDR_dqs_p; wire DDR_odt; wire DDR_ras_n; wire DDR_reset_n; wire DDR_we_n; wire FIXED_IO_ddr_vrn; wire FIXED_IO_ddr_vrp; wire [53:0]FIXED_IO_mio; wire FIXED_IO_ps_clk; wire FIXED_IO_ps_porb; wire FIXED_IO_ps_srstb; wire [0:0]PHY_Rst; system system_i (.DDR_addr(DDR_addr), .DDR_ba(DDR_ba), .DDR_cas_n(DDR_cas_n), .DDR_ck_n(DDR_ck_n), .DDR_ck_p(DDR_ck_p), .DDR_cke(DDR_cke), .DDR_cs_n(DDR_cs_n), .DDR_dm(DDR_dm), .DDR_dq(DDR_dq), .DDR_dqs_n(DDR_dqs_n), .DDR_dqs_p(DDR_dqs_p), .DDR_odt(DDR_odt), .DDR_ras_n(DDR_ras_n), .DDR_reset_n(DDR_reset_n), .DDR_we_n(DDR_we_n), .FIXED_IO_ddr_vrn(FIXED_IO_ddr_vrn), .FIXED_IO_ddr_vrp(FIXED_IO_ddr_vrp), .FIXED_IO_mio(FIXED_IO_mio), .FIXED_IO_ps_clk(FIXED_IO_ps_clk), .FIXED_IO_ps_porb(FIXED_IO_ps_porb), .FIXED_IO_ps_srstb(FIXED_IO_ps_srstb), .PHY_Rst(PHY_Rst)); endmodule |

可以看到顶层文件的源码调用了CPU接口,所有外设的接口也都是通过顶层文件引出来的。

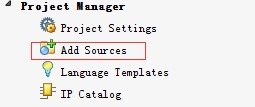

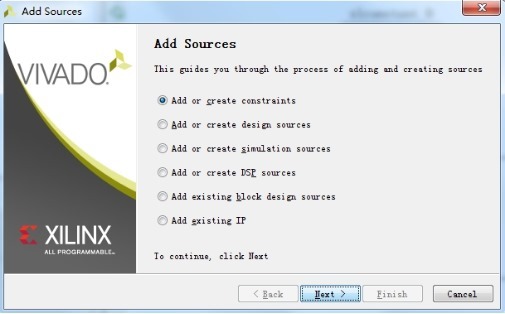

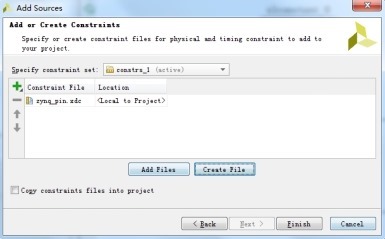

Step22:单机Add Sources

Step23:选择Add or create constraints

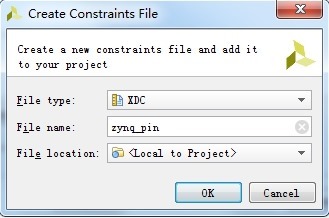

Step24:选择Create File

Step25:输入zynq_pin

Step26:如图,单击Finish

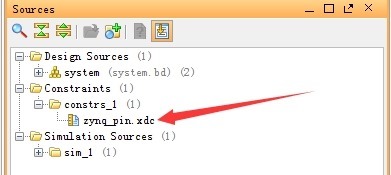

Step27:双击打开zynq_pin.xdc文件,添加PIN脚约束

Step28:双击打开zynq_pin.xdc文件,添加PIN脚约束

|

set_property PACKAGE_PIN E17 [get_ports PHY_Rst[0]] set_property IOSTANDARD LVCMOS33 [get_ports PHY_Rst[0]] |

Step25:执行->产生bit文件

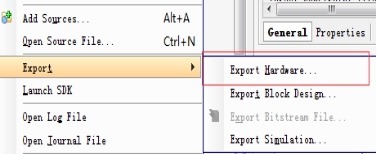

1.6导出SOC硬件到SDK

Step1:File->Export->Export Hardware

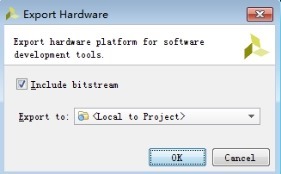

Step2:勾选Include bitstream 直接单击OK

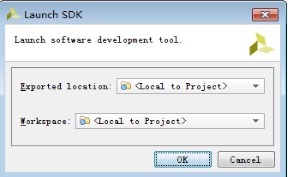

Step3:File->Launch SDK加载到SDK

Step4:单击OK

1.6 HelloWorld程序

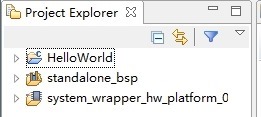

Step1:导出完成后如下图

1、硬件部分,这部分就是从VIVADO定制好的SOC硬件

2、这部分是硬件的地址空间分配

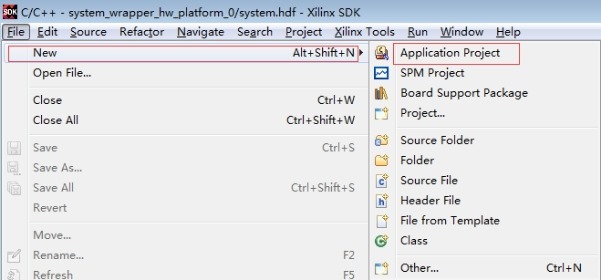

Step2:选择File->New->Application Project

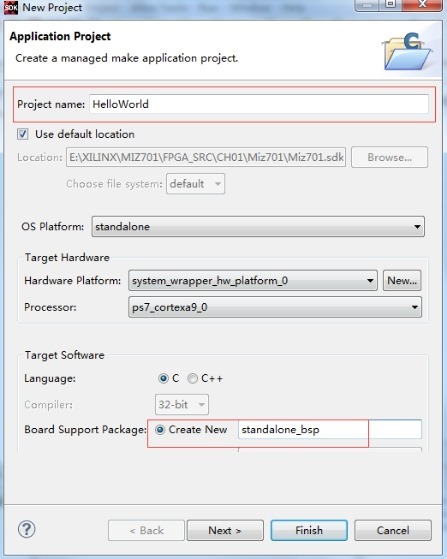

Step3:工程命名为HelloWorld,创建的bsp包取名为Miz702_bsp,然后单击NEXT

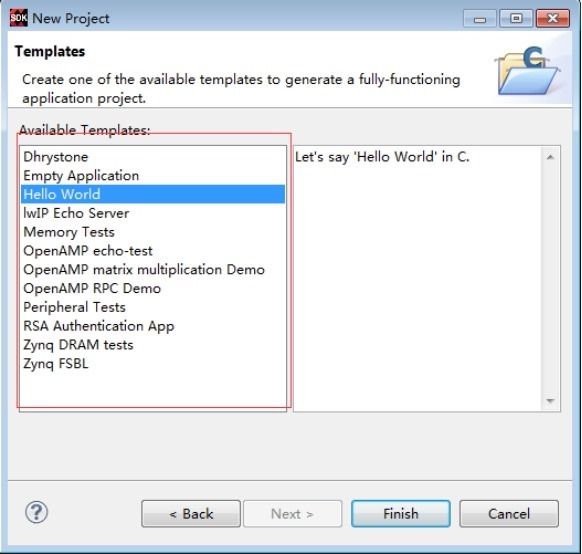

Step4:系统里面有很多自带的测试程序,本次就用自带的Helloworld程序做测试,单击Finish

Step5:完成后

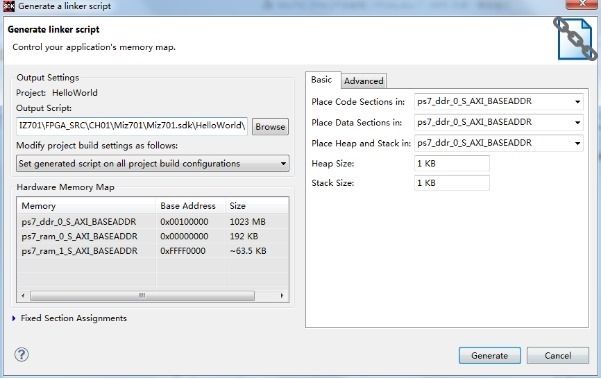

Step6:右击HelloWorld->Generate linker Script

Step7:可以看到所有可用内存的情况,代码、数据、堆栈运行所在内存的情况。不做人后改动,关闭。

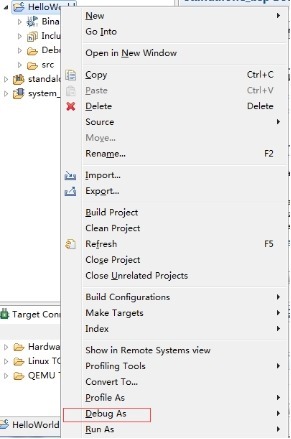

Step8:右击HelloWorld->

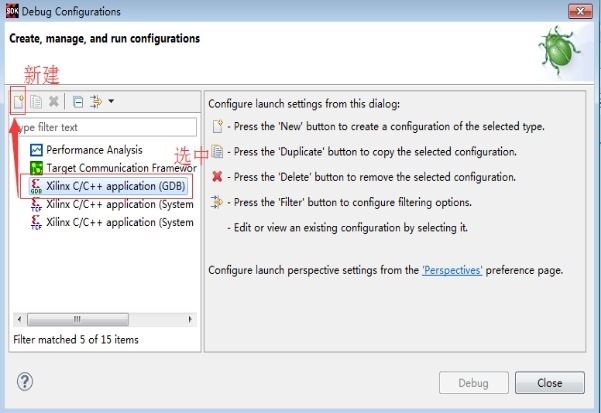

Step9:单击这个位置新建

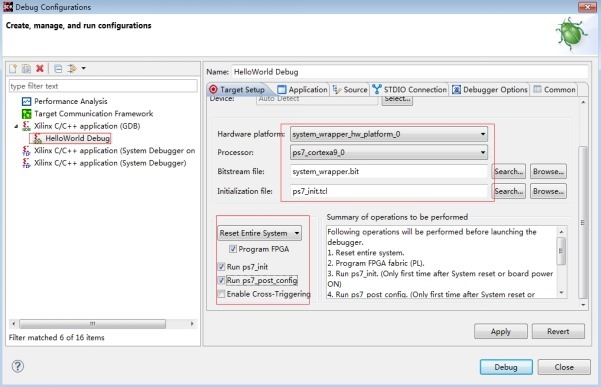

Step10:然后进行如下设置

Step10:然后进行如下设置

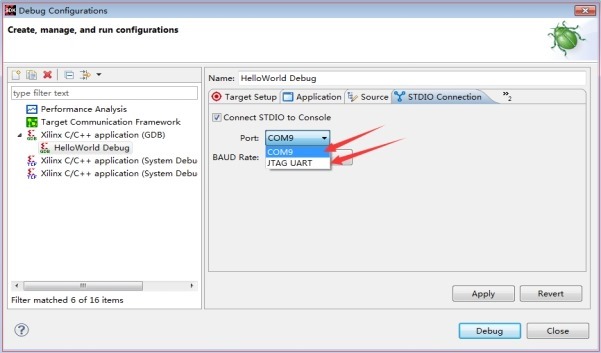

Step11:设置调试信息输出的端口可以到支持串口和JTAG方式,如果使用串口先确保串口已经接通到电脑,并且开发板已经通电。这里选择串口,这样可以测试我们的串口是否正常工作了。如果以后调试可以直接使用JTAG调试更加方便并且波特率设置到115200之后单击Apply。之后单击Debug(注意开发板必须通电,另外TF卡确保拔掉)

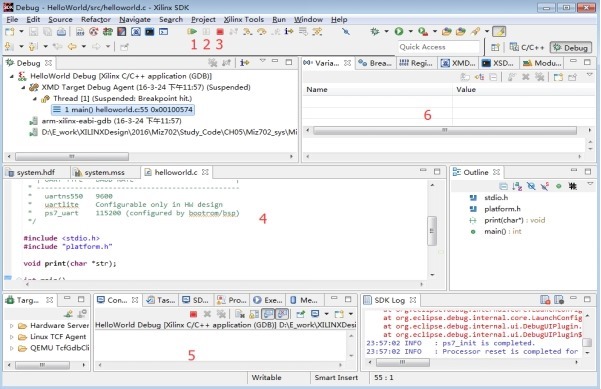

Step12:进入SDK调试界面

1、启动2、暂停3、停止4、代码5、信息控制台6、调试变量

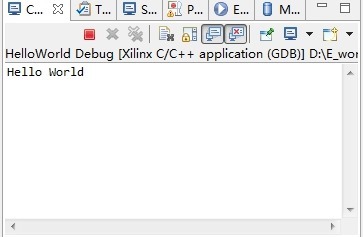

Step13:单击运行输出结果

1.7 MemTest内存测试程序

Step1:新建一个名为MemTest的工程

Step2:任然采用自带的测试函数测试

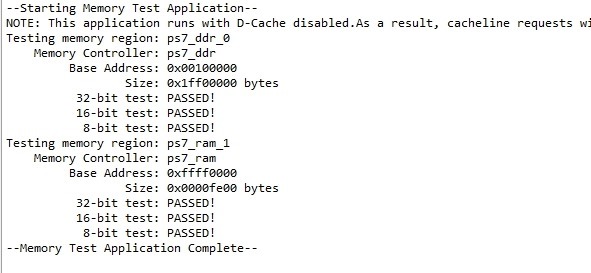

Step3:测试结果

1.8 DRAMTest内存测试程序

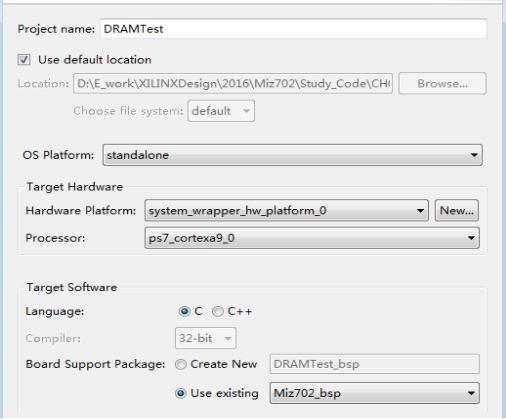

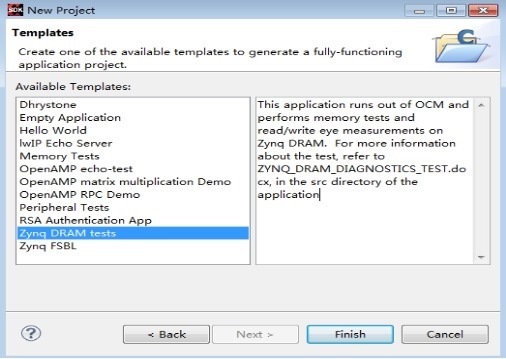

Step1:新建一个名为DRAMTest的工程

Step3:新建一个名为MemTest的工程

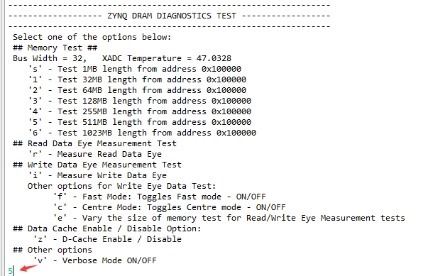

Step4:测试结果

根据提示可以在控制台中输入相关序号按回车进行(r,i测试会有一部分错误,还以和程序空间有关系)

1.9 LWIP协议对千兆网口测试

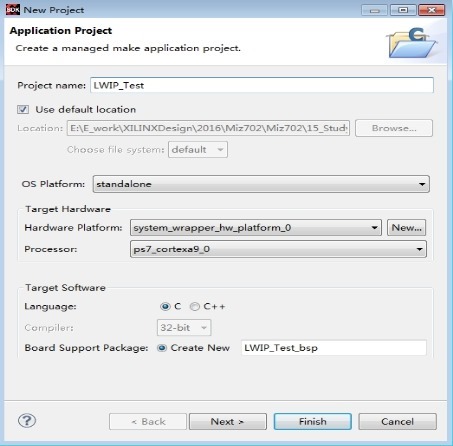

Step1:新建一个名为LWIP_Test的工程

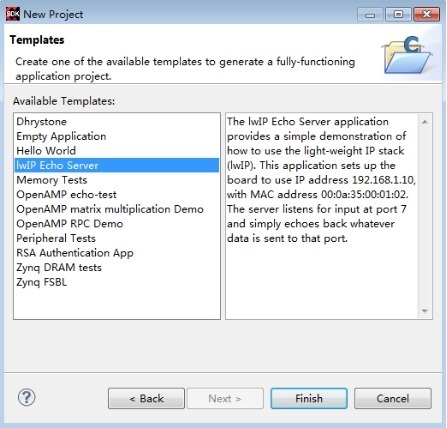

Step2:选择LWIP Echo Server 之后单击Finish

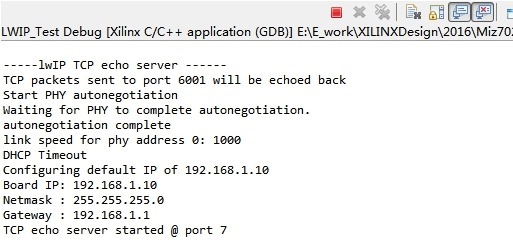

Step3:运行之后的串口打印信息

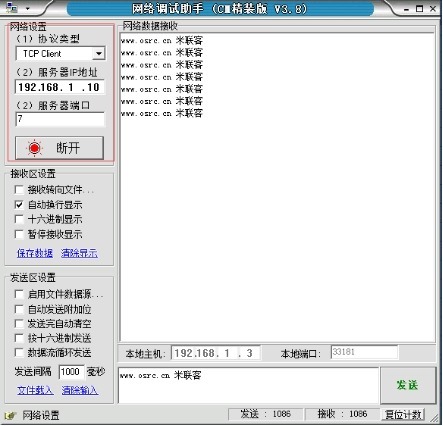

Step4:用网络助手实现回传测试

1.10使用快捷按钮调试

使用这两个图标,一个是debug一个是运行模式可以方便调试。

1.11 本章小结

本章详细讲解了定制一个SOC最小系统,并且运行了自带的HelloWorld工程、MemTest内存测试工程、DRAMTest内存测试工程、LWIP网络协议工程对千兆网口测试。本章让初学者可以搭建一个最小的SOC系统,并且教会读者利用软件自动的工程对SOC的基本外设进行测试。

第一章 MIZ701 VIVADO 搭建SOC最小系统HelloWorld的更多相关文章

- Zedboard学习(四):PS+PL搭建SoC最小系统 标签: fpgazedboardxilinxsoczynq 2017-07-07 15:58 7人阅读

zynq最核心的设计理念就是软件加硬件,即PS+PL.通过软硬件协同设计,结合了FPGA与双arm9内核,对于嵌入式拥有极大的优势. SoC:System on Chip的缩写,称为芯片级系统,也有称 ...

- 【菜鸟学习Linux】-第一章-Linux环境搭建-安装VMware虚拟机

本人菜鸟一个,刚毕业才上班2个月,现在用到Linux部署项目,这才开始学习Linux,以下是我在安装Linxu系统是遇到的一些问题,希望能给广大菜鸟们在学习的道路上提供帮助和指导,废话不多说!开工! ...

- 我的Android第一章:Android环境搭建

今天是Android第一天的学习,对于学习任何一门课程时我们都要对该课程要有基本的了解和认识,了解该课程学点什么内容,学了这门知识我门能够做些什么,这也是对于我们这些刚入门的学习人员来说是一个必须要弄 ...

- [OpenGL] 1、环境搭建及最小系统

>_<: 首先推荐一个企业版的VC6.0自带OpenGL和DirectX,非常方便:http://pan.baidu.com/s/1mgIAGi8 PS: 要注意这里的OpenGL建立的工 ...

- 一起来学Spring Cloud | 第一章 :如何搭建一个多模块的springcloud项目

在spring cloud系列章节中,本来已经写了几个章节了,但是自己看起来有些东西写得比较杂,所以重构了一下springcloud的章节内容,新写了本章节,先教大家在工作中如何搭建一个多模块的spr ...

- 第一章 用记事本搭建C#程序

1.新建记事本:using System;class Text{ Console.WriteLine("你好如鹏网"); Console.WriteLine("www.r ...

- 虚拟机上的Linux Java开发环境部署记录(VirtualBox+Ubuntu)第一章-基础环境搭建

创建虚拟机时需注意三点: 在BIOS中开启Intel VT,以支持64位虚拟机系统: 对于Ubuntu 16以上版本,至少分配10G以上初始控件. 增加一块网卡,选择Host-Only网络,用于主机和 ...

- 搭建CnetOS6.5x64最小系统及在线yum源的配置

CentOS系统作为红帽系列的一款linux系统,因为其免费.开源,在中小企业中得到了广泛应用,生产上为了更好的利用资源,都采用最小系统安装,因为一个图形界面都会占去系统资源的30%到40%,生产上一 ...

- 第一章 搭建Qt开发环境

第一章 搭建Qt开发环境 1.到http://download.qt-project.org/archive/上下载Qt的源码包.我下载的是qt-everywhere-opensource-src-4 ...

随机推荐

- 2016百度之星资格赛 Problem B(大数+组合数)

题意:度熊面前有一个全是由1构成的字符串,被称为全1序列.你可以合并任意相邻的两个1,从而形成一个新的序列.对于给定的一个全1序列,请计算根据以上方法,可以构成多少种不同的序列.最多200个1. 比如 ...

- 6.3 MRUnit写Mapper和Reduce的单元测试

1.1 MRUnit写单元测试 作用:一旦MapReduce项目提交到集群之后,若是出现问题是很难定位和修改的,只能通过打印日志的方式进行筛选.又如果数据和项目较大时,修改起来则更加麻烦.所以,在将 ...

- HTTP之持久连接

HTTP/1.1 允许 HTTP 设备在事务处理结束之后将 TCP 连接保持在打开状态,以便为未来的 HTTP 请求重用现存的连接.在事务处理结束后仍然保持在打开状态的 TCP 连接被称为持久连接.非 ...

- ionic serve 报【ionic-app-scripts' 不是内部或外部命令 】问题解

Error: Cannot find module 'E:\angular\ionic0515\node_modules\@ionic\app-scripts' at Function.Modu ...

- Redis | 一文轻松搞懂redis集群原理及搭建与使用

转载:https://juejin.im/post/5ad54d76f265da23970759d3 作者:SnailClimb 这里总结一下redis集群的搭建以便日后所需同时也希望能对你有所帮助. ...

- IP拨号器

是一个最终的接收者 package com.example.ip; import android.content.BroadcastReceiver; import android.content.C ...

- Qt编写安防视频监控系统9-自动隐藏光标

一.前言 这个效果的灵感来自于大屏电子看板系统,在很多系统中尤其是上了大屏的时候,其实在用户不在操作的时候,是很不希望看到那个鼠标箭头指针的,只有当用户操作的时候才显示出来,这个就需要开个定时器定时计 ...

- 使用VLC发送TS流与播放TS流

使用VLC发送TS流与播放TS流 一.如何使用VLC发送TS流 1.添加一个文件至VLC 2.选择串流,继续 3.选择UDP,点击添加 4.输入地址及端口 5.选择h.264+mp3(TS) 6.ne ...

- mongodb查询修改

//查 public StatisticsSchoolPracticeView findByUser(String userId,int statOrgType,int inDateType){ Qu ...

- swift 第十四课 可视化view: @IBDesignable 、@IBInspectable

以前应objctiew-c 写项目的时候,就知道有这两个关键字,现在用swift了.用法稍作改变,基本用法还是一致的 虽然使用这个之后,有时候会报错的非常的莫名其妙----(其实还是自己技术不够牛…… ...