FPGA 流水灯

VerilogHDL那些事儿_建模篇(黑金FPGA开发板配套教程)

作者:akuei2

说明:参照该书将部分程序验证学习一遍

学习时间:2014年5月2号

主要收获:

1. 对FPGA有初步了解;

2. 功能模块和控制模块;

3. 并行操作的思维;

4. 使用"并行操作"进行流水灯实验。

FPGA是什么?

1. 一个很好的比喻是:FPGA是"一堆乐高积木",而Verilog是"搭积木的手"。FPGA并没有实际的形状,要通过Verilog描述出形状来。

2. 新手们常常忽略了,FPGA其实是并存着"顺序操作"和"并行操作"的操作概念。如果打从一开始就忽略了它们,往后的日子很难避免遇见瓶颈。

过程赋值和assign连续赋值:

1. 过程赋值改变一个寄存器的状态,是时序逻辑,用在initial和always里面;

2. 连续赋值是组合逻辑,驱动线型变量(wire)。

流水灯实验:

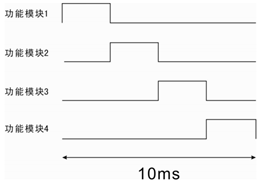

1. 系统整体模块以及每个功能模块示意图:

2. RTL原理图

RTL(寄存器传输级):描述数据在寄存器之间怎么流动和如何处理这些数据的模型。

3. 控制模块为top_module,功能模块有led1_module~led4_module。

module top_module(CLK, RSTn, LED_Out);

input CLK;

input RSTn;

output [3:0]LED_Out;

wire LED1_Out;

led1_module U1

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED1_Out)

);

wire LED2_Out;

led2_module U2

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED2_Out)

);

wire LED3_Out;

led3_module U3

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED3_Out)

);

wire LED4_Out;

led4_module U4

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED4_Out)

);

assign LED_Out = {LED4_Out, LED3_Out, LED2_Out, LED1_Out};

endmodule

module led1_module(CLK, RSTn, LED_Out);

input CLK;

input RSTn;

output LED_Out;

parameter T10MS = 2'd3;

reg[1:0]Count1;

always@(posedge CLK or negedge RSTn)

if(!RSTn)

Count1 <= 2'd0;

else if(Count1 == T10MS)

Count1 <= 2'd0;

else

Count1 <= Count1 + 1'b1;

reg rLED_Out;

always@(posedge CLK or negedge RSTn)

if(!RSTn)

rLED_Out <= 1'b0;

else if(Count1 == 2'd0)

rLED_Out <= 1'b1;

else

rLED_Out <= 1'b0;

assign LED_Out = rLED_Out;

endmodule

4. 仿真如下:

知识点~~~

1. 硬件描述语言 Hardware Description Language;

2. HDL采用自顶向下的电路设计方法,主要可以分为五个抽象层次:

3. HDL语言是有时序概念的,这和平常的编程语言不一样。

FPGA 流水灯的更多相关文章

- FPGA——流水灯(一)

对于FPGA的结构原理,先不进行全面的了解,先能根据教程程序看得懂,写得出来跑起来.慢慢的了解程序运行的原理,各种语法的使用. 今天对流水的程序有一个认识,熟悉软件的使用,语法规则,原理.以正点原子的 ...

- 第一个FPGA工程—LED流水灯

这一章我们来实现第一个FPGA工程-LED流水灯.我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序.掌握本章内容,大家就算正式的开始 ...

- 【黑金原创教程】【FPGA那些事儿-驱动篇I 】【实验一】流水灯模块

实验一:流水灯模块 对于发展商而言,动土仪式无疑是最重要的任务.为此,流水灯实验作为低级建模II的动土仪式再适合不过了.废话少说,我们还是开始实验吧. 图1.1 实验一建模图. 如图1.1 所示,实验 ...

- NIOS ii 流水灯

为了做项目的前期验证工作,实验室购买了某开发板,下面是基于该板子的实现过程.作为笔记记录,供入门者参考. 1:创建一个Quartus II的工程 next选择器件,然后finish.我的器件是cycl ...

- Xilinx Vivado的使用详细介绍(4):Zedboard+vivado之流水灯(加SDK)

Vivado+zedboard之初学流水灯 Author:zhangxianhe 环境:vivado 2016.3(已验证适用于2015.4) 开发板:Zedboard version xc7z020 ...

- 【接口时序】2、Verilog实现流水灯及与C语言的对比

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45 ...

- Zedboard学习(三):PL下流水灯实验 标签: fpgazynqPL 2017-07-05 11:09 21人阅读 评论(0)

zynq系列FPGA分为PS部分和PL部分. PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分. PS: 处理系统 (Processing System) , 就是与F ...

- S5PV210_流水灯

1.整体思路:把相应的配置数据写入相应的寄存器,控制GPIO电平(Led.s)——运用工程管理Makefile编译.链接文件(由Led.s编译得到led.bin,该文件用于USB启动方式点亮LED,若 ...

- (一)GPIO 编程实验 LED 流水灯控制

7个寄存器 是R1-R16.(当然,里面有很多是分几个模式的,所以总共有37个)类似于单片机的R0-R7. GPXCON,GPXDAT等等是另外的寄存器,应该叫,特殊功能寄存器,类似于单片机的P0,P ...

随机推荐

- python实现有趣的数学逻辑程序

1.无重复数字的三位数 题目:有1.2.3.4个数字, 能组成多少个互不相同且无重复数字的三位数? 都是多少? for i in range(1,5): for j in range(1,5): fo ...

- 分库分表的 9种分布式主键ID 生成方案,挺全乎的

<sharding-jdbc 分库分表的 4种分片策略> 中我们介绍了 sharding-jdbc 4种分片策略的使用场景,可以满足基础的分片功能开发,这篇我们来看看分库分表后,应该如何为 ...

- Windows自带MD5 SHA1 SHA256命令行工具

感恩大佬LiuYanYGZ的文章 MyHash 检验工具http://www.zdfans.com/html/4346.html HashMyFiles Hash校验工具http://www.nirs ...

- 用npm安装插件时报错: fsevents@^1.0.0 (node_modules\chokidar\node_modules\fsevents)

在做前端项目的时候执行命令: npm install --save-dev file-loader@1.1.6 --registry=https://registry.npm.taobao.org 出 ...

- 案例:简易的Div拖拽

案例:简易的Div拖拽 鼠标移入Div区域后,按下鼠标左键,可以拖动Div移动;松开鼠标左键,Div拖动停止.同时要求Div不能拖出屏幕显示区域外. 拖拽原理:距离不变.三个事件(onmousedow ...

- nginx&http 第二章 ngx 事件event配置等初始化

event事件模块,配置分为两层:ngx_events_module 事件模块 和 ngx_event_core_module 事件核心模块.ngx_events_module:模块类型NGX_COR ...

- 信号发送接收函数:sigqueue/sigaction

信号是一种古老的进程间通信方式,下面的例子利用sigqueue发送信号并附带数据:sigaction函数接受信号并且处理时接受数据. 1.sigqueue: 新的信号发送函数,比kill()函数传递了 ...

- SQL Server 不同数据间建立链接服务器进行连接查询

在平时查询以及导数据时,经常会遇到需要使用两个数据库里数据的情况,这时就会用到在两个服务器之间建立一个链接,进行操作,脚本语句如下: 举例:例如你在测试服务器上想要查询业务库里的数据信息,此脚 ...

- MySQL索引背后的数据结构及原理

摘要 本文以MySQL数据库为研究对象,讨论与数据库索引相关的一些话题.特别需要说明的是,MySQL支持诸多存储引擎,而各种存储引擎对索引的支持也各不相同,因此MySQL数据库支持多种索引类型,如BT ...

- win10,ubuntu时间不对问题

sudo apt-get install ntpdate sudo ntpdate time.windows.com # ntp2.aliyun.com 然后将时间更新到硬件上: sud ...