SV Interface and Program 2

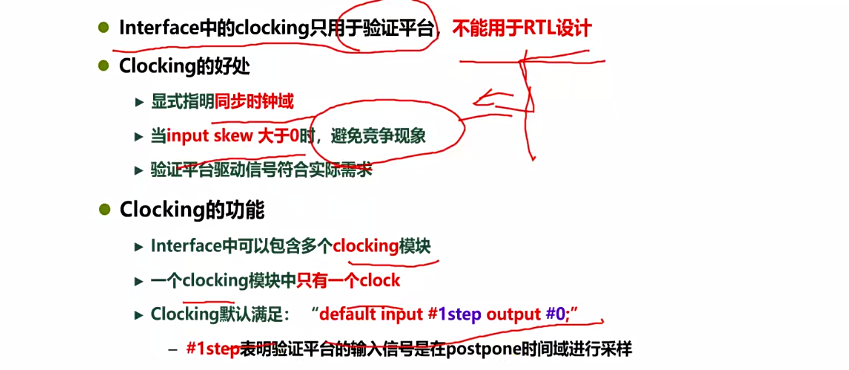

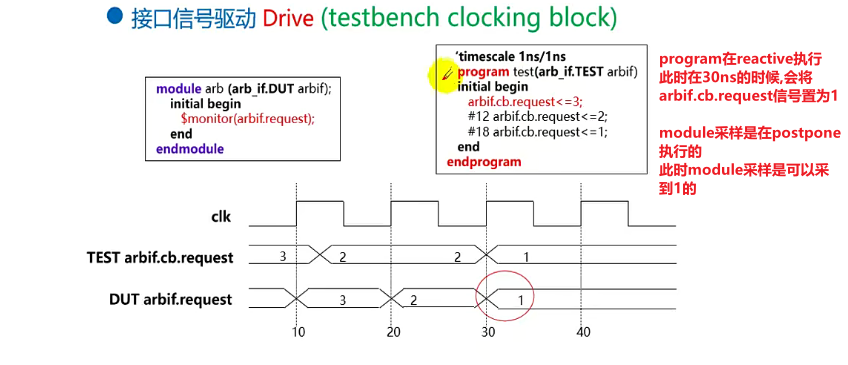

Clocking:激励的时序

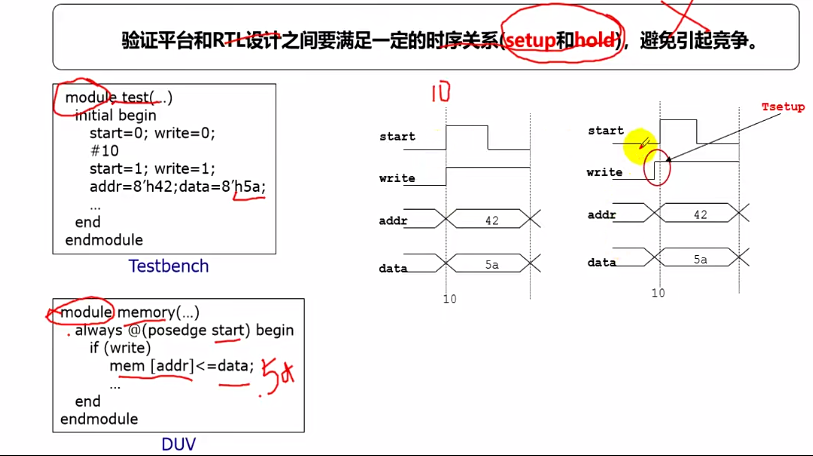

- memory检测start信号,当start上升沿的时候,如果write信号拉高之后,将data存储到mem中

- start\write\addr\data - 四个信号是同时在start上升沿进行,在采样的时候,testcase和Dut都是module,write采样的时候,有时候会采样到上升沿之前的值或者上升沿之后的值,需要规避这种情况

- 信号在时钟的驱动下发生跳变,会有delta-delay产生,并且delta-delay是不确定的,所以会造成采样的不确定性,使用clocking模块进行控制

- 需要给write信号稳定之后进行采样

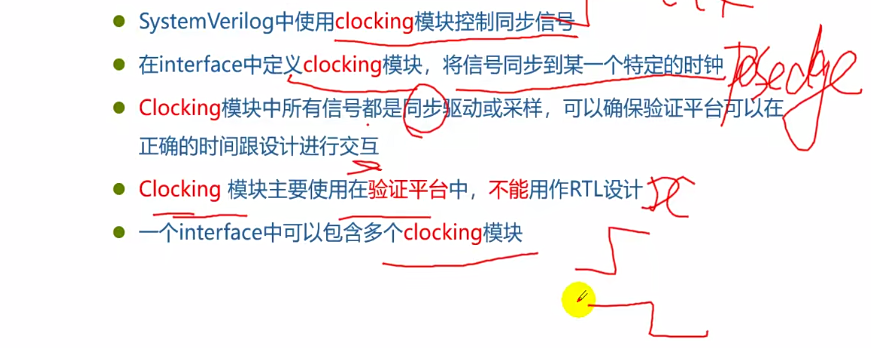

- 所以设置clocking模块进行控制

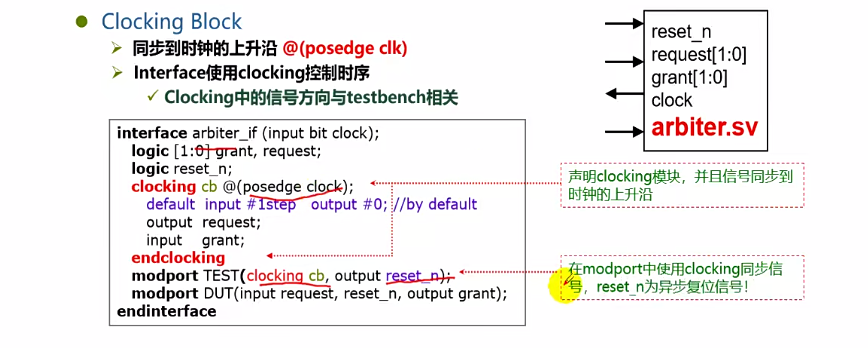

- 在clocking block定义在interface中,是不可综合的

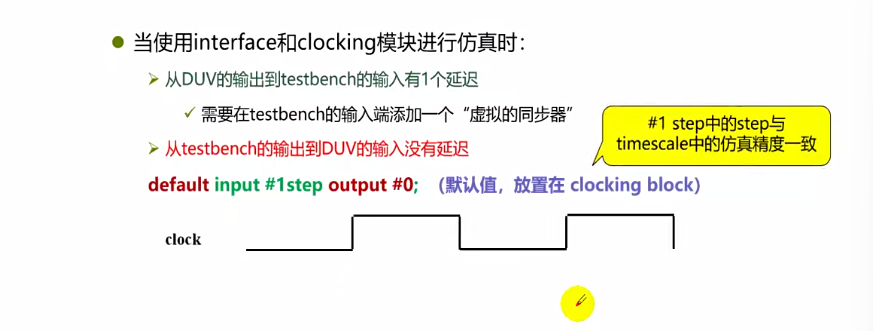

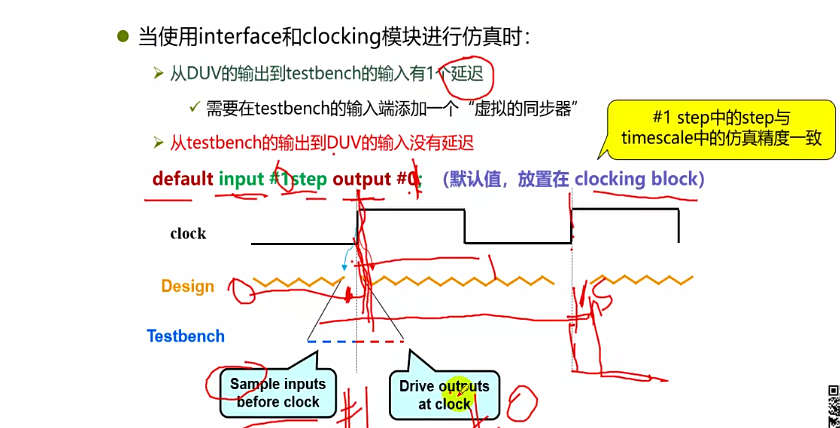

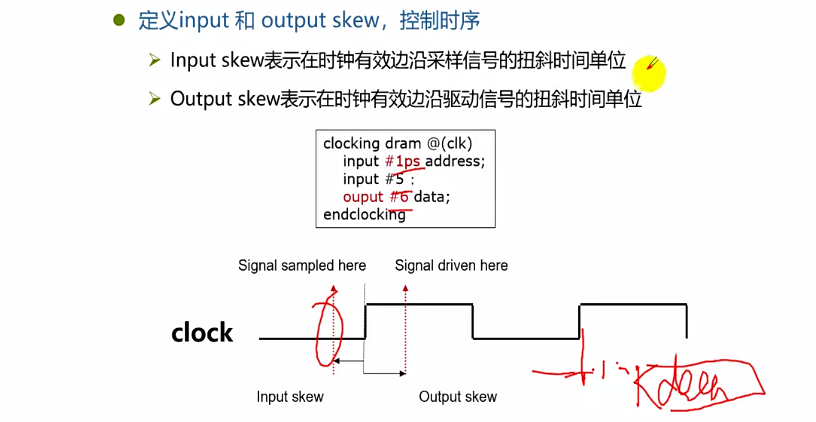

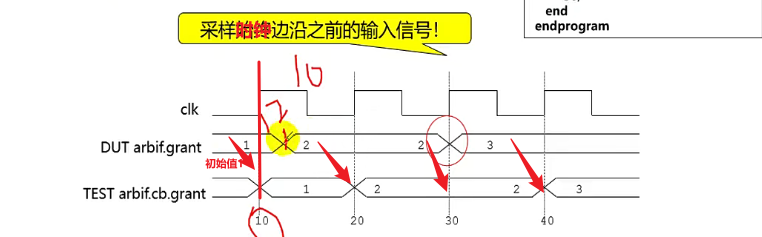

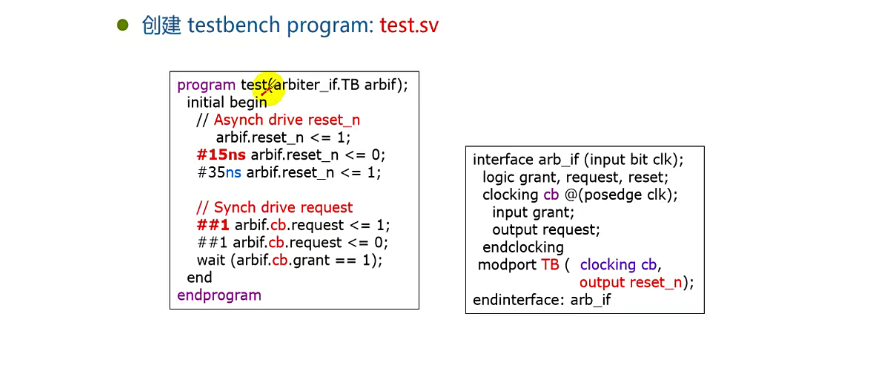

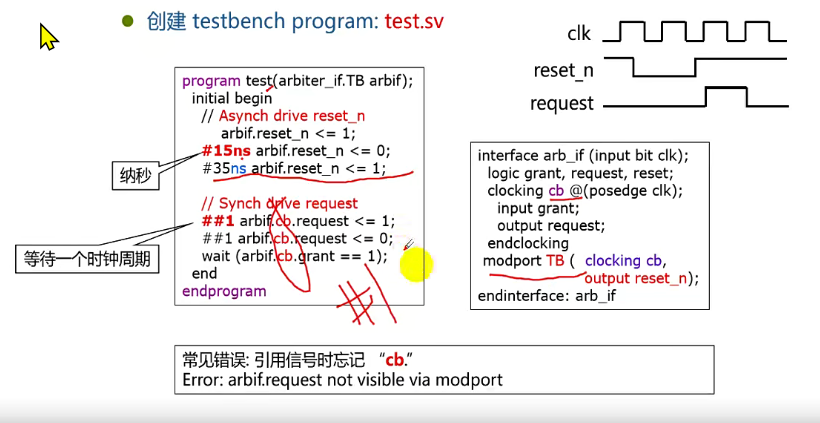

- 对于testbench,input(DUT输入)要延迟进行采样,就是在时钟上升沿之前1个时间单位采样

- output(输入给DUT) - 没有延时时间

- input向时钟上升沿之前多少时间单位进行采样,output向时钟上升沿之后多少个时间输出

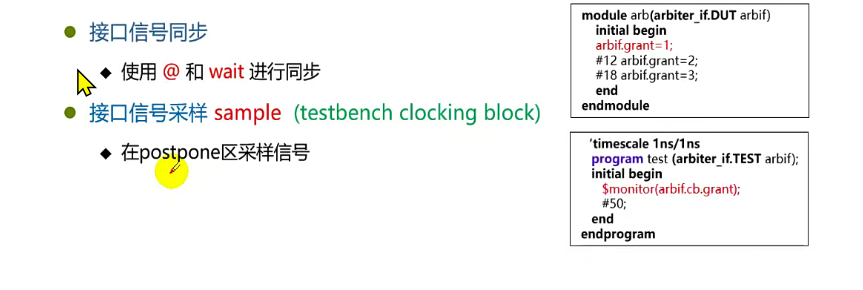

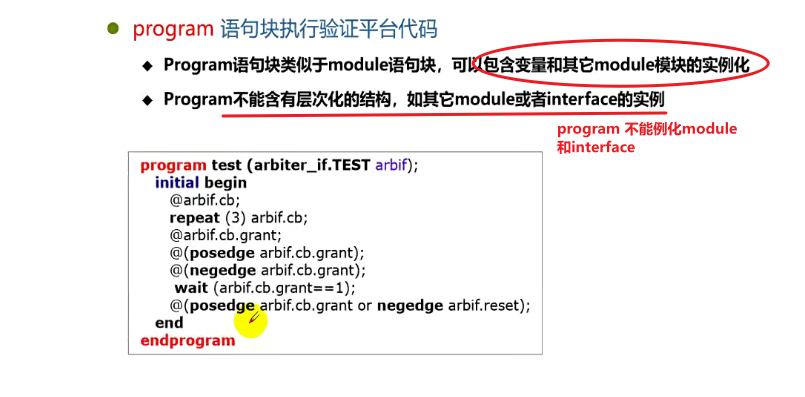

// 同步到时钟上升沿

clocking cb @(posedge)

default input #1step output #0;

output request;

input grant;

endclocking

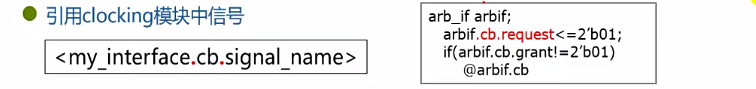

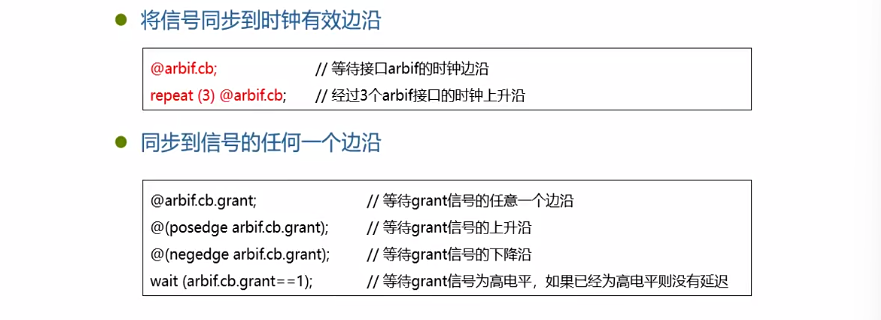

//将信号同步到时钟有效沿

@arbif.cb; // 等待接口arbif的时钟边沿

@(posedge arbif.clk) //等待接口arbif的时钟边沿

repeat(3) @arbif.cb; // 经过3个arbif接口的时钟上升沿

// 等待n个时钟周期 ##n - 阻塞语句

##2 arbif.cb.request <= 0; // 经过两个时钟周期之后进行赋值

- 同步信号,驱动输出信号使用非阻塞赋值,采样输入信号使用输入信号

- 非同步信号,阻塞赋值

forever begin

if(request == 1)

grant <= 1; // forever中没有时间推进语句,会造成死循环

end

总结

- Clocking模块中信号的方向与testbench相关

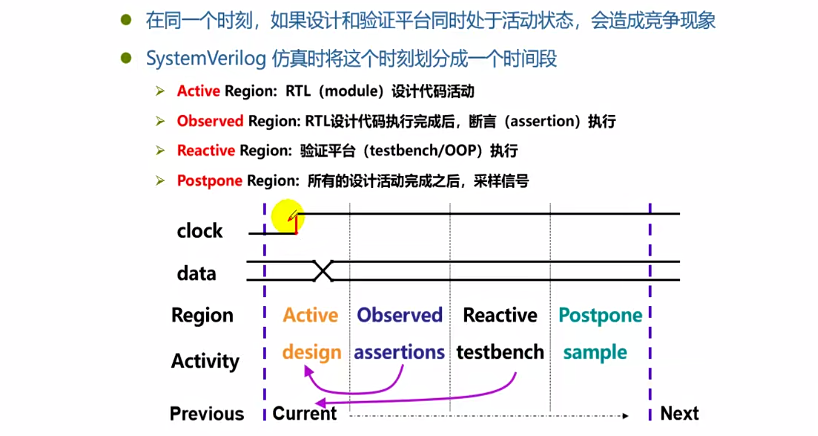

仿真时间域

- 不同代码的执行是有先后顺序的

- active region - 执行设计代码

- observed region - 执行断言

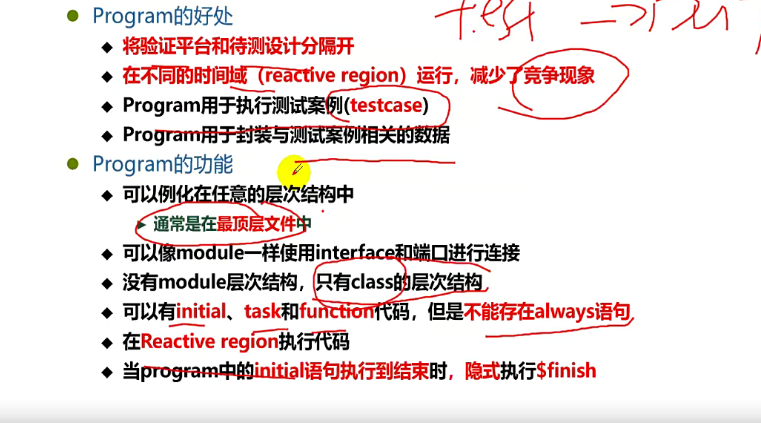

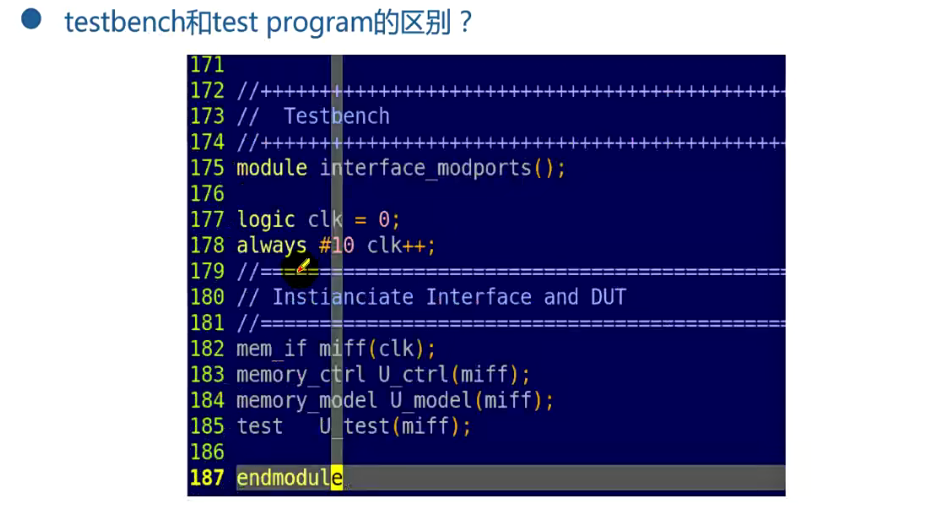

- Reactive region - testbench/oop,验证平台和dut都是module,仿真工具如何区分,testbench会用program进行定义,program可以认为是testbench

- Postpone region - sample

- program - 会在reactive region进行执行

- module - 会在active region进行执行

- 采样的时候采样到的是时钟之前的信号

Program block

- program语句只能用于testbench,不能用于design

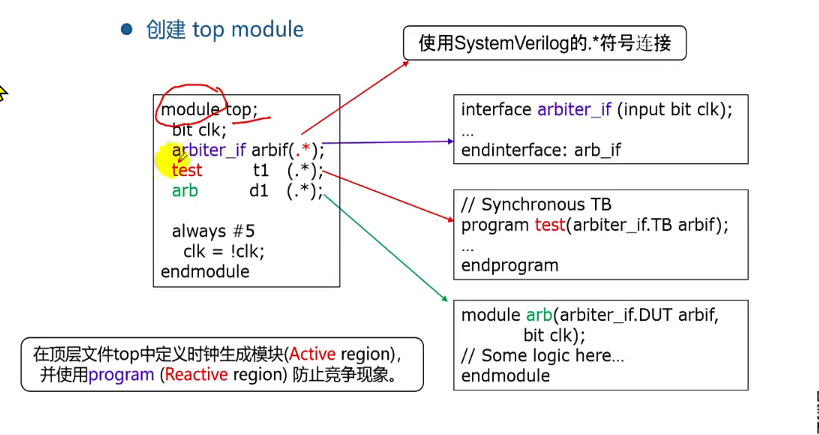

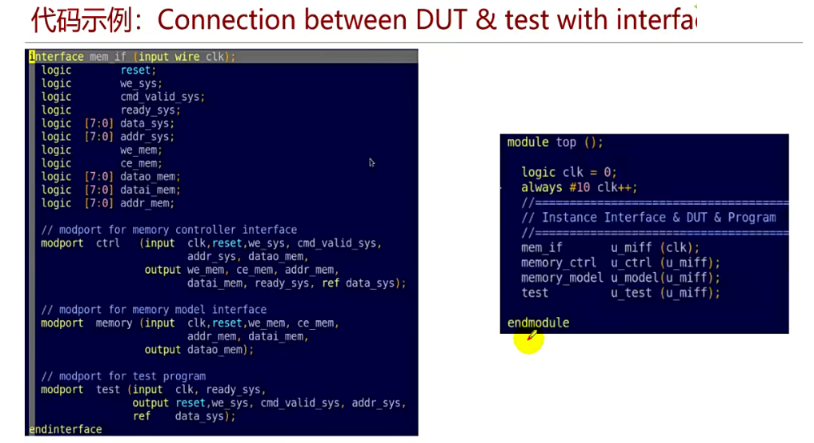

验证平台顶层文件-top文件

- tb_top必须是module

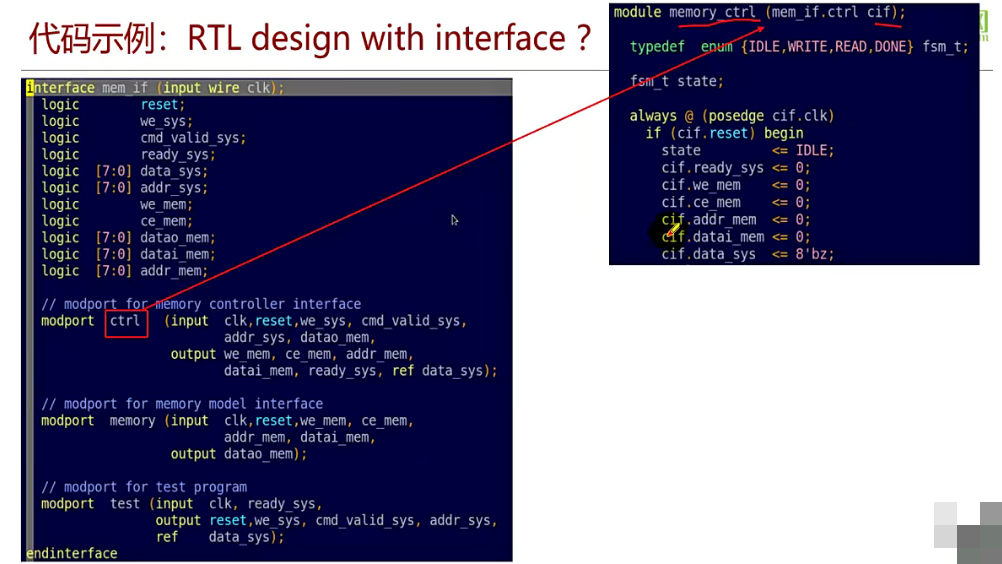

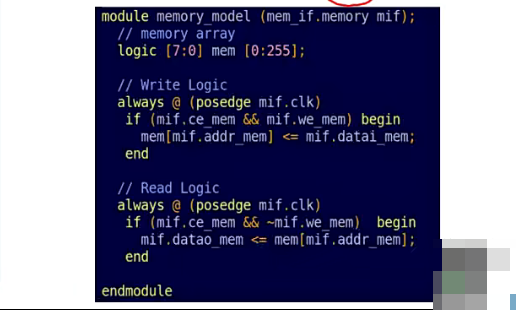

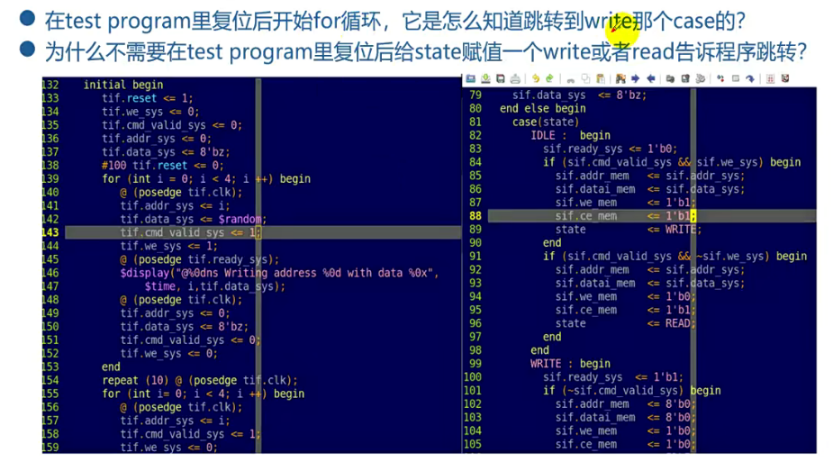

代码示例

SV Interface and Program 2的更多相关文章

- SV中的Interface和Program

Interface:SV中新定义的接口方式,用来简化接口连接,使用时注意在module或program之外定义interface,然后通过'include来添加进工程. interface arb_ ...

- program与module

program,各方面与module都类似,其中声明的变量在program中都可见, 生命周期也是static类型的, program的结束,也是需要等待其中的所有initial块都执行结束. 与mo ...

- sv命令空间 packge

SV中的module,interface,program,checker,都提供declaration空间,内部定义都local当前的那个scope,相互之间的building block不影响,不识 ...

- Tun/Tap interface tutorial

Foreword: please note that the code available here is only for demonstration purposes. If you want t ...

- C# explicit interface implementation(显式接口实现)

C# explicit interface implementation 某个类要实现两个包含相同方法名的接口, 应该如何实现这两个方法? namespace ExplicitInterfaceImp ...

- 如何搭建SoC项目的基本Testbench【zz】

原文地址:http://bbs.eetop.cn/thread-442797-1-8.html 写这个文档的目的是让大家对搭建SoC项目的Testbench有一个比较清晰的认识,可以根据这个文档来一步 ...

- Systemverilog for design 笔记(六)

转载请标明出处 第一章 有限状态机建模(FSM,finite state machine) 1.1. 使用枚举类型建立状态机模型 l 三过程块建模风格:三个过程块分别实现: a.状态转换(al ...

- Systemverilog for design 笔记(一)

转载请标明出处 一. System Verilog 声明的位置 1. 包(packages) Verilog要求局部声明: variables, nets, tasks and f ...

- A web crawler design for data mining

Abstract The content of the web has increasingly become a focus for academic research. Computer prog ...

- C语言代写

MTRX1702 - C ProgrammingAssignment 2This assignment requires you to design and build a program that ...

随机推荐

- 华企盾DSC防泄密软件造成VS启动报目录错误

解决方法:找到安装路径下的Privateregistry.bin文件解密即可

- 【Python微信机器人】第六七篇: 封装32位和64位Python hook框架实战打印微信日志

目录修整 目前的系列目录(后面会根据实际情况变动): 在windows11上编译python 将python注入到其他进程并运行 注入Python并使用ctypes主动调用进程内的函数和读取内存结构体 ...

- 从零玩转Yaip使用-cong-ling-wan-zhuan-yaip-shi-yong

title: 从零玩转Yaip使用 date: 2021-07-16 15:47:17.624 updated: 2021-12-26 17:43:12.255 url: https://www.yb ...

- vulnhub - Nagini - writeup

信息收集 基础信息 目标只开放了22和88: root@Lockly tmp/nagini » arp-scan -I eth1 -l Interface: eth1, type: EN10MB, M ...

- EvilBox : ONE - WriteUp

EvilBox : ONE 信息收集 扫描网段内存活主机,得到目标 nmap 进一步收集有效信息,只开放了22和80 访问80的页面没有什么有效信息 接着扫一下目录, 没有敏感的文件 在robots中 ...

- C#数据结构与算法系列(十六):时间复杂度(上)

1.时间频度 介绍: 一个算法花费的时间与算法中语句的执行次数成正比例,哪个算法中语句执行次数多,他花费时间越多.一个算法中的语句执行次数称为语句频度或时间频度 举例说明: 比如计算1-100所有数字 ...

- Langchain-Chatchat项目:1.2-Baichuan2项目整体介绍

由百川智能推出的新一代开源大语言模型,采用2.6万亿Tokens的高质量语料训练,在多个权威的中文.英文和多语言的通用.领域benchmark上取得同尺寸最佳的效果,发布包含有7B.13B的Bas ...

- 【API进阶之路】太秃然了,老板要我一周内检测并导入一万个小时的视频

摘要:假期结束后回来上班,走进电梯都有一种特别的感觉,电梯那个植发广告里的大哥看我的眼神好像和之前不太一样- 上回说到,老板奖励7天带薪假,我就回家玩耍了几天,顺便还帮兄弟发不脱当了一回"A ...

- 华为云举办AI经典论文复现活动,打造领先AI开发者学习社区

摘要:百余篇经典论文算法上线华为云AI Gallery,学AI就用ModelArts 2020年8月28日,华为云AI院长峰会在杭州千岛湖举行,来自中国科学院.中国工程院的多位院士,以及清华大学.北京 ...

- storybook组件属性详解:组件props到strorybook Args

首先我们查看官方文档:https://storybook.js.org/docs/vue/writing-docs/doc-block-argstable#customizing 官方的例子么有看到v ...