【转载】数字IC设计流程及开发工具

原文链接:https://www.zhihu.com/question/28322269/answer/42048070

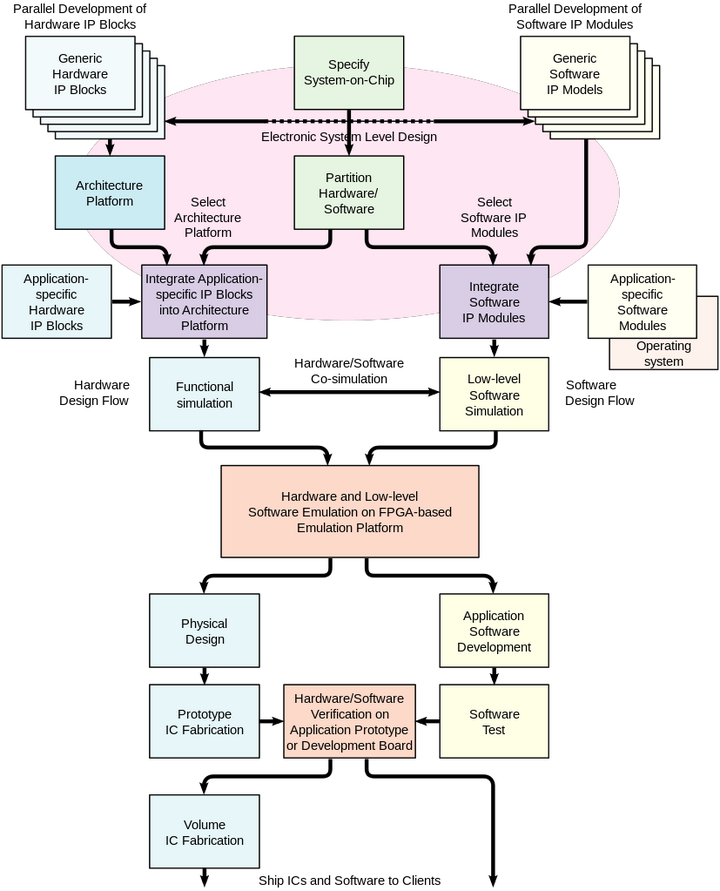

Design Flow

<img src="https://pic1.zhimg.com/50/c21722c94ed307d02d10330460cf6886_hd.jpg" data-rawwidth="827" data-rawheight="1023" class="origin_image zh-lightbox-thumb" width="827" data-original="https://pic1.zhimg.com/c21722c94ed307d02d10330460cf6886_r.jpg"/>

IC设计流程以及各个阶段使用的工具

<img src="https://pic4.zhimg.com/50/d09353bab1b8acbcf4d13e3937c89896_hd.jpg" data-rawwidth="2362" data-rawheight="1000" class="origin_image zh-lightbox-thumb" width="2362" data-original="https://pic4.zhimg.com/d09353bab1b8acbcf4d13e3937c89896_r.jpg"/>前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计。

1. 规格制定

芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。2. 详细设计

Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。3. HDL编码

使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。4. 仿真验证

仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。 设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Synopsys的VCS,还有Cadence的NC-Verilog。5. 逻辑综合――Design Compiler

仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard

cell)的面积,时序参数是不一样的。所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)。

逻辑综合工具Synopsys的Design Compiler。6. STA

Static Timing Analysis(STA),静态时序分析,这也属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。这个是数字电路基础知识,一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。

STA工具有Synopsys的Prime Time。7. 形式验证

这也是验证范畴,它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。

形式验证工具有Synopsys的Formality。前端设计的流程暂时写到这里。从设计程度上来讲,前端设计的结果就是得到了芯片的门级网表电路。

Backend design flow :

1. DFT

Design For Test,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。关于DFT,有些书上有详细介绍,对照图片就好理解一点。

DFT工具Synopsys的DFT Compiler2. 布局规划(FloorPlan)

布局规划就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。

工具为Synopsys的Astro3. CTS

Clock Tree Synthesis,时钟树综合,简单点说就是时钟的布线。由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。

CTS工具,Synopsys的Physical Compiler4. 布线(Place & Route)

这里的布线就是普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的0.13um工艺,或者说90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟道长度。

工具Synopsys的Astro5. 寄生参数提取

由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。

工具Synopsys的Star-RCXT6. 版图物理验证

对完成布线的物理版图进行功能和时序上的验证,验证项目很多,如LVS(Layout Vs

Schematic)验证,简单说,就是版图与逻辑综合后的门级电路图的对比验证;DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求, ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气 规则违例;等等。

工具为Synopsys的Hercules实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题,在此不说了。

物理版图验证完成也就是整个芯片设计阶段完成,下面的就是芯片制造了。物理版图以GDS II的文件格式交给芯片代工厂(称为Foundry)在晶圆硅片上做出实际的电路,再进行封装和测试,就得到了我们实际看见的芯片。

【转载】数字IC设计流程及开发工具的更多相关文章

- VerilogHDL概述与数字IC设计流程学习笔记

一.HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言.那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是 ...

- 数字IC设计工程师的知识结构

刚毕业的时候,我年少轻狂,以为自己已经可以独当一面,庙堂之上所学已经足以应付业界需要.然而在后来的工作过程中,我认识了很多牛人,也从他们身上学到了很多,从中总结了一个IC设计工程师需要具备的知识架构, ...

- 数字IC设计入门书单

首发于观芯志 写文章 数字IC设计入门书单 Forever snow 1 年前 作者:Forever snow链接:你所在领域的入门书单? - 知乎用户的回答来源:知乎著作权归作者所有,转 ...

- 数字IC设计入门必备——VIM自定义模板调用与VCS基本仿真操作示例

一.前言 毕业论文答辩结束,闲下来写篇文章.芯片研发人员都在Linux系统下借助各种EDA工具和代码语言完成工作,因此提高代码开发效率,熟练运用开发工具是十分必要的.本文讲述VIM编辑神器的veril ...

- IC设计流程介绍

芯片设计分为前端设计和后端设计,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计. 1. 规格制定 芯片规格,也就像功能列表一样 ...

- IC设计流程概述

芯片设计分为前端设计和后端设计,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计. Front-end design flow 1. 规格制定 ...

- 数字IC设计-15-DPI(延续)

简介 供SV,无论是构建测试激励,或模拟硬件的并行行为,DPI这是非常方便.上次我们介绍SV内通"import"导入和电话C性能. 在本节,通过一个简单的例子来说明C什么语言的函数 ...

- 数字IC设计工程师成长之路

学习的课程 仿真工具VCS实践学习 2019年12月9日-2019年12月23日

- 数字IC前后端设计中的时序收敛(五)--Max Transition违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

随机推荐

- XSS相关有效载荷及绕道的备忘录(下)| 文末有打包好的负载

前言: 今天发布的是下半部分 进入正题 过滤的绕过和一些奇异的有效载荷 大小写绕过 <sCrIpt>alert(1)</ScRipt> 绕过标签黑名单 <script x ...

- Html引入百度富文本编辑器ueditor及自定义工具栏

在日常工作用,肯定有用到富文本编辑器的时候,富文本编辑器功能强大使用方便,我用的是百度富文本编辑器,首先需要下载好百度编辑器的demo, 然后创建ueditor.html文件,引入百度编辑器,然后在h ...

- python循环删除列表元素留一个问题

https://www.cnblogs.com/baihualin/p/10698651.html 引用up

- cmake设定boost python3

在mac上操作的.python3是anaconda环境下装的,3.7.1. boost是用brew装的,1.71.0版本. 按照FindBoost.cmake官方写法的CMakeLists.txt: ...

- apache2.4

介绍 Apache HTTP server是Apache软件基金会的一个开源的网页服务器,可以运行在几乎所有广泛使用的计算机平台上,由于跨平台和安全性被广泛使用,是目前最流行的web服务器软件之一,目 ...

- Nginx基础知识介绍

Nginx基础知识介绍 作者:尹正杰 版权声明:原创作品,谢绝转载!否则将追究法律责任. 一.Nginx概述 Nginx是免费的.开源的.高性能的HTTP和正向/反向代理服务器.邮件代理服务器.以及T ...

- nbu虚拟机恢复样例(之后补图)

9.2.1进入Backup,Archive,and Restore管理器 9.2.2选择客户端和策略类型 9.2.3选择恢复的虚拟机 9.2.4恢复虚拟机到不同目录 9.2.5更改虚拟机名称和存储 因 ...

- maven中,dependency 中的 classifier属性

classifier元素用来帮助定义构件输出的一些附属构件.附属构件与主构件对应,比如主构件是 kimi-app-2.0.0.jar 该项目可能还会通过使用一些插件生成 如 kimi-app-2.0. ...

- PAT 乙级 1042.字符统计 C++/Java

题目来源 请编写程序,找出一段给定文字中出现最频繁的那个英文字母. 输入格式: 输入在一行中给出一个长度不超过 1000 的字符串.字符串由 ASCII 码表中任意可见字符及空格组成,至少包含 1 个 ...

- django model content_type 使用

一.关于content_type 使用 1.引入模块在models from django.db import models from django.contrib.contenttypes.mode ...