阅读GIC-500 Technical Reference Manual笔记

GIC-500是ARM GICv3的一个实现,它只支持ARMv8核和实现了GIC Stream协议的GIC CPU Interface,比如Cortex-A53。

关于GIC有四份相关文档:《Cortex-A53 TRM》介绍了GIC CPU Interface;《ARMv8-A Architecture Profile》提供了GIC CPU Interface的细节;《GIC-500 TRM》介绍了GICv3的一个实现;《GICv3/4 Architecture Specification》介绍了GIC架构细节规范。

这四份文档可以分为两部分:GIC CPU Interface和GIC本身。

1 Introduction

SGIs - Software Generated Interrupts

ITS - Interrupt Translation Service

LPIs - Locality-specific Peripheral Interrupts

SPIs - Shared Peripheral Interrupts

PPIs - Private Peripheral Interrupts

1.1 About the GIC-500

GIC-500支持高达128核,只支持ARMv8架构的核和GIC Stream Protocol接口的GIC CPU接口,Physical interrupt signals,SGIs,从AXI4 slave端口产生的中断,ITS提供ID转换等功能。

GIC-500从AXI4 Slave或者Physical interrupt inputs接收中断,和CPU通过AXI4-Stream接口连接,通过AXI4 Slave端口被编程。

GIC CPU interface属于GIC一部分,但不属于GIC-500,而更倾向于属于ARMv8 core的一部分。

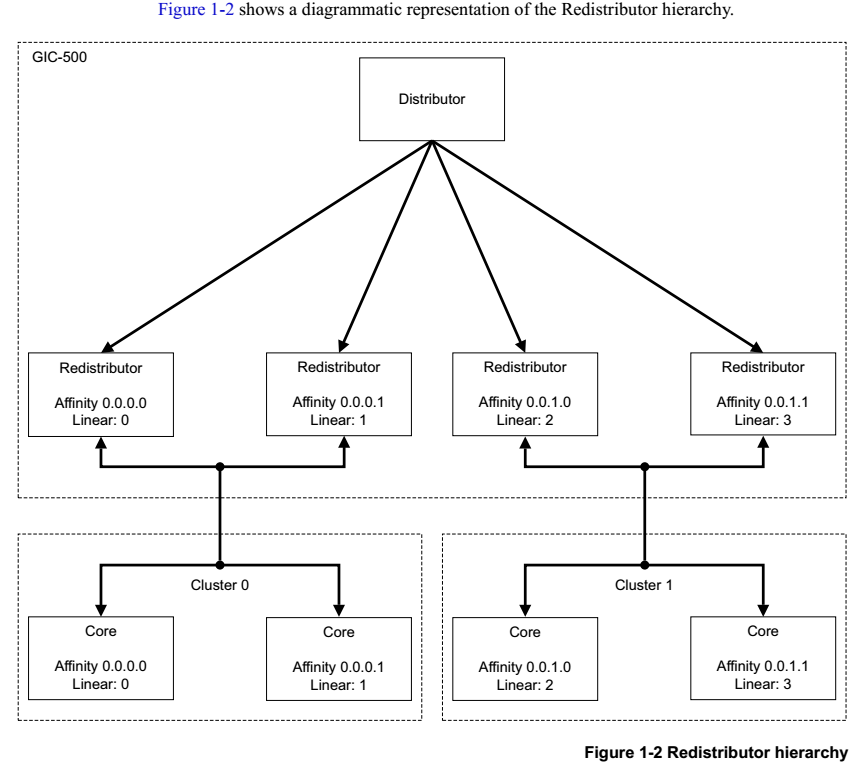

GIC-500的Distributor->Redistributor->Cluster->Core的拓扑结构:

ARM架构通过MPIDR(Multiprocessor Affinity Register)寄存器给给每个CPU制定一个逻辑地址。

ARMv7支持三层,ARMv8支持四层,MPIDR有着明显的分层结构,<Aff3>.<Aff2>.<Aff1>.<Aff0>。

GIC-500只支持两层,所以MPIDR的值只能是0.0.c.d,c是process层,d是core层。GIC-500支持128 core或者32 processor,并且每processor不超过8 core。

1.3 Features

- 支持高达128 core

- affinity-level 1支持高达32 cluster

- 每cluster高达8 core

- 16个SGIs,ID0-ID15

- 16个PPIs,ID16-ID31

- 基于Affinity的可编程中断路由

- 中断屏蔽和优先级控制

- 每中断可配置32个优先级

2 Functional Description

2.1 About the functions

ICB: Interrupt Control Block.

ICB State RAM是保存SPIs、PPIs、SGIs各种配置的地方。同样LPI State RAM和ITE State RAM是保存LPIs和ITS设置的地方。

2.2 Interfaces

从Figure 2-1可以看出GIC-500和外部的接口包括:AXI4 Slave Interface、AXI4 Master Interface、RAM Interfaces、Physical interrupt signals、GIC-500 Stream Protocal Interface。

AXI4 Slave Interface:可以通过此接口对GIC-500所有部分编程,包括Distributor、Redistributor、ITS。同时也负责处理message-based中断,也即通过写AXI4 slave interface产生的中断。message-based中断可以产生SGI/LPI类型的中断。

AXI4 Master Interface:GIC-500通过此接口访问主内存,包括ITS的translation tables、ITS command queue、LPI配置表、LPI pending table等。

RAM Interfaces:和各种State RAM接口。

Physical interrupt signals:产生SPIs和PPIs类型中断的信号,可配置成level-sensitive、edge-triggered。

GIC-500 Stream Protocal Interface:用于发送中断给CPU核,并且从CPU接收激活中断的通知。

2.3 Operation

GIC-500可以分成三个主要部分:ITS(将外设message-based中断翻译成LPIs)、Distributor(接收Wire interrupts或者编程接口过来的中断,然后根据优先级发送到CPU Interface)、Redistributor(每CPU核一个Redistributor,保存每个核的PPIs/SGIs/:PIs状态)。

GIC-500支持不同类型的中断,主要包括:

SGIs - 是核间中断,从一个核触发发送到另外核。一个核上触发的中断,并不影响其他核上同样中断号,并且每个核的SGI设置都是独立的。可以通过System register或者GICD_SGIR触发中断,共16个独立的SGIs,ID0-ID15。

PPIs - 用于和CPU和紧耦合的外设,因此PPI仅发送到相关的CPU核。一个核上触发的PPI总段并不会影响其他核相同ID号的PPI,而且每个核的PPI设置也是相互独立的。

SPIs - 用于不和特定CPU和紧耦合的外设,一个核上触发的SPI中断,同时也会激活其他核上的中断。但是也可以通过编程设置SPI到特定的核。GIC-500只允许一个核响应SPI中断,SPI的设置是核间共享的。SPI可以被wire input或者AXI4 slave programming interface触发。GIC-500支持高达960各终端,spi[991:32]。

LPIs - 多用于产生message-based类型中断的外设,一个LPI同一时刻只能指向一个核。

Interrupt group:Group 0、Group 1 Secure、Group 1 Non-secure。

Interrupt triggering:Level-sensitive(这种类型的中断会一直pending,直到被asserted)和Edge-triggered(上升沿触发导致中断变成pending状态,直到被CPU interface activated时清pending位)。

Power Management:GIC-500不仅支持对应的核被关闭,同时自身也可以被关闭。通过GICR_WAKER寄存器来设置。

2.4 Clocking and resets

GIC-500仅有一个时钟输入clk,和一根reset信号resetn。

3 Programmers Model

3.2 The GIC-500 register map

GICD - GIC Distributor register

GICR - GIC Redistributor register

GITS - GIC Interrupt Translation Service register

4 相关延伸

在每个平台的实现中都会对中断资源进行定义,这是一个GIC-500对应的中断控制器设置:

/* 0-15: SGI (software generated interrupts)

* 16-31: PPI (private peripheral interrupts)

* 32+: SPI (shared peripheral interrupts)

*/ #define GIC_PPI_START 16

#define GIC_SPI_START 32 /*

* software generated interrupts

*/

#define SGI0_INT (0)

#define SGI1_INT (1)

#define SGI2_INT (2)

#define SGI3_INT (3)

#define SGI4_INT (4)

#define SGI5_INT (5)

#define SGI6_INT (6)

#define SGI7_INT (7)

#define SGI8_INT (8)

#define SGI9_INT (9)

#define SGI10_INT (10)

#define SGI11_INT (11)

#define SGI12_INT (12)

#define SGI13_INT (13)

#define SGI14_INT (14)

#define SGI15_INT (15) /*

* private peripheral interrupts

*/

...

/*

* shared peripheral interrupts

*/

#define WDT_INT (GIC_SPI_START+0)

... #define NR_SOC_IRQS (GIC_SPI_START+77)

更深入的分析,就需要和Linux kernel中GIC相关代码结合了。

阅读GIC-500 Technical Reference Manual笔记的更多相关文章

- 阅读Cortex-A53 Technical Reference Manual笔记

1. 前言 一颗芯片最主要的就是CPU核了,处理CPU Core之外,还存在很多其他IP,包括Graphical.Multimedia.Memory Controller.USB Controller ...

- Oracle Global Finanicals Technical Reference(一个)

Skip Headers Oracle Global Finanicals Oracle Global Financials Technical Reference Manual Release 11 ...

- Oracle Global Finanicals Technical Reference(一)

Skip Headers Oracle Global Finanicals Oracle Global Financials Technical Reference Manual Release 11 ...

- Oracle Global Finanicals Technical Reference(二)

Skip Headers Oracle Global Finanicals Oracle Global Financials Technical Reference Manual Release 11 ...

- 阅读ARM Memory(L1/L2/MMU)笔记

<ARM Architecture Reference Manual ARMv8-A>里面有Memory层级框架图,从中可以看出L1.L2.DRAM.Disk.MMU之间的关系,以及他们在 ...

- 阅读 ‘External Memory PHY Interface (ALTMEMPHY)’笔记

阅读 ‘External Memory PHY Interface (ALTMEMPHY)’笔记 1.PLL reference clock frequency 此处控制器输入时钟设置为100MHz, ...

- OpenCASCADE6.8.0 Reference Manual Serach Problem

OpenCASCADE6.8.0 Reference Manual Serach Problem eryar@163.com 1. Problem 有网友反映OpenCASCADE6.8.0的Refe ...

- 阅读《LEARNING HARD C#学习笔记》知识点总结与摘要系列文章索引

从发表第一篇文章到最后一篇文章,时间间隔有整整一个月,虽只有5篇文章,但每一篇文章都是我吸收<LEARNING HARD C#学习笔记>这本书的内容要点及网上各位大牛们的经验,没有半点废话 ...

- 阅读《LEARNING HARD C#学习笔记》知识点总结与摘要三

最近工作较忙,手上有几个项目等着我独立开发设计,所以平时工作日的时候没有太多时间,下班累了就不想动,也就周末有点时间,今天我花了一个下午的时间来继续总结与整理书中要点,在整理的过程中,发现了书中的一些 ...

随机推荐

- android Google推荐的容器SparseArrayCompat简介

android Google推荐的容器SparseArrayCompat简介 private static SparseArrayCompat<BaseFragment> mCaches ...

- 网站开发进阶(二十一)Angular项目信息错位显示问题解决

Angular项目信息错位显示问题解决 绪 最近在项目开发过程中遇到这样一个棘手的问题:查询出所有订单信息后,点击选择某一个订单,查询出的结果是上一次查询所得的结果.而且会出现点击两次才可以显示订单详 ...

- java工具类(五)之日期格式字符串与日期实现互转

JAVA字符串转日期或日期转字符串 项目开发过程中需要实现日期格式的字符串与日期进行互转,并进行日期的加减操作. Demo如下: package weiming.lmapp.utils; import ...

- 菜鸟玩云计算之十七:RHEL克隆虚拟机后改变网卡地址

菜鸟玩云计算之十七:RHEL克隆虚拟机后改变网卡地址 (一)更改hostname # vi /etc/sysconfig/network NETWORKING=yes HOSTNAME=your-vm ...

- Google官方网络框架-Volley的使用解析Json以及加载网络图片方法

Google官方网络框架-Volley的使用解析Json以及加载网络图片方法 Volley是什么? Google I/O 大会上,Google 推出 Volley的一个网络框架 Volley适合什么场 ...

- MIDle生命周期详解,以及工作原理

当MIDlet被应用程序管理器成功地初始化之后,就开始展开了它的生命周期.MIDlet的生命周期完全由应用程序管理器控制,也就是说,当MIDlet要从一个状态变成另外一个状态时,应用程序管理器会调用对 ...

- objective-c中所谓的僵尸对象

正常情况下向已回收的对象发送消息时灵时不灵,具体要看该对象所占内存有没有被覆写.cocoa提供了僵尸对象(Zombie Object)这个功能,简单的说:启用该调试功能后,运行时会将所有已回收的实例转 ...

- 超高速前端开发工具——Emmet

[由于 CSDN 不支持富文本编辑器写的文章迁移到 Markdown 编辑器中修改,已重发了一个重新排版的版本, 新版链接:http://blog.csdn.net/ys743276112/artic ...

- C# 压缩PDF图片

文档中包含图片的话,会使得整个文档比较大,占用存储空间且不利于快速.高效的传输文件.针对一些包含大量高质图片的PDF文档,若是对图片进行压缩,可以有效减少文档的占用空间.并且,在文档传输过程中也可以减 ...

- 安装Emacs并设置racket环境

最近在阅读sicp这本书,书中的代码是使用scheme实现的.之前阅读的时候是使用Dr.Racket来完成写练习的,可我觉得与其这样,不如一步到位,使用emacs+lisp解释器来的比较快. 安装em ...