数字IC后端布局阶段对Tie-high和Tie-low Net的处理

本文转自:自己的微信公众号《集成电路设计及EDA教程》

里面主要讲解数字IC前端、后端、DFT、低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程。

考虑到微信公众平台上面发布的很多推文百度搜索不到,所以以后的推文也会在这里进行转载。

《数字IC后端布局阶段对Tie-high和Tie-low Net的处理》

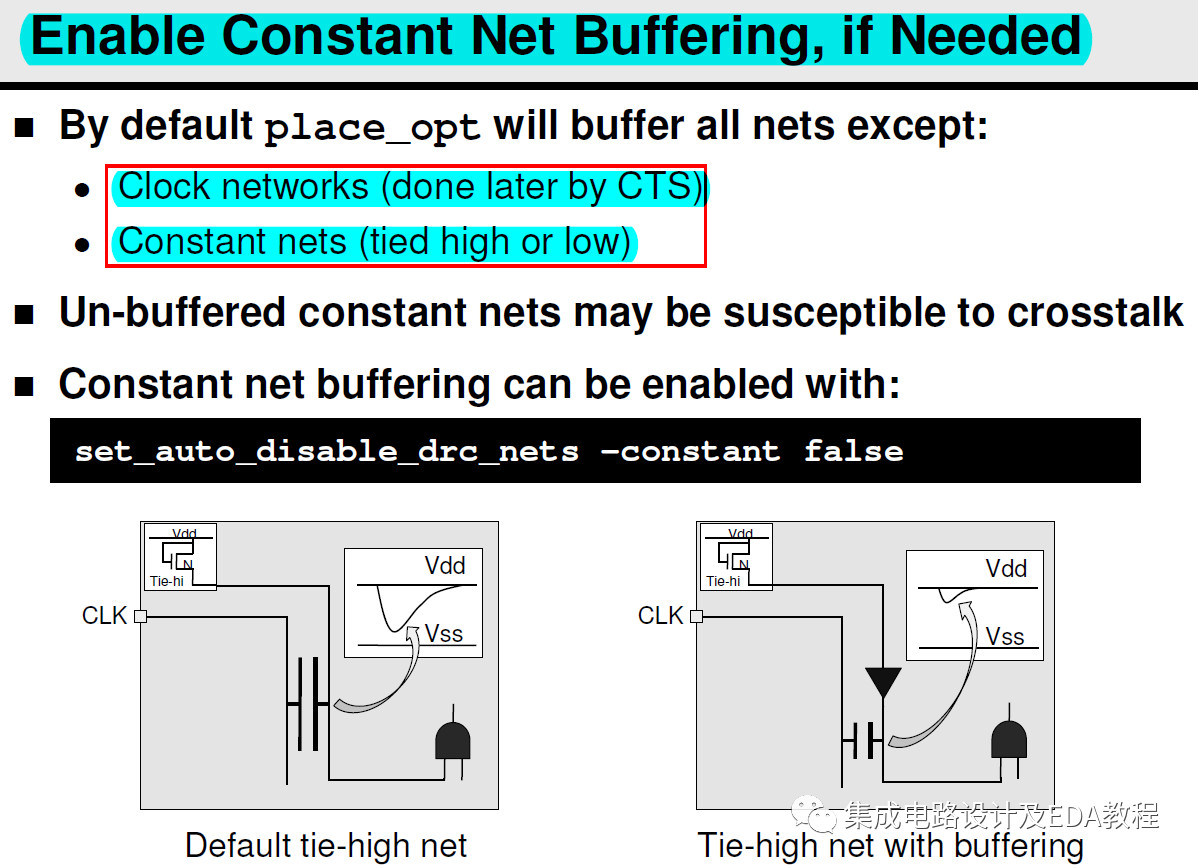

布局阶段ICC对于时钟网络和恒0/1网络(Constant Net)的行为:

在布局阶段,在默认情况下,对于时钟网络和恒0/1网络(也就是Tie-high和Tie-low的net),ICC是不会做逻辑DRC(Design RuleConstraint)的检查与修复的。这也意味着在执行place_opt时,ICC不会在这些net上插入Buffer。在布局阶段我们也不想在时钟网络上插入Buffer,但是对于Tie-high和Tie-low的Net,如果软件不在上面插入Buffer,可能会产生一些问题。在默认设置下工具在place_opt时对tie-high和tie-low的net的行为:会用tie-high和tie-low的Cell去驱动尽量多的Cell。

逻辑DRC(Design Rule Constraint):

即max_transition, max_capacitance, max_fanout。这些规则决定布局布线引擎是否需要在这些Net上插入Buffer。

Constant Net上面不插入Buffer的缺点:

其信号容易受到串扰的影响,如下图所示:

在离Tie-high的Net比较近的地方,如果有个高速时钟信号(两条线并行走了很长的距离),那么它的恒定电平会受到串扰的影响而产生毛刺。

而对于加了Buffer的Tie-high网络,它不容易受到串扰的影响,原因如下:

1、由于互连线长度缩短了,因此耦合电容大幅降低,串扰会大大降低;

2、由于Buffer有非常好的电平保持和恢复能力,与Tie-high Cell相比,抗串扰能力更好。

Constant Net上面插入Buffer的缺点:

以面积为代价,Tie-high/low的net扇出越大(也就是说设计中固定0/1输入比较多),加的Buffer越多。

如何使能Constant Net Buffering呢?

ICC命令:set_auto_disable_drc_nets -constant false

set_app_varphysopt_new_fix_constants true

set_attribute[...] max_fanout 12

set_attribute[...] max_capacitance 0.2 -type float

设置完成后工具的行为:

用tie-high和tie-low尽量驱动更多的单元,同时满足指定的最大扇出和最大电容约束。

set_auto_disable_drc_nets命令可以在常量网络上启用DRC修复。

physopt_new_fix_constants变量设置为true会使得工具在优化期间注意最大电容约束。最大电容约束由max_capacitance属性确定,该属性使用set_max_capacitance或set_attribute命令设置。 set_attribute命令用于明确指定设计中对象的最大扇出和最大电容约束。

## 为了方便大家交流讨论 ##

## 建了一个QQ群 ##

## 集成电路设计及EDA教程 ##

## 加群请备注:EDA ##

## 群二维码如下 ##

数字IC后端布局阶段对Tie-high和Tie-low Net的处理的更多相关文章

- 数字IC前后端设计中的时序收敛(五)--Max Transition违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- 数字IC前后端设计中的时序收敛(二)--Setup违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- 数字IC前后端设计中的时序收敛(四)--Max Capacitance违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- 数字IC前后端设计中的时序收敛(三)--Hold违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程>(二维码见博文底部) 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教 ...

- 数字IC前后端设计中的时序收敛(一)前言

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 为了纪念,同时 ...

- 数字IC前后端设计中的时序收敛(六)--Max Fanout违反

本文转自:自己的微信公众号<数字集成电路设计及EDA教程>(二维码见博文底部) 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教 ...

- VerilogHDL概述与数字IC设计流程学习笔记

一.HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言.那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是 ...

- 数字IC笔试题-芯源

前言 由于最近开始找数字IC的工作,所以准备多练笔试题,下面贴上芯源笔试题,来源微信公众号<数字IC打工人> 参考资源: 1. mu_guang_ 2. 李锐博恩 3. 长弓的坚持 4. ...

- (数字IC)低功耗设计入门(一)

低功耗设计这个专题整理了好久,有一个月了,有图有证据: 然而最近一直有些烦心事.郁闷事,拖延了一下,虽然现在还是有点烦,但是还是先发表了吧.下面我们就来聊聊低功耗设计吧,由于文章比较长,因此我就不一次 ...

随机推荐

- js div的显示和隐藏

<head> <title></title> <style type="text/css"> div ...

- WPF 元素tag属性绑定一个属性或一个对象

<Window x:Class="CollectionBinding.CategoryDataTemp" xmlns="http://schemas. ...

- linux 修改 ssh 的端口号,启动hg服务

修改 ssh 的端口号 # vim /etc/ssh/sshd_config 将其中的 Port 改为 想要修改的端口号. # service sshd restart 启动hg服务 # hg ...

- VMNET 工作站

nattunnel 快速连接内网电脑 内网穿透.内网映射,支持微信小程序本地开发 支持WEB.远程桌面.多种TCP协议 官方主页:http://www.vmnet.cc 用途 一个可以快速连接局域网中 ...

- Git 将子文件夹分离为一个新的库

前面的需求 公司Android的项目上,想要将一些module抽取出来,作为一个可以被其它项目上使用的. 所以使用了git submodule的方案. 为了将代码库中的一个文件夹分离后,作为一个单独的 ...

- 图像滤镜艺术---Swirl滤镜

原文:图像滤镜艺术---Swirl滤镜 Swirl Filter Swirl 滤镜是实现图像围绕中心点(cenX,cenY)扭曲旋转的效果,效果图如下: 原图 效果图 代码如下: // ...

- UWP显示对话框

public static async void ShowMessage(string message) { var msgDialog = new Windows.UI.Popups.Message ...

- 使用内核对象Mutex可以防止同一个进程运行两次

用互斥法实现防止程序重复运行,使用内核对象Mutex可以防止同一个进程运行两次.注意:是名称相同的进程,而不是exe,因为exe程序可以改名. using System.Threading; publ ...

- SQL Server Update 所有表的某一列(列名相同,类型相同)数值

); WITH T AS (SELECT SchemaName = c.TABLE_SCHEMA, TableName = c.TABLE_NAME, ColumnName = c.COLUMN_NA ...

- eclipse 插件编写(一)

由于项目开发进程中有一些重复性的代码进行编写,没有任何业务逻辑,粘贴复制又很麻烦且容易出错,故想起做一个eclipse插件来满足一下自己的工作需要,同时记录一下,以供以后参考与共同学习.本文主要讲解一 ...