从RTL视图到Verilog语言-转可乐豆原创

从RTL视图到Verilog语言

曾经听过某位大牛都说:“当你的学习FPGA到一个境界的时候,你看到的硬件描述语言,将不再是单纯的语言,而是由一个个逻辑门组成的电路图,一旦达到这个境界,方能把代码写到极致!”

笔者是多么希望达到这种境界啊~~,可这种境界给笔者的感觉是那么的虚无缥缈。

前段时间笔者写了一篇名叫《关于FPGA(verilog)电平检测模块的易错点分析》的博客。我仔细看了看verilog对应的RTL视图,又将RTL视图与verilog对比,突然间略有感悟。

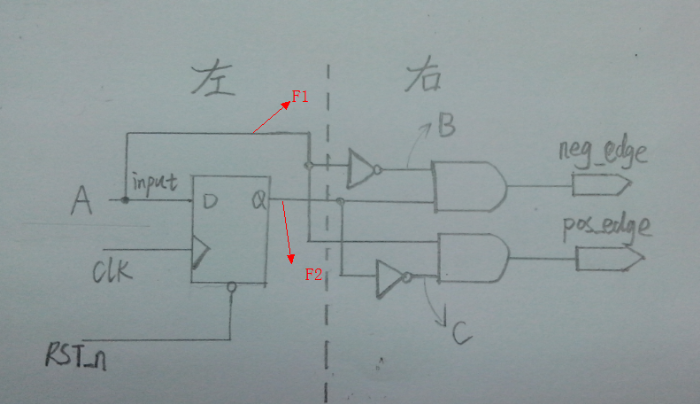

首先奉上笔者亲手绘制的逻辑图,呵呵~~请原谅它的丑陋。读者能从图直接想象对应出Verilog吗?

图中虚线左边:有一个输入A端口,输入时钟,复位信号和一个D触发器。

图中虚线右边:有两个非门和两个与门,和两个输出端口。

组合逻辑的输出与输入直接相关,时序逻辑的输出和原有状态也有关。

那么左边图就是我们常常所说的时序逻辑,而右边图就是组合逻辑。

先看看右边的视图,看看能不能把它想想成verilog,咦,似乎不难——不就是几个个输入经过几个非门和与门嘛。假设输入就叫F1和F2。

那么对图右边视图的上部分图而言:

wire neg_edge = !F1 & F2;

那么对图右边视图的上部分图而言:

wire pos_edge = F1 & !F2;

再看看左边的时序逻辑视图,我们发现F1和F2时序上是有关系的,F1与D触发器的输入直接相连,而F2与D触发器的输出直接相连。而对于D触发器而言,从输入到输出,从启动沿,到锁存沿。

F1和F2所间隔的正好是一个时钟周期(不考虑物理上的延时)。

好的,F1和F2的关系,我们也发现了。现在试着能不能根据左边的时序逻辑视图,写成Verilog时序逻辑。试试看,似乎也不难。

always @(posedge CLK)//时序逻辑肯定少不了时钟,对吧~

begin

F1 <= A; //F1与输入A端口直接相连

F2 <= F1; //F2与F1相隔一个时钟周期

end

最后,我们看看整张图,脑子中想象Verilog代码,结果出现了。

always @(posedge CLK or negedge RSTn)

if(!RSTn) begin F1 <= 1’b0 ; F2 <= 1’b0 ; end//加上一个异步复位

else

begin

F1 <= A; //F1与输入A端口直接相连

F2 <= F1; //F2与F1相隔一个时钟周期

end

wire neg_edge = !F1 & F2;

wire pos_edge = F1 & !F2;

现在给笔者的感觉,就是不需要在死记硬背这个电平检测模块,因为迷迷糊糊,笔者的脑袋里似乎浮现出一幅图,这幅图在指引这笔者如何写这个模块。

其实还有一个更好的记忆方法:

F1 Current State;F2 Previous State,

那么,!F1 & F2 == 1 就必须是之前值是1,现在值是0,那么检测的自然是下降沿。

同理: F1 & !F2 == 1 就必须是之前值是0,现在值是1,那么检测的自然是上升沿。

总结:从看到verilog就能反映出逻辑视图(RTL),笔者感觉很难,这需要大量经验的积累;反之,从看到逻辑视图就能反映出verilog,笔者感觉相对较易。如果我们先从容易的下手,慢慢的积累经验。说不定哪一天也能达到那位大牛所说的境界,哈哈~~

2013-11-12

——宋桓公

从RTL视图到Verilog语言-转可乐豆原创的更多相关文章

- 【iCore、iCore2 双核心板】EPCS 实验(SPI Flash)(基于Verilog语言)

_____________________________________ 深入交流QQ群: A: 204255896(1000人超级群,可加入) B: 165201798(500人超级群,满员) C ...

- 基于MATLAB2016b图形化设计自动生成Verilog语言的积分模块及其应用

在电力电子变流器设备中,常常需要计算发电量,由于电力电子变流器设备一般是高频变流设备,所以发电量的计算几乎时实时功率的积分,此时就会用到一个积分模块.发电量计算的公式如下:Q=∫P. FPGA由于其并 ...

- Verilog语言实现并行(循环冗余码)CRC校验

1 前言 (1) 什么是CRC校验? CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错功能, ...

- Verilog语言:还真的是人格分裂的语言

人气腹语术师天愿在现场披露了被人偶搭档夺取灵魂的腹语术师将妻子杀害的表演节目.天愿真的陷入了多重人格,命令自己杀害妻子和子的人偶的人格出现了.为了不(让自己)杀害和弟子登川有外遇的妻子,天愿提出委托想 ...

- Verilog 语言 001 --- 入门级 --- 编写一个半加器电路模块

Verilog 语言编写一个 半加器 电路模块 半加器 的电路结构: S = A 异或 B C = A 与 B 1. 程序代码 module h_adder (A, B, SO, CO); input ...

- FPGA基础(verilog语言)——语法篇

verilog语言简介 verilog语言是一种语法类似于c的语言,但是与c语言也有不同之处,比如: 1.verilog语言是并行的,每个always块都是同时执行,而c语言是顺序执行的 2.veri ...

- Verilog语言中的系统任务和系统函数

Verilog语言中预先定义了一些任务和函数,用于完成一些特殊的功能,它们被称为系统任务和系统函数,这些函数大多数都是只能在Testbench仿真中使用的,使我们更方便的进行验证. `timescal ...

- FPGA基础(verilog语言)——语法篇(续1)

上一篇文章提到了FPGA中一个模块基本结构,这篇文章开始介绍语法. 首先,我们学习一门语言都要从这门语言的单词学起,所以verilog中的关键词都有哪些呢?看下面: A:always.assign B ...

- Xilinx ISE14.1用Verilog语言实现一个半加器并测试

<一>建立一个工程 注:Xilinx ISE的安装在此不再过多说明,网上有参考资料 1.打开软件进入如下界面 2.创建工程 File-->New Project 3.创建文件(我取名 ...

随机推荐

- 易语言 史诗级Json处理 烁_Json模块!!!!

大家好,我是键盘上的魔手 * “************************”* “** 欢迎使用烁Json模块 **”* “** 作者:键盘上的魔手 **”* “** 微信号:codervip ...

- nyoj 1364-治安管理 (INT_MAX)

1364-治安管理 内存限制:128MB 时间限制:3000ms 特判: No 通过数:6 提交数:6 难度:2 题目描述: SZ市是中国改革开放建立的经济特区,是中国改革开放的窗口,已发展为有一定影 ...

- python:类3——魔法方法

一.魔法方法特点 被双上下滑线包围 魔法方法是面向对象的Python的一切,如果你不知道魔法方法,说明你还没能意识到面向对象的Python的强大(不是说Python脚本) 通过对制定方法的重写,完全可 ...

- django 中 css文件的调用

Django: 配置css文件 晚上搞了好久的css文件的调用,发现,我根本文件位置都放错了. 接下来要更改settings.py 和 urls.py 的设定. Settings.py 中应该: ur ...

- vue3.0wactch监听

<template> <div> <input v-model="count" /> </div> </template> ...

- 性能测试——记XX银行电票系统上线后宕机问题诊断优化

四月份我们公司负责的电票系统上线了,这个系统上线比客户方其他系统上线还特殊,是二期改造项目,旧系统数据还要整合抽取到新系统中继续使用,而且该系统不是增量型方式开发上线的,而且全部开发完后全国上线的,这 ...

- python3 之 内置函数Zip

python3 内置函数zip 一.简介: 该函数用于将多个可迭代对象作为参数,依次将对象中对应的元素打包成一个个元组,然后返回由这些元组组成的对象.二.实例1: name = ['张三','李四', ...

- WebGL简易教程(十三):帧缓存对象(离屏渲染)

目录 1. 概述 2. 示例 2.1. 着色器部分 2.2. 初始化/准备工作 2.2.1. 着色器切换 2.2.2. 帧缓冲区 2.3. 绘制函数 2.3.1. 初始化顶点数组 2.3.2. 传递非 ...

- spark graphX作图计算

一.使用graph做好友推荐 import org.apache.spark.graphx.{Edge, Graph, VertexId} import org.apache.spark.rdd.RD ...

- kafka官方的kafka-server-start.sh不能关闭kafka进程解决办法

vi kafka-server-stop.sh 把PIDS=$(ps ax | grep -i 'kafka\.Kafka' | grep java | grep -v grep | awk '{pr ...