JZ2440 裸机驱动 第9章 中断体系结构

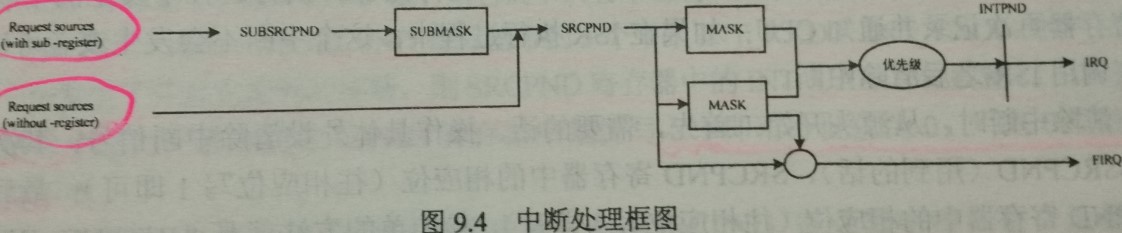

(1)“Request sources(without sub-register)”中的中断源被触发之后,SRCPND寄存器中

综上所述,使用中断的步骤如下:

sub lr, lr, # @计算返回地址

stmdb sp!, {r0-r12, lr} @保存使用的寄存器

... ... @处理中断

ldmia sp!, {r0-r12, pc}^ @中断返回

@^表示将spsr的值赋给cpsr

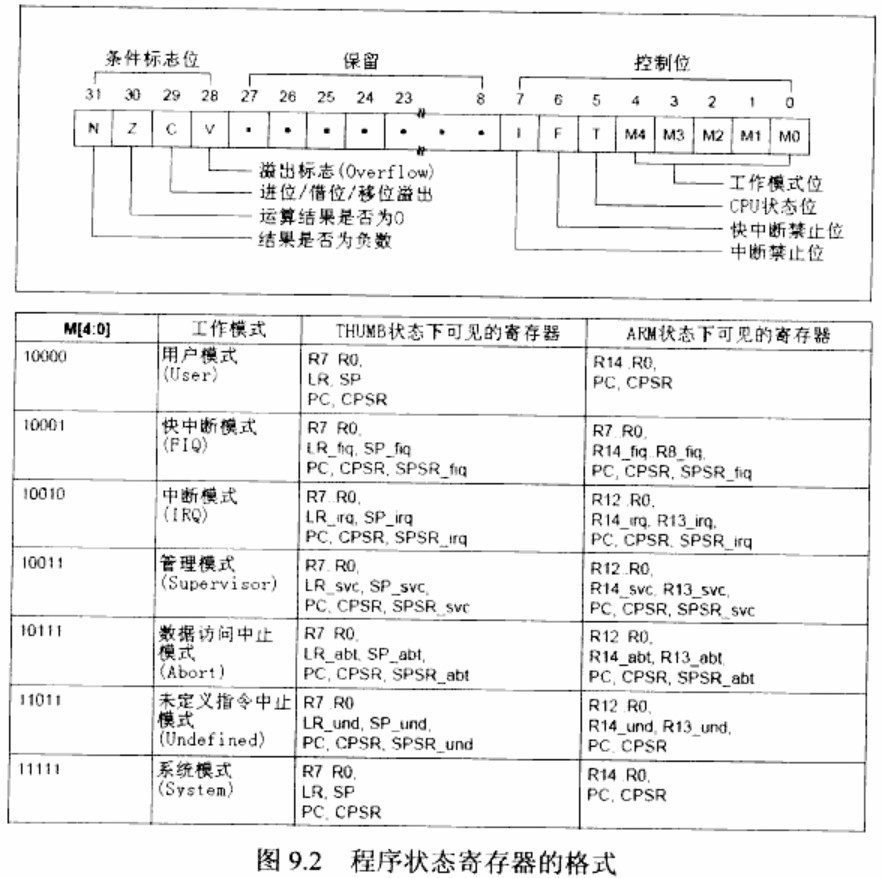

进入和退出IRQ

sub lr, lr # @计算计算返回地址

stmdb sp!, {r0-r7, lr} @保存使用到的寄存器

... ... @快速处理中断

sdmia sp!, {r0-r7, pc}^ @快速中断返回

@^表示将spsr的值赋给cpsr

进入和退出FIQ

@*************************************

@File:head.S

@功能:初始化、设置中断模式、系统模式的栈,设置好中断处理函数

@************************************* .extern main

.text

.global _start

_start:

@*************************************

@中断向量,本程序中,除了Reset和HandleIRQ外,其他异常都没有使用

@*************************************

b Reset @ 0x04:未定义指令终止模式的向量地址

HandleUndef:

b HandleUndef @ 0x08:管理模式的向量地址,通过SWI指令进入此模式

HandleSWI:

b HandleSWI @ 0x0c:指令预取终止导致的异常向量的向量地址

HandlePrefetchAbort:

b HandlePrefetchAbort @ 0x10:数据访问终止导致的异常向量地址

HandleDataAbort:

b HandleDataAbort @ 0x14:保留

HandleNotUsed:

b HandleNotUsed @ 0x18:中断模式的向量地址

b HandleIRQ @ 0x1c:快速中断模式的向量地址

HandleFIQ:

b HandleFIQ

head.S

接上面

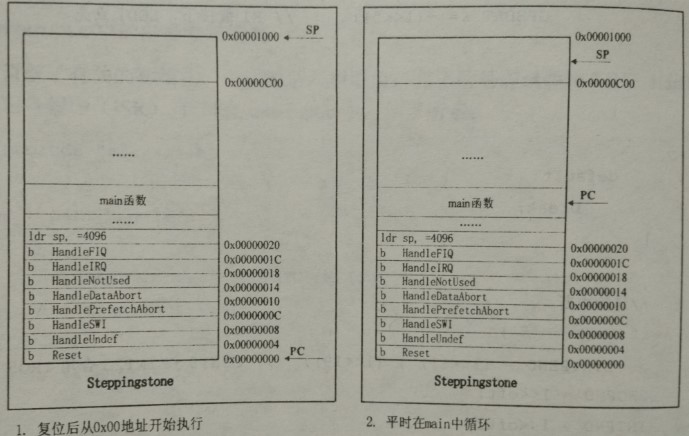

42行 Reset:

43行 ldr sp, = @设置栈指针,以下都是C函数,需要在调用前设置好栈

44行 bl disable_watch_dog @关闭看门狗

45行

46行 msr cpsr_c, #0xd2 @进入中断模式

47行 ldr sp, = @设置中断模式栈指针

48行

49行 msr cpsr_c, #0xdf @进入系统模式

50行 ldr sp, = @设置系统模式栈指针

51行 @起始复位之后,CPU就处于系统模式

52行 @前面的“ldr sp, =”完成同样的功能,此句可省略

53行

Reset代码

接上面

54行 bl init_led @初始化LED的GPIO管脚

55行 bl init_irq @调用中断管脚初始化函数,在init.c中

56行 msr cpsr_c, #0x5f @设置I-bit=,开启IRQ中断

57行

58行 ldr lr, =halt_loop @设置返回地址

59行 ldr pc, =main @调用main函数

60行 halt_loop:

61行 b halt_loop

接上面

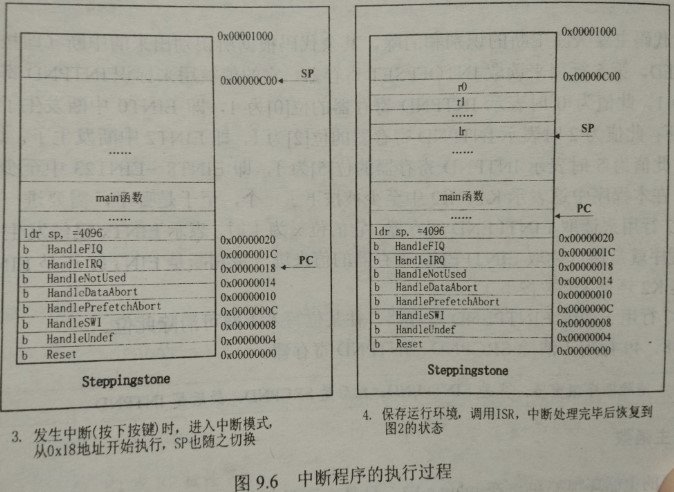

62行 HandleIRQ:

63行 sub lr, lr # @计算返回地址

64行 stmdb sp!, {r0-r12, lr} @保存使用到的寄存器

65行 @注意,此时的sp是中断模式的sp

66行 @初始值是上面设置的3072

67行

68行 ldr lr, =int_return @设置调用ISR即EINT_Handle函数后的返回地址,即为第71行指令的地址

69行 ldr pc, =EINT_Handle @调用中断服务函数,在interrupt.c中

70行 int_return:

71行 ldmia sp!, {r0-r12, pc}^ @中断返回,^表示将spsr的值复制到cpsr

72行

HandleIRQ

37行 /*

38行 * 初始化GPIO引脚为外部中断

39行 * GPIO引脚为外部中断时,默认低电平触发,IRQ方式(不用设置INTMOD)

40行 */

41行 void init_irq()

42行 {

// S2,S3对应的2根引脚设为中断引脚 EINT0,ENT2

43行 GPFCON &= ~(GPF0_msk | GPF2_msk);

44行 GPFCON |= GPF0_eint | GPF2_eint;

// S4对应的引脚设为中断引脚EINT11

GPGCON &= ~GPG3_msk;

GPGCON |= GPG3_eint;

45行

46行 //对于EINT11,需要在EINTMASK寄存器中使能它们

47行 EINTMASK &= ~(<<);

48行

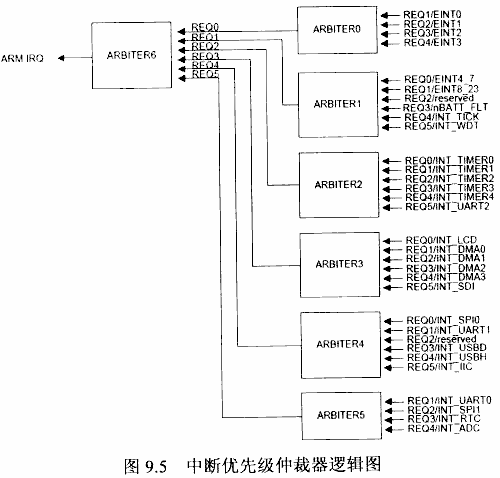

49行 /*

50行 *设定优先级

51行 *ARB_SEL0 = 00b,ARB_MODE0 = 0;REQ1 > REQ3,即EINT0 > EINT2

52行 *仲裁器1、6无须设置

53行 *最终:

54行 *EINT0 > EINT2 > EINT11, EINT19、即K4 > K3 > K1、K2

55行 *EINT11和EINT19的优先级相同

56行 */

57行 PRIORITY = (PRIORITY & ((~0x01) | (0x3 << ))) | (0x0 << );

58行

59行 //EINT0、EINT2、EINT8_23使能

60行 INTMSK &= (~( << )) & (~( << )) & (~( << ));

61行 }

init.c

#include "s3c24xx.h" void EINT_Handle()

{

unsigned long oft = INTOFFSET;

unsigned long val; switch( oft )

{

// S2被按下

case :

{

GPFDAT |= (0x7<<); // 所有LED熄灭

GPFDAT &= ~(<<); // LED1点亮

break;

} // S3被按下

case :

{

GPFDAT |= (0x7<<); // 所有LED熄灭

GPFDAT &= ~(<<); // LED2点亮

break;

} // K4被按下

case :

{

GPFDAT |= (0x7<<); // 所有LED熄灭

GPFDAT &= ~(<<); // LED4点亮

break;

} default:

break;

} //清中断

if( oft == )

EINTPEND = (<<); // EINT8_23合用IRQ5

SRCPND = <<oft;

INTPND = <<oft;

}

interrupt.c

int main()

{

while();

return ;

}

main.c

JZ2440 裸机驱动 第9章 中断体系结构的更多相关文章

- JZ2440 裸机驱动 第14章 ADC和触摸屏接口

本章目标: 了解S3C2410/S3C2440和触摸屏的结构: 了解电阻触摸屏的工作原理和等效电路图: 了解S3C2410/S3C2440触摸屏控制器的多种工作模式: ...

- JZ2440 裸机驱动 第12章 I2C接口

本章目标: 了解I2C总线协议: 掌握S3C2410/S3C2440中I2C接口的使用方法: 12.1 I2C总线协议及硬件介绍 12.1.1 I2C总线协议 1 I2C总线的概念 2 I2C总线的信 ...

- JZ2440 裸机驱动 第10章 系统时钟和定时器

本章目标 了解S3C2410/S3C2440的时钟体系结构 掌握通过设置MPLL改变系统时钟的方法 掌握在不同的频率下设置存储控制器的方法 掌握PWM定时器的用法 ...

- JZ2440 裸机驱动 第5章 GPIO接口

本章目标: 掌握嵌入式开发的步骤:编程.编译.烧写程序.运行 通过GPIO的操作了解软件如何控制硬件 5.1 GPIO硬件介绍 S3C2440A有130个多功能输入/输出口引脚 ...

- JZ2440 裸机驱动 第13章 LCD控制器(1)

本章目标 了解LCD显示器的接口及时序: 掌握S3C2410/S3C2440 LCD控制器的使用方法: 了解帧缓冲区的概念,掌握如何设置帧缓冲区来显示图像: 13.1 LCD和LCD控制器 13.1 ...

- JZ2440 裸机驱动 第11章 通用异步收发器UART

本章目标: 了解UART原理: 掌握S3C2410/S3C2440中UART的使用 11.1 UART原理及UART内部使用方法 11.1.1 UART原理说明 UART用于传输串行数据: ...

- JZ2440 裸机驱动 第6章 存储控制器

本章目标: 了解S3C2410/S3C2440地址空间的布局 掌握如何通过总线形式访问扩展的外设,比如内存.NOR Flash.网卡等 ························ ...

- JZ2440 裸机驱动 第8章 NAND Flash控制器

本章目标 了解NAND Flash 芯片的接口 掌握通过NAND Flash控制器访问NAND Flash的方法 8.1 NAND Flash介绍和NAND Flash控制器使用 NAND ...

- JZ2440 裸机驱动 第7章 内存管理单元MMU

本章目标: 了解虚拟地址和物理地址的关系: 掌握如何通过设置MMU来控制虚拟地址到物理地址的转化: 了解MMU的内存访问权限机制: 了解TLB.Cache.Write ...

随机推荐

- 重启oracle数据库的操作方法

在实际的应用中,有时候工作数据库需要重新启动.本文介绍了一个特别实用的操作步骤,希望对大家有所帮助. 1. 停应用层的各种程序 2. 停Oralce的监听进程 $ lsnrctl stop 3. 在独 ...

- 拷贝构造函数(define)

1.拷贝构造函数是一种特殊的构造函数,具有单个形参,此形参是对该类型的引用. 当定义一个新对象并用一个同类型的对象对它进行初始化时,将显示使用拷贝构造函数. 2.当将该类型的对象传递给函数或从函数返回 ...

- anu - children

import { _flattenChildren } from "./createElement"; export const Children = { only(childre ...

- css3 制作平滑过度动画

-webkit-transition(属性渐变) -webkit-transition:CSS属性(none|all|属性) 持续时间 时间函数 延迟时间 CSS属性(transition-pr ...

- STM32 Flash 永久用户数据空间

/********************************************************************************* * STM32 Flash 永久用 ...

- I.MX6 Linux Qt 启动流程跟踪

/************************************************************************** * I.MX6 Linux Qt 启动流程跟踪 ...

- SUST OJ 1675: Fehead的项目(单调栈)

1675: Fehead的项目 时间限制: 1 Sec 内存限制: 128 MB提交: 41 解决: 27[提交][状态][讨论版] 题目描述 Fehead俱乐部接手了一个项目,为了统计数据,他们 ...

- Sql语句中两个比较迷糊的概念:“连接查询” 与 “外键约束”

Sql语句中两个比较迷糊的概念:“连接查询” 与 “外键约束 Sql 中的连接查询:就是为了避免笛卡尔积,因为涉及到多表查询的化,不使用连接查询,会先将多个互相乘,求出笛卡尔积,然后在在里面查询符合的 ...

- 八皇后 递归or迭代

递归: #include <iostream> #include <cstdlib> #include <cstdio> using namespace std; ...

- Python需要知道的知识点

1.所有数据类型都自带布尔值,布尔值为假的数据类型 包括( 空字符串,空列表,空字典,空集合).数字(0).None类型 2.Python实现int的时候有个小整数池.为了避免因创建相同的值而重复申请 ...