FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍

1、分频

FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大。一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对复杂一些,小数分频则更难一些。

1)偶分频系数=时钟输入频率/时钟输出频率=50MHz/5MHz=10,则计数器在输入时钟的上升沿或者下降沿从0~(10-1)计数,而输出时钟在计数到4和9时翻转。

2)奇分频系数=50MHz/10MHz=5,则两个计数器分别在输入时钟的上升沿和下降沿从0~ (5-1)计数,而相应的上升沿和下降沿触发的输出时钟在计数到1和4时翻转,最后将两个输出时钟进行或运算从而得到占空比为50%的5分频输出时钟。

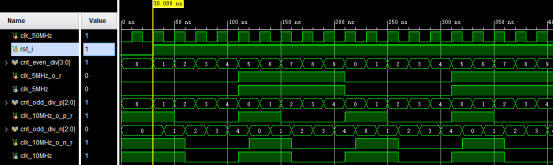

下图所示为50MHz输入时钟进行10分频和5分频的仿真波形

2、倍频

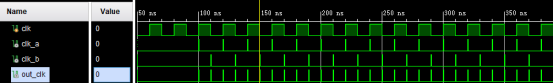

两种思路:PLL(锁相环)或者利用门延时来搭建

注意:此仿真是利用FPGA内部电路延迟来实现的倍频需要在后仿真下才能看到波形,在行为仿真下无法得到输出波形。

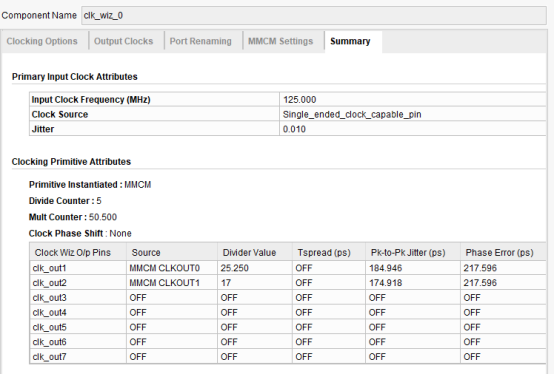

一、时钟IP的分频倍频相关参数说明

输入时钟:clk_in1(125MHz)

输出时钟:clk_out1(50MHz),clk_out2(74.25MHz)

则VCO Freq=1262.5MHz=clk_in1*CLKFBOUT_MULT_F/DIVCLK_DIVIDE=125*50.5/5

clk_out1(50MHz)=VCO_Freq/Divide=1265.5/25.250

clk_out2(74.25MHz)=VCO_Freq/Divide=1265.5/17

二、MMCME4_ADV

MMCME4是一种混合信号块,用于支持频率合成、时钟网络设计和减少抖动。基于相同的VCO频率,时钟输出可以有单独的分频、相移和占空比。此外,MMCME4还支持动态移相和分数除法

(1)Verilog 初始化模板

MMCME4_ADV #(

.BANDWIDTH("OPTIMIZED"), // Jitter programming

.CLKFBOUT_MULT_F(5.0), // Multiply value for all CLKOUT

.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB

.CLKFBOUT_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.CLKIN1_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz).

.CLKIN2_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz).

.CLKOUT0_DIVIDE_F(1.0), // Divide amount for CLKOUT0

.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0

.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0

.CLKOUT0_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.CLKOUT1_DIVIDE(1), // Divide amount for CLKOUT (1-128)

.CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT1_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.CLKOUT2_DIVIDE(1), // Divide amount for CLKOUT (1-128)

.CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT2_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT2_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.CLKOUT3_DIVIDE(1), // Divide amount for CLKOUT (1-128)

.CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT3_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT3_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.CLKOUT4_CASCADE("FALSE"), // Divide amount for CLKOUT (1-128)

.CLKOUT4_DIVIDE(1), // Divide amount for CLKOUT (1-128)

.CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT4_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT4_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.CLKOUT5_DIVIDE(1), // Divide amount for CLKOUT (1-128)

.CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT5_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT5_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.CLKOUT6_DIVIDE(1), // Divide amount for CLKOUT (1-128)

.CLKOUT6_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT6_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT6_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE)

.COMPENSATION("AUTO"), // Clock input compensation

.DIVCLK_DIVIDE(1), // Master division value

.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN

.IS_CLKIN1_INVERTED(1'b0), // Optional inversion for CLKIN1

.IS_CLKIN2_INVERTED(1'b0), // Optional inversion for CLKIN2

.IS_CLKINSEL_INVERTED(1'b0), // Optional inversion for CLKINSEL

.IS_PSEN_INVERTED(1'b0), // Optional inversion for PSEN

.IS_PSINCDEC_INVERTED(1'b0), // Optional inversion for PSINCDEC

.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN

.IS_RST_INVERTED(1'b0), // Optional inversion for RST

.REF_JITTER1(0.0), // Reference input jitter in UI (0.000-0.999).

.REF_JITTER2(0.0), // Reference input jitter in UI (0.000-0.999).

.SS_EN("FALSE"), // Enables spread spectrum

.SS_MODE("CENTER_HIGH"), // Spread spectrum frequency deviation and the spread type

.SS_MOD_PERIOD(10000), // Spread spectrum modulation period (ns)

.STARTUP_WAIT("FALSE") // Delays DONE until MMCM is locked

)

MMCME4_ADV_inst (

.CDDCDONE(CDDCDONE), // 1-bit output: Clock dynamic divide done

.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock

.CLKFBOUTB(CLKFBOUTB), // 1-bit output: Inverted CLKFBOUT

.CLKFBSTOPPED(CLKFBSTOPPED), // 1-bit output: Feedback clock stopped

.CLKINSTOPPED(CLKINSTOPPED), // 1-bit output: Input clock stopped

.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0

.CLKOUT0B(CLKOUT0B), // 1-bit output: Inverted CLKOUT0

.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1

.CLKOUT1B(CLKOUT1B), // 1-bit output: Inverted CLKOUT1

.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2

.CLKOUT2B(CLKOUT2B), // 1-bit output: Inverted CLKOUT2

.CLKOUT3(CLKOUT3), // 1-bit output: CLKOUT3

.CLKOUT3B(CLKOUT3B), // 1-bit output: Inverted CLKOUT3

.CLKOUT4(CLKOUT4), // 1-bit output: CLKOUT4

.CLKOUT5(CLKOUT5), // 1-bit output: CLKOUT5

.CLKOUT6(CLKOUT6), // 1-bit output: CLKOUT6

.DO(DO), // 16-bit output: DRP data output

.DRDY(DRDY), // 1-bit output: DRP ready

.LOCKED(LOCKED), // 1-bit output: LOCK

.PSDONE(PSDONE), // 1-bit output: Phase shift done

.CDDCREQ(CDDCREQ), // 1-bit input: Request to dynamic divide clock

.CLKFBIN(CLKFBIN), // 1-bit input: Feedback clock

.CLKIN1(CLKIN1), // 1-bit input: Primary clock

.CLKIN2(CLKIN2), // 1-bit input: Secondary clock

.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2

.DADDR(DADDR), // 7-bit input: DRP address

.DCLK(DCLK), // 1-bit input: DRP clock

.DEN(DEN), // 1-bit input: DRP enable

.DI(DI), // 16-bit input: DRP data input

.DWE(DWE), // 1-bit input: DRP write enable

.PSCLK(PSCLK), // 1-bit input: Phase shift clock

.PSEN(PSEN), // 1-bit input: Phase shift enable

.PSINCDEC(PSINCDEC), // 1-bit input: Phase shift increment/decrement

.PWRDWN(PWRDWN), // 1-bit input: Power-down

.RST(RST) // 1-bit input: Reset

);

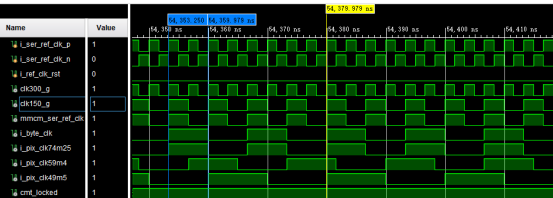

(2)本实验仿真所用参数配置说明及部分端口调用

1、参数配置说明

本实验通过输入时钟CLKIN1(150MHz),实现输出反馈时钟CLKFBOUT(150MHz)、输出时钟CLKOUT0(74.25MHz)、输出时钟CLKOUT1(74.25MHz)、输出时钟CLKOUT2(59.4MHz)、输出时钟CLKOUT3(49.5MHz)。其关键参数设置如下

CLKFBOUT_MULT_F(1.98) //指定如果需要不同的频率,则对相关的CLKOUT时钟输出进行分数分割的乘法系数。这个数字与CLKFBOUT_MULT_F和DIVCLK_DIVIDE值的组合将决定输出频率

DIVCLK_DIVIDE(1) // 指定所有输出时钟相对于输入时钟的除法因子

CLKOUT0_DIVIDE_F(4)、 CLKOUT1_DIVIDE(4)、CLKOUT2_DIVIDE(5)、CLKOUT3_DIVIDE(6) //指定分频输出的除法因子从而输出不同的频率

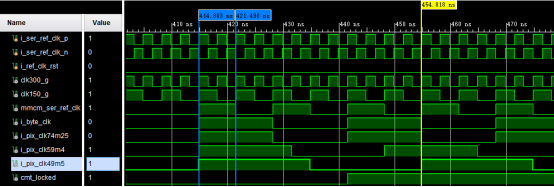

注:输入150MHz 乘以倍频因子1.98,得到倍频频率297MHz ,由于DIVCLK_DIVIDE(1)设置为1,则分频的参考时钟为297/1=297;输出反馈时钟也为:297/1=297;那么其它CLKOUT_DIVIDE_F、CLKOUT1_DIVIDE~CLKOUT6_DIVIDE的分频根据设置的分频系数结合分频参考时钟297MHz而定,即参考分频时钟/相应分频系数,比如这里的297/4;297/5;297/6。其仿真波形如下图1所示

图1

图2所示的波形仿真是改变了此参数设置:DIVCLK_DIVIDE(2)

图2

2、端口调用

MMCME4_ADV #(

.BANDWIDTH("OPTIMIZED"), // Jitter programming (HIGH, LOW, OPTIMIZED)

.CLKFBOUT_MULT_F(1.98), //

.CLKFBOUT_PHASE(0.0), //

.CLKIN1_PERIOD(6.6),

.CLKOUT0_DIVIDE_F(4), //

.CLKOUT1_DIVIDE(4),

.CLKOUT2_DIVIDE(5),

.CLKOUT3_DIVIDE(6),

.CLKOUT0_DUTY_CYCLE(0.5),

.CLKOUT1_DUTY_CYCLE(0.5),

.CLKOUT2_DUTY_CYCLE(0.5),

.CLKOUT3_DUTY_CYCLE(0.5),

.CLKOUT0_PHASE(0.0),

.CLKOUT1_PHASE(0.0),

.CLKOUT2_PHASE(0.0),

.CLKOUT3_PHASE(0.0),

.DIVCLK_DIVIDE(2), // Master division value (1-106)

.REF_JITTER1 (0.100)

)

MMCME4_ADV_inst (

// Clock Outputs outputs: User configurable clock outputs

.CLKOUT0(i_byte_clk), // 1-bit output: CLKOUT0

.CLKOUT0B(), // 1-bit output: Inverted CLKOUT0

.CLKOUT1(i_pix_clk74m25), // 1-bit output:

.CLKOUT1B(), // 1-bit output: Inverted CLKOUT1

.CLKOUT2(i_pix_clk59m4), // 1-bit output: CLKOUT2

.CLKOUT2B(), // 1-bit output: Inverted CLKOUT2

.CLKOUT3(i_pix_clk49m5), // 1-bit output: CLKOUT3

.CLKOUT3B(), // 1-bit output: Inverted CLKOUT3

// Feedback outputs: Clock feedback ports

.CLKFBOUT(mmcm_ser_ref_clk), // 1-bit output: Feedback clock

.CLKFBOUTB(), // 1-bit output: Inverted CLKFBOUT

// Status Ports outputs: MMCM status ports

.LOCKED(cmt_locked), // 1-bit output: LOCK

// Clock Inputs inputs: Clock inputs

.CLKIN1(clk150_g), // 1-bit input: Primary clock

// Control Ports inputs: MMCM control ports

.PWRDWN(1'b0), // 1-bit input: Power-down

.RST(i_ref_clk_rst) // 1-bit input: Reset

);

附:UltraScale+的高级混合模式时钟管理的三种原语库

MMCME3_ADV

The MMCME3 is a mixed signal block designed to support frequency synthesis, clock network

deskew, and jitter reduction. The clock outputs can each have an individual divide, phase shift

and duty cycle based on the same VCO frequency. Additionally, the MMCME3 supports dynamic

phase shifting and fractional divides.

MMCME3_BASE

The MMCME3 is a mixed signal block designed to support frequency synthesis, clock network

deskew, phase adjustment and jitter reduction. The MMCME3_BASE supports a subset of the

more common features and thus is easier to instantiate and use compared to the full features

MMCME3_ADV.

MMCME4_ADV

The MMCME4 is a mixed signal block designed to support frequency synthesis, clock network

deskew, and jitter reduction; The clock outputs can each have an individual divide, phase shif

and duty cycle based on the same VCO frequency. Additionally, the MMCME4 supports dynamic

phase shifting and fractional divides.

FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)的更多相关文章

- [置顶]

基于FPGA的VGA简易显存设计&NIOS ii软核接入

项目简介 本项目基于Altera公司的Cyclone IV型芯片,利用NIOS II软核,2-port RAM与时序控制模块,实现64*48分辨率的显存(再大的显存板载资源m9k不够用) 实现效果如下 ...

- 基于AXI4总线卷积FPGA加速IP核的尝试

本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面.使用的硬件平台是Zedboard. 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块 ...

- 循序渐进做项目系列(2):最简单的C/S程序——消息异步调用与消息同步调用

上篇博客 循序渐进做项目系列(1):最简单的C/S程序——让服务器来做加法 实现了一个最简单的C/S程序,即让服务器来做加法.当时为了通俗易懂采用了消息异步调用的方式.今天我们要采用消息同步调用的方式 ...

- Hook任务栏时钟窗口(原理其实很简单,就是注入DLL到时钟窗口进程(explorer.exe))

用过一些日历软件的小伙伴应该都知道它们都实现了在时钟窗口上的Hook,也就是屏蔽了系统原有的功能,实现自己的功能 某日历软件Hook时钟窗口后的效果 经过一番研究,发现原理其实很简单,就是注入DLL到 ...

- FPGA图像处理之行缓存(linebuffer)的设计一

FPGA图像处理之行缓存(linebuffer)的设计一 作者:OpenS_Lee 1 背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- Shell基础(一):Shell基础应用、简单Shell脚本的设计、使用Shell变量、变量的扩展应用

一.Shell基础应用 目标: 本案例要求熟悉Linux Shell环境的特点,主要练习以下操作: 1> 切换用户的Shell环境 2> 练习命令历史.命令别名 3 ...

- FPGA内部IP核DDS

项目当中需要正弦信号与余弦信号,首先想到了DDS芯片,例如AD9833.AD9834.由于还需要用FPGA 做一些数据处理,后来干脆直接用FPGA 内部的DDSIP核,同时根据IP核内部的相位累加 ...

- GVIM与模板——让FPGA开发变得更简单

还在使用FPGA开发环境自带的代码编辑器?还在逐个字母敲击冗长重复的代码?明德扬至简设计法让你快速提高代码编写效率!利用GVIM这一高效的编辑工具并添加自定义模板,通过简短的脚本命令即可自动生成所有常 ...

随机推荐

- Java框架-MyBatis三剑客之MyBatis Generator(mybatis-generator MBG插件)详解

生成器设计思路: 连接数据库 -> 获取表结构 -> 生成文件 1 下载与安装 官网文档入口 最方便的 maven 插件使用方式 贴至pom 文件 2 新建配置文件 填充配置信息(官网示例 ...

- jenkins 与 gitlab 的持续集成

前言介绍 gitlab与jenkins的安装部署请参考之前的文章:这里介绍一下jenkins与gitlab结合的好处. gitlab可以自己实现CICD功能,jenkins也可以结合其他工具来实现CI ...

- HDU 2087 剪花布条 KMP极其初级之入门题(KMP模板在这里)

Problem Description 一块花布条,里面有些图案,另有一块直接可用的小饰条,里面也有一些图案.对于给定的花布条和小饰条,计算一下能从花布条中尽可能剪出几块小饰条来呢? Input ...

- Go语言实现:【剑指offer】旋转数组的最小数字

该题目来源于牛客网<剑指offer>专题. 把一个数组最开始的若干个元素搬到数组的末尾,我们称之为数组的旋转. 输入一个非递减排序的数组的一个旋转,输出旋转数组的最小元素. 例如数组{3, ...

- java架构之路-(微服务专题)ribbon的基本使用和内部算法的自我实现

上次回归: 上次我们主要说了,我们的注册中心nacos的使用,如我们的命名空间.分组.集群.版本等是如何使用的,如果是这样呢?我们现在有三个用户服务和三个订单服务,我们应该如何分发这些请求呢?都请求到 ...

- one-hot编码(pytorch实现)

n = 5 #类别数 indices = torch.randint(0, n, size=(15,15)) #生成数组元素0~5的二维数组(15*15) one_hot = torch.nn.fun ...

- qt creator源码全方面分析(2-3-1)

目录 Using External Tools 使用Qt语言学家 预览QML文件 使用外部文本编辑器 配置外部工具 Using External Tools 您可以直接从Qt Creator中使用外部 ...

- 【学习底层原理系列】重读spring源码1-建立基本的认知模型

开篇闲扯 在工作中,相信很多人都有这种体会,与其修改别人代码,宁愿自己重写. 为什么? 先说为什么愿意自己写: 从0-1的过程,是建立在自己已有认知基础上,去用自己熟悉的方式构建一件作品.也就是说, ...

- CentOS7重置密码

#在vmlinuz段最后添加rd.break Ctrl+X启动 rd.break #在linux16/linux/linuxefi所在参数行尾添加以下内容 init=/bin/sh #此时,可使用mo ...

- Angular常用命令

一. Angular常用命令 1. ng new 文件夹名 (新建项目,选择y使用路由) 2. ng serve --open (默认浏览器运行项目) 3. ng serve --port 6060 ...