FPGA内部IP核DDS

项目当中需要正弦信号与余弦信号,首先想到了DDS芯片,例如AD9833、AD9834。由于还需要用FPGA 做一些数据处理,后来干脆直接用FPGA 内部的DDSIP核,同时根据IP核内部的相位累加端口,设置触发信号,使得触发信号更加准时,并且通过PSD 算法计算有效值,相位差更小,精度更高。

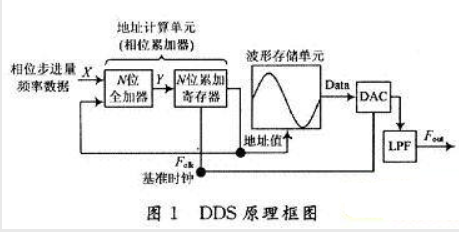

首先了解DDS的原理:

1、 DDS技术是根据奈奎斯特取样定律,从连续信号的相位出发,将正弦信号取样,编码,量化,形成一个正弦函数表,存在EPROM中,合成时,通过改变相位累加器的频率字来改变相位增量,也就是我们所称的步长。相位增量的不同导致一个周期内取样点的不同,在时钟频率即采样频率不变的情况下,通过相位的改变来改变频率。

2、 DDS 以数控振荡器的方式,产生频率、相位可控制的正弦,电路包括了基准时钟源、相位累加器、相位调制器、正弦ROM 查找表、D/A 转换 器和低通滤波器等。 频率控制字N 和相位控制字M 分别控制DDS 所输出的正弦波的频率和相 位。DDS 系统的核心是相位累加器,它由一个N 位累加器与N 位相位寄存器构成。时钟脉冲每触发一次, 累加器便将频率控制数据与相位寄存器输出的累加相位数据相加, 然后把相加后的结果送至相位寄存器的数据输入端。 相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端, 以使加法器在下一个时钟的作用下继续与频率控制数据相加。 这样, 相位累加器在参考时钟的作用下将进行线性相位累加, 当相位累加器累加满时, 就会产生一次溢出, 以完成一个周期性的动作, 这个周期就是DDS 合成信号的一个频率周期, 相位累加器的溢出频率就是DDS 输出的信号频率。 相位寄存器的输出与相位控制字相加, 结果作为正弦查找表的地址。 查找表由ROM 构成, 其内部存有一个完整周期正弦波的数字幅度信息, 每个查找表的地址对应正弦波中的一个相位点。 查找表把输入地址信息映射成正弦波幅度信号, 同时输出到D/A 转换器的输入端, 通过D/A 可将数字量形式的波形幅值转换成所要求的合成频率模拟量形式信号。 低通滤波器用于衰减和滤除不需要的取样分量, 以便输出频谱纯净的正弦波信号。

ISE DDS IP核设置如下图,输出正弦信号为12位,为了实现频率的高分辨率,需要将相位增加足够的小,因此相位宽度为33位。

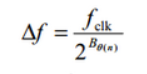

有DDS IP核datasheet当中,可以 看到分辨率计算公式、相位增量公式如下:

当输出38Khz正弦信号,频率分辨为0.01Hz,得到相位增量位宽为33位(50M/0.01=5000000000~~~~~~~BIT=33)

相位增量为38k*8589934592/50M=6528350。

wire [31:0] phase_out;

wire [32:0] poff_in;

assign poff_in = 33'd0;

wire [32:0] data_in; //DDS相位增量

assign data_in = 33'd6528350;

dds dds_inst_M0 (

.clk(clk), // input clk

.pinc_in(data_in), // input [32 : 0] pinc_in

.poff_in(poff_in), // input [32 : 0] poff_in

.cosine(cosine), // output [11 : 0] cosine

.sine(sine), // output [11 : 0] sine

.phase_out(phase_out) // output [32 : 0] phase_out

);

使用ModelSim仿真如下图

FPGA内部IP核DDS的更多相关文章

- 基于AXI4总线卷积FPGA加速IP核的尝试

本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面.使用的硬件平台是Zedboard. 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块 ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- FPGA VGA+PLL+IP核笔记

1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ.2.分辨率使用了800*600@72HZ.3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色.VGA图形基 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- 7 Series GTP IP核使用总结 IP核配置篇

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级.本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用.本文是 ...

- 7系列高速收发器总结 GTP IP核使用篇

上一篇7系列收发器博文讲解了GTP IP核的基本配置,本文继续分析如何将它使用起来.生成IP核后打开example design,先看看工程中包含的文件结构. 顶层文件下包含了gtp ip核系统顶层文 ...

- 浅析Xilinx 三速以太网MAC IP核

之前在使用Altera的三速以太网MAC IP的基础上,完成了UDP协议数据传输.此次为了将设计移植到xilinx FPGA上,需要用到xilinx的三速以太网MAC IP核,当然也可以自己用HDL编 ...

随机推荐

- Spring Cloud Alibaba基础教程:Sentinel Dashboard中修改规则同步到Apollo

在之前的两篇教程中我们分别介绍了如何将Sentinel的限流规则存储到Nacos和Apollo中.同时,在文末的思考中,我都指出了这两套整合方案都存在一个不足之处:不论采用什么配置中心,限流规则都只能 ...

- Python-使用tkinter实现的摇骰子小游戏

贴吧看到的一个求助题,大致需求是:3个人摇骰子,每人摇3次,点数之和最大的获胜,支持玩家名称输入.我觉得这个题目挺有意思的,做了个界面程序,欢迎大家交流指正~ #!usr/bin/env python ...

- CSS三种布局模型是什么?

在网页中,元素有三种布局模型:流动模型(Flow) 默认的.浮动模型 (Float).层模型(Layer).下面我们来看一下这三种布局模型. 三种布局模型介绍: 1.流动模型(Flow) 流动(Flo ...

- Web移动端 自适应缩放界面

在开发App端的网页时,要适配iphone.ipad.ipod.安卓等各种机型,一般是直接使用em.px转em.界面缩放. 本章是通过将界面缩放,等比例显示在各机型上.过程中遇到了些问题和大坑~ 然后 ...

- 重学 Java 设计模式:实战策略模式「模拟多种营销类型优惠券,折扣金额计算策略场景」

作者:小傅哥 博客:https://bugstack.cn - 原创系列专题文章 沉淀.分享.成长,让自己和他人都能有所收获! 一.前言 文无第一,武无第二 不同方向但同样努力的人,都有自身的价值和亮 ...

- 「疫期集训day13」雾天

我们千里迢迢赶来这里支援协约国----与德军正面交锋的美国士兵 今天考试签到题都没A,失误重大,T1几周前做过的拓扑排序板子都没写,T2失误在没敢调试,对自己信心不足,30分钟写了个DP,几分钟没调出 ...

- Windows 最值得推荐的装机必备“神器”软件大合集

工欲善其事,必先利其器.每个人在平时使用电脑的过程中,多多少少都会积累一些好用的软件,我也不例外,从业这么多年,收藏了许多不错的软件,通过这篇文章都分享给大家.如果觉得不错,请把这篇文章分享给你的小伙 ...

- saver 的保存与恢复

模型保存,先要创建一个Saver对象:saver=tf.train.Saver(), max_to_keep 是用来设置保存模型的个数,默认为5,即保存最近的五个模型,saver=tf.train.S ...

- spring boot实现简单的登录拦截

一.思路 1.在pom.xml导入相关包 2.先写个简单的认证适配器(WebSecurityConfig extends WebSecurityConfigurerAdapter),登录拦截后就会跳转 ...

- Go的100天之旅-04基础数据类型

基础数据类型 在变量的定义中,我们讲了每个变量是有类型的,类型在计算机中是用来约束数据的解释.Go语言和其它计算机语言一样,提供丰富了丰富的数据类型,我们就来看看到底有哪些类型,同时也可以比较一下它和 ...