(转)Quartus II和Modelsim的联合仿真(详细)

这篇文章不需要在modelsim中建库、映射、建工程等一些繁琐的步骤,直接使用modelsim中的默认work库。使用quartus+modelsim联合仿真。

首先推荐一篇文章 http://www.cnblogs.com/emouse/archive/2012/07/08/2581223.html

首先,根据上一篇文章,建立一个testbench模板;

第一次用modelsim+quartus的时候需要在quartus中设置modelsim的路径,quartus->tools->general->EDA tool options ,在右边选择modelsim的安装路径,如下图:

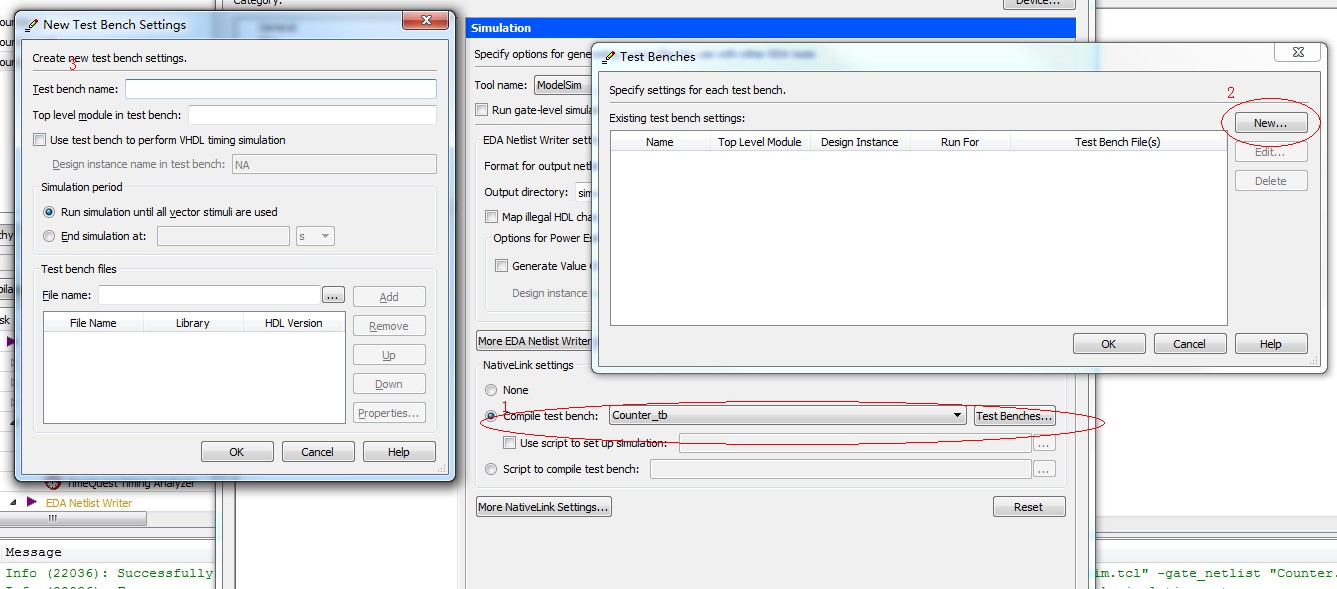

然后在Quartus->setting->simulation中设置仿真工具(选择modelsim),输出netlist语言(选择 VHDL or Verilog),然后在下面添加testbench;如下图:

到edit test settings这个步骤的时候需要说明一下,其中test bench name可以自己定,下面两个的内容根据test bench文件中的内容而定。

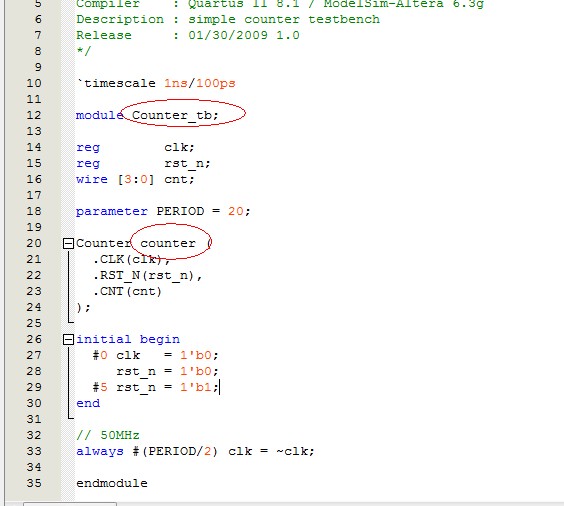

比如说我用verilog写的test bench如下:

那么我下面两个的名字就为分别为 Counter_tb和counter 如下图:

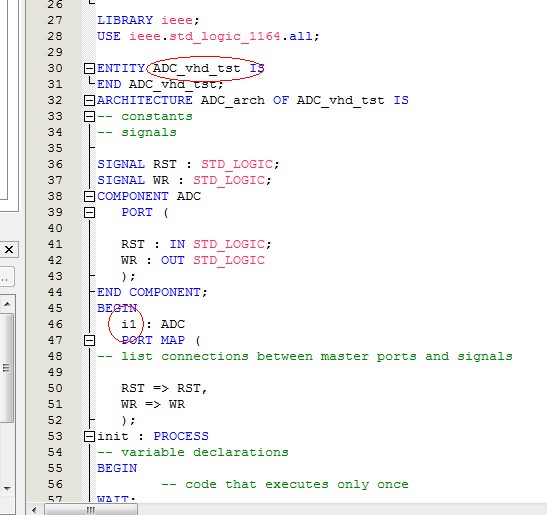

如果是用VHDL写的test bench,如下图

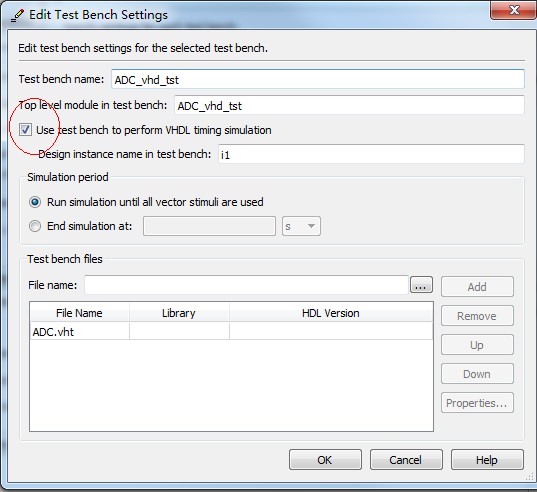

那么我们下面两个的内容就是ADC_vhd_tst和i1,如同下图

这样设置了之后,就可以从quartus中直接进行RTL仿真和门极(时序)仿真了,(上图打勾就代表使用时序仿真);具体为什么要这么设置请看http://www.uio.no/studier/emner/matnat/fys/FYS4220/h12/documentation/quartus_modelsim_setup.pdf 如果不这么设置的话,可以进行RTL仿真,但是不能进行门级(时序)仿真,门级(时序)仿真的时候会报 Failed to find INSTANCE 错误。

做到上一部可以编写程序,然后编译,接着运行RTL simulation,这个时候modelsim会自己启动,然后自己编译,接着在work library中会有两个单元,其中一个是testbench生成的,我们仿真的话是用这个。然后添加波形什么的就可以仿真了。

运行时序仿真的话单击quartus上的gate-level simulation按钮就可以了。

接着最关键的问题来了,如果我们修改了VHDL程序或者testbench,怎么在modelsim中更新,我在网上找了很多教程,发现只做到上一步就结束了,在modelsim中更新的话只有关掉modelsim,在quartus中重新进行RTL simulation,显然这样很麻烦,直到我看到这篇文章http://www.cnblogs.com/emouse/archive/2012/07/08/2581223.html,这边文章最后第7步完全可以不用做,我讲一下我的做法。

当运行RTL simulation的时候,modelsim会自己启动,且开始编译,这个是时候实际上它有个命令被输入了,你可以在transcripe中按向上的箭头,会发现有个do ****.do 的命令,你可以在simlation文件夹中找到这个do文件,如果你进行RTL仿真的话,会有****rtl****.do文件,亦然,如果进行gate-level 仿真的话,就有*******gate****.do 文件,请注意区分。当你修改了程序之后要想在modelsim中更新,直接敲这个do *****.do命令就OK了,但是每次敲这个命令会把库文件重新编译,大大浪费了时间,所以你可以找到这个文件,打开,把上面一部分编译库文件的指令注释掉,如下图:

这个时候执行do指令的话,几秒钟就执行完毕了,modelsim中也更新了。

当然modelsim中也可以不用test bench仿真,可以敲force指令生成波形,具体找资料吧。

在test bench中,输入信号都要初始化,否则会显示‘X’任意状态,且不能全都放在一个process中初始化,不然在别的process中对其操作也会呈现‘X’,最好要使用之前初始化一下就可以了.

好像RTL仿真修改了VHLD文件后不需要编译,直接使用do命令就可以更新仿真结果,门级仿真则需要编译一下,再使用do命令才会更新

(转)Quartus II和Modelsim的联合仿真(详细)的更多相关文章

- 【转】Quartus II调用modelsim无缝仿真

Quartus II调用modelsim无缝仿真 ★emouse 思·睿博客文章★ 原创文章转载请注明:http://emouse.cnblogs.com 本篇文章为转载,写的不错,最近在学mode ...

- 通过文件读写方式实现Matlab和Modelsim的联合仿真

虽然Modelsim的功能非常强大,仿真的波形可以以多种形式进行显示,但是当涉及到数字信号处理的算法的仿真验证的时候,则显得有点不足.而进行数字信号处理是Matlab的强项,不但有大量的关于数字信号处 ...

- vivado与modelsim的联合仿真(二)

最近在做Zynq的项目,曾经尝试使用ISE+PlanAhead+XPS+SDK组合和Vivado+SDK来搭建工程,使用中发现前者及其不方便后者有诸多不稳定.近期得闻Xilinx退出Vivado20 ...

- Xilinx ISE如何调用Modelsim进行联合仿真

图: 在对设计的芯片进行测试时,经常要用到FPGA,可是里面的仿真工具却不如Modelsim那么好用,且在规模比较大时,ISE在仿真时,软件经常会报告内存限制的问题,此时一般会切换到Modelsim软 ...

- Quartus II 与modelsim连接不上的问题

在Quartus II 中tools>options>General>EDA Tool Options 设置modelsim 路径 说明:不管是Quartus II 与modelsi ...

- Quartus II调用modelsim无缝仿真

本篇文章为转载,写的不错,最近在学modelsim仿真,网上的教程很乱,把自己认为不错的整理贴出来,后面有机会会写个详细点的. Quartus 中调用modelsim的流程 1. 设定仿真工具 ass ...

- Quartus II 使用 modelsim 仿真

转自:http://www.cnblogs.com/emouse/archive/2012/07/08/2581223.html Quartus 中调用modelsim的流程 1. 设定仿真工具 as ...

- Viavdo&ISE&Quartus II级联Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- Vivado&ISE&Quartus II调用Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

随机推荐

- Oracle数据库的后备和恢复————关于检查点的一些知识

当我们使用一个数据库时,总希望数据库的内容是可靠的.正确的,但由于计算机系统的故障(硬件故障.软件故障.网络故障.进程故障和系统故障)影响数据库系统的操作,影响数据库中数据的正确性,甚至破坏数据库,使 ...

- 对char类型的理解以及对补码的理解分析

今天遇到这样一个小程序,觉得当中有些问题很容易让人忽略的! 这个程序代码如下: 程序的结果为: 我想很多像我一样的小白可能才开始是想不明白为什么最后的结果是255吧!首先,我们得知道 strlen() ...

- codeforces 689 E. Mike and Geometry Problem 组合数学 优先队列

给定一个函数: f([l,r]) = r - l + 1; f(空集) = 0; 即f函数表示闭区间[l,r]的整点的个数 现在给出n个闭区间,和一个数k 从n个区间里面拿出k个区间,然后对这k个区间 ...

- gRPC Java的代码架构

RPC(远程过程调用) 的架构最常见的是"动态代理"方式,事先定义好接口,用一个代理假装实现了这个接口(真正的实现放在服务端),供客户端调用,代理内部将该方法调用封装成一个网络请求 ...

- 数据库连接池dbcp基本配置

DBCP(DataBase connection pool),数据库连接池.是 apache 上的一个 java 连接池项目,也是 tomcat 使用的连接池组件.单独使用dbcp需要2个包: com ...

- 性能测试框架Locust初学笔记

Locust初探 Locust是一款类似于Jmeter开源负载测试工具,所不同的是它是用python实现,并支持python脚本. locust提供web ui界面,能够方便用户实时监控脚本运行状态. ...

- spring 获取 bean

不通过注解或者是配置文件怎么获取spring中定义的bean呢?有几个方法: 1.实现ApplicationContextAware <bean class="com.xxx.Spri ...

- iptables-qos-tcpcopy-tc-tcpdump

QOS: https://www.chiphell.com/thread-427876-1-1.html iptables指南: http://man.chinaunix.net/network/ip ...

- PIC32MZ tutorial -- Blinky LED

Today I finish the "Blinky LED" application on PIC32MZ starter kit. This application let L ...

- Egret 压缩与解压(jszip)

一 jszip是什么 二 为什么要用jszip 三 如果使用zip 一 jszip是什么 jszip 是一个 JavaScript 库,可直接在浏览器上创建 zip 压缩档. 二 为什么要用jszip ...