Verilog基础入门——Vivado流水灯工程(四)(实验报告)

今日进行了数字逻辑实验,完成了一个最简单的FPGA设计,即流水灯设计。

此处记录我们的指导文件以及实验报告,同时记录遇到的问题及解决方法。

一、vivado工程源文件编写

counter.v文件

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/10/08 12:01:18

// Design Name:

// Module Name: counter

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module counter(

input clk,

input rst,

output clk_bps

);

reg[13:0]cnt_first,cnt_second;

always@(posedge clk or posedge rst)

if(rst)

cnt_first<=14'd0;

else if (cnt_first == 14'd10000)

cnt_first<=14'd0;

else cnt_first <=cnt_first + 1'b1;

always@(posedge clk or posedge rst)

if(rst)

cnt_second <= 14'd0;

else if (cnt_second == 14'd10000)

cnt_second<=14'd0;

else if (cnt_first == 14'd10000)

cnt_second <= cnt_second + 1'b1;

assign clk_bps = cnt_second == 14'd10000 ? 1'b1 : 1'b0;

endmodule

flash_led_ctl.v

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// module flash_led_ctl(

input clk,

input rst,

input dir,

input clk_bps,

output reg[15:0]led

);

always @( posedge clk or posedge rst )

if( rst )

led <= 16'h8000;

else

case( dir )

1'b0: //从左向右

if( clk_bps )

if( led != 16'd1 )

led <= led >> 1'b1;

else

led <= 16'h8000;

1'b1: //从右向左

if( clk_bps )

if( led != 16'h8000 )

led <= led << 1'b1;

else

led <= 16'd1;

endcase

endmodule

flash_top_led.v

`timescale 1ns / 1ps module flash_led_top(

input clk,

input rst_n,

input sw0,

output [15:0]led

);

wire clk_bps;

wire rst;

assign rst = ~rst_n; counter counter(

.clk( clk ),

.rst( rst ),

.clk_bps( clk_bps )

);

flash_led_ctl flash_led_ctl(

.clk( clk ),

.rst( rst ),

.dir( sw0 ),

.clk_bps( clk_bps ),

.led( led )

);

endmodule

flash_top_led_tb.v

module flash_led_top_tb;

reg clk,rst,sw0;

wire [15:0] led;

initial begin

clk = 1'b0;

rst = 1'b1;

sw0 = 1'b0;

#10 rst = 1'b0;

#10 rst = 1'b1;

#1000000000 //6ms后改变位移方向

#1000000000

#1000000000

#1000000000

#1000000000

#1000000000

sw0 = 1'b1;

end

always #5 clk <= ~clk;

flash_led_top flash_led_top(

.clk( clk ),

.rst_n( rst ),

.sw0( sw0 ),

.led( led )

);

endmodule

二、工程流程设计

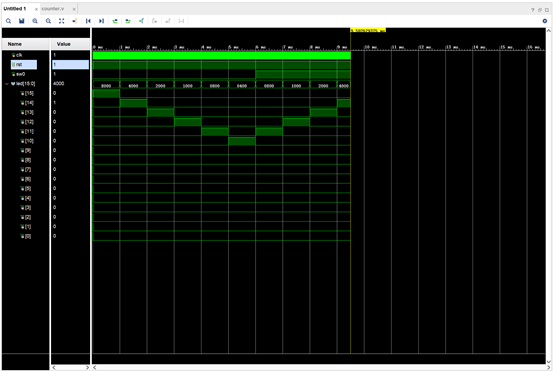

给出流水灯仿真结果截图,对波形进行简要解释:

1、 初始条件下,流水灯从led[15]开始向右移动

2、 6ms后移动至led10亮,改变位移方向向左移动。

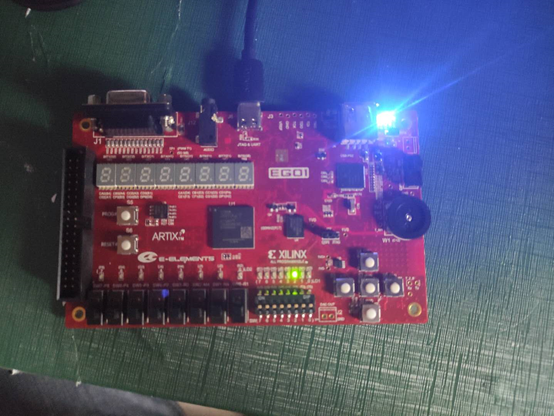

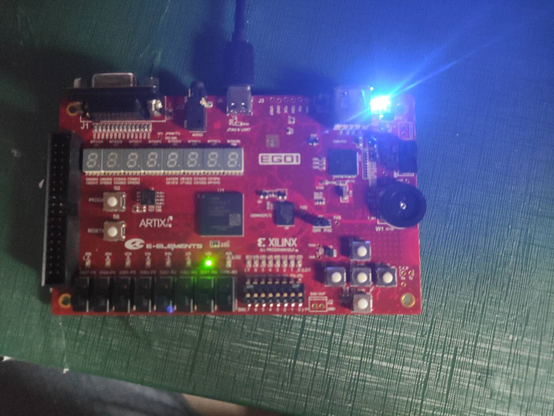

给出板子运行结果照片,以及你的操作过程:

灯向左移动

按下sw0后反向

counter模块的作用是什么?

计时模块

三、实验总结

遇到的问题

1、仿真时波形与预期不相同,排查结果后发现是”Set as top”设置错误。

【在编写源文件的过程中,应该注意到flash_led_top.v文件是应该放到最上方的】

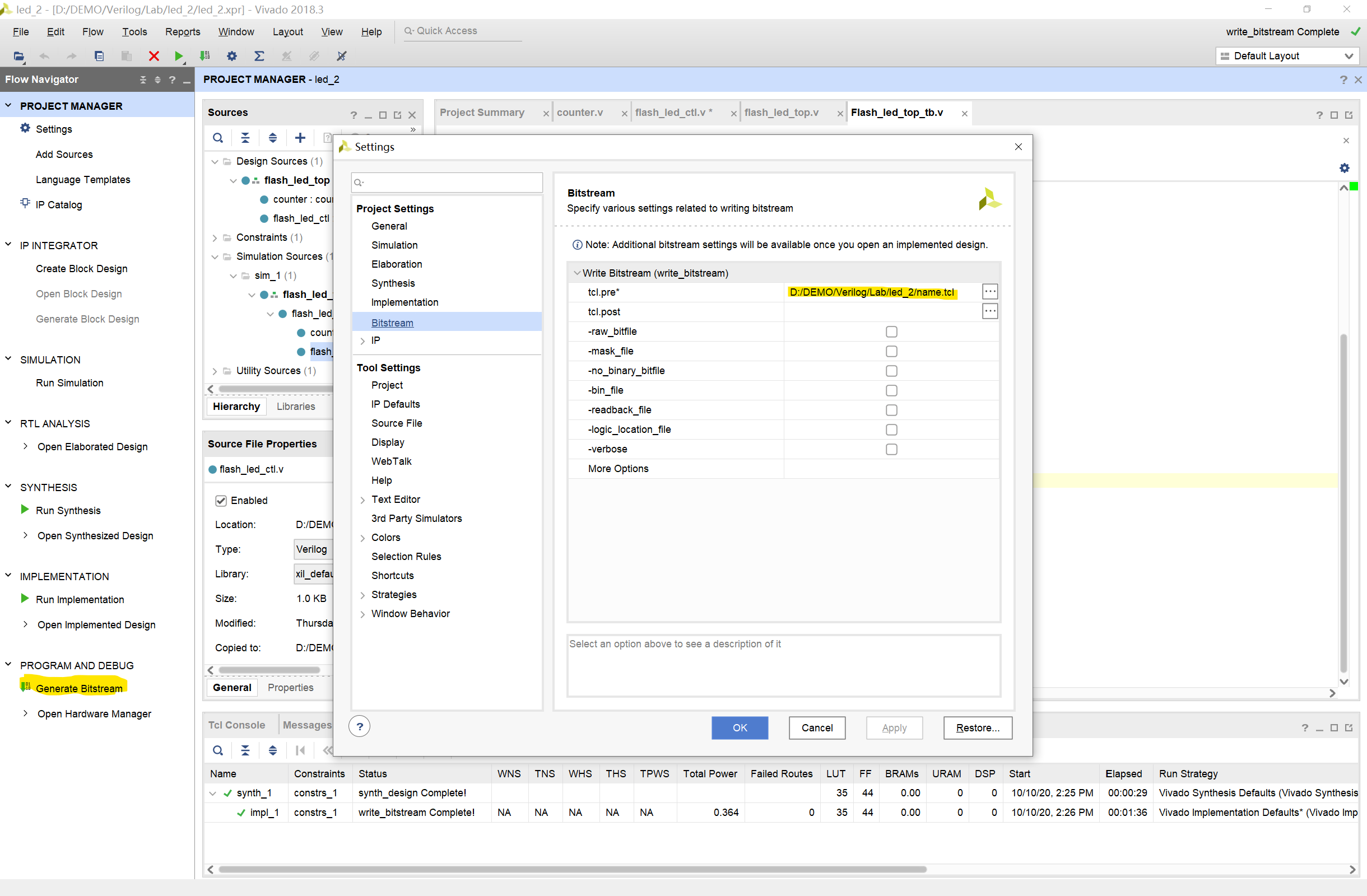

2、无法生成bit流文件,参照csdn上的博客,添加tcl文件代码如下

【set_property

SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property

SEVERITY {Warning} [get_drc_checks UCIO-1]

set_property

SEVERITY {Warning} [get_drc_checks RTSTAT-1]】

右键click左下方的generate bitstream——添加tcl文件。

体会

多查,网上有很多的解决方案,不断排查问题才能得到正确解决方案。

Verilog基础入门——Vivado流水灯工程(四)(实验报告)的更多相关文章

- Verilog基础入门——Vivado工程创建(三)

Verilog基础入门--Vivado工程创建(三) Vivado是Verilog语言的一个集成环境,目前使用的版本为英文版,简单介绍一下在Vivado中创建一个工程并写入源文件 [配置] win10 ...

- 实验四实验报告————Android基础开发

实验四实验报告----Android基础开发 任务一 关于R类 关于apk文件 实验成果 任务二 活动声明周期 实验成果 任务三 关于PendingIntent类 实验成果 任务四 关于布局 实验成果 ...

- 20145120 《Java程序设计》实验四实验报告

20145120 <Java程序设计>实验四实验报告 实验名称:Android开发基础 实验目的与要求: 用SDK成功编译出HelloWorld 实验内容.步骤 PSP 步骤 耗时 百分比 ...

- 20145328 《Java程序设计》实验四实验报告

20145328 <Java程序设计>实验四实验报告 实验名称 Andoid开发基础 实验内容 基于Android Studio开发简单的Android应用并部署测试; 了解Android ...

- 20145227 《Java程序设计》实验四实验报告

20145227 <Java程序设计>实验四实验报告 实验内容 安装Andriod Studio并配置软件 使用Andriod Studio软件实现Hello World的小程序 实验步骤 ...

- 20145315 《Java程序设计》实验四实验报告

20145315 <Java程序设计>实验四实验报告 第一步 安装Android Studio 按教程安装即可,安装过程中需要配置JAVA_HOME环境变量为jdk安装目录. 第二步 在I ...

- # 20155337 《Android程序设计》实验四实验报告

20155337 <Android程序设计>实验四实验报告 实验一 实验内容 Android Stuidio的安装测试: 参考<Java和Android开发学习指南(第二版)(EPU ...

- 20145314郑凯杰 《Java程序设计》实验四 实验报告

20145314郑凯杰 <Java程序设计>实验四 实验报告 实验要求 完成实验.撰写实验报告,实验报告以博客方式发表在博客园,注意实验报告重点是运行结果,遇到的问题(工具查找,安装,使用 ...

- 《Java程序设计》实验四 实验报告

实验四 Android开发基础 实验内容 XP基础 XP核心实践 相关工具 实验要求 1.没有Linux基础的同学建议先学习<Linux基础入门(新版)><Vim编辑器> 课程 ...

随机推荐

- jenkins打包前端项目报 error: index-pack died of signal 15 问题解决

jenkins打包前端项目报 error: index-pack died of signal 15 问题解决 前几天用jenkins打包一个前端项目的时候出现了 error: index-pack ...

- Unit1:Android

unit1 1.安卓版本 最新数据访问维基百科 2008年,android1.0 2011年,android3.0,平板失败 同年10月,android4.0,无差别使用 2014年,android5 ...

- 第 8 篇:内容支持 Markdown 语法,接口返回包含解析后的 HTML

作者:HelloGitHub-追梦人物 在 Django博客教程(第二版) 中,我们给博客内容增加了 Markdown 的支持,博客详情接口应该返回解析后的 HTML 内容. 来回顾一下 Post 模 ...

- 如何成为一位优秀的ScrumMaster

嗨,大家好,我是叶子 背景介绍 目标:为了能更好的适应快速变化的需求和不确定的未来. 部门包含岗位:部门负责人.项目经理.产品经理.开发团队(开发人员.测试人员) 那么这种情况下,我们想转型Scrum ...

- Node.js 从零开发 web server博客项目[koa2重构博客项目]

web server博客项目 Node.js 从零开发 web server博客项目[项目介绍] Node.js 从零开发 web server博客项目[接口] Node.js 从零开发 web se ...

- FastDFS不同步怎么破

一.背景说明 FastDFS是一款开源的分布式文件系统,具体介绍就不说了,有兴趣的可以自行百度下. 以下是官方的架构图: 一次完整的写交互过程如下: 1.Client向Tracker查询可用的Stor ...

- Oracle学习(十六)Oracle安装

为了本地创建数据库自己玩耍,还是下个Oracle的客户端吧... 一.下载地址 注意,要用Oracle的帐号进行登录后才能下载 http://download.oracle.com/otn/nt/or ...

- 搜索引擎学习(三)Lucene查询索引

一.查询理论 创建查询:构建一个包含了文档域和语汇单元的文档查询对象.(例:fileName:lucene) 查询过程:根据查询对象的条件,在索引中找出相应的term,然后根据term找到对应的文档i ...

- BurpSuite抓取本地包方法

本文重点在介绍抓本地包, 而非介绍抓包步骤 Burpsuite配置 默认配置即可 Chrome 浏览器配置 Falcon Proxy扩展程序配置浏览器代理. 需要抓包的网页是个本地搭建的网址, 一般会 ...

- hystrix 源码分析以及属性的配置

一.feign与hystix结合 1.1测试环境搭建 架构如图: 非常简单,就是Order服务通过feign调用product服务的一个获取商品信息的一个接口: package com.yang.xi ...