ahb时序解析

ahb 总线架构

AHB(Advanced High Performance Bus)总线规范是AMBA(Advanced Microcontroller Bus Architecture) V2.0总线规范的一部分,AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。现在已经有AHB V5.0。

AHB总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线主机、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统,不仅如此,还可以通过AHB-APB桥来连接APB总线系统。AHB可以成为一个完整独立的SOC芯片的骨架。

AHB特点:

分块处理

单周期总线主机移交

单时钟沿操作

无需三态门的实现方式

更宽的数据总线架构(64位或者128位)

流水线操作

可支持多个总线主设备(最多16个)

ahb 总线组成

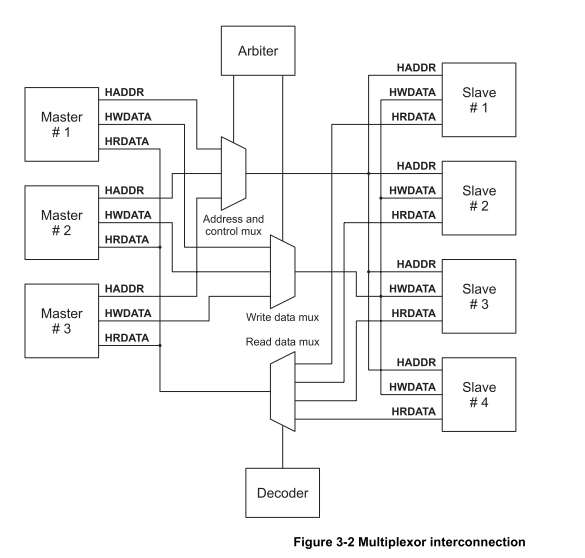

AHB总线由AHB总线主机(Master)、AHB总线从机(Slave)和Infrastructure构成。Infrastructure由仲裁器、数据多路选择器、地址控制多路选择器、译码器构成。

AMBA AHB 总线协议设计使用一个中央多路选择器互联方案。该方案中,所有总线主机设备输出地址和控制信号来指示它们想执行的传输,同时仲裁器决定哪一个主机能够将它

的地址和控制信号连通到所有的从机。当然也需要一个译码器来控制读数据和响应多路信号选择器,多路信号选择器选中来自传输中所包含从机的适当信号。

AHB 主机: 总线主机能够通过提供地址和控制信息发起读写操作。任何时候只允许一个总线主机处于有效状态并能使用总线。

AHB 从机: 总线从机在给定的地址空间范围内响应读写操作。总线从机将成功、失败或者等待数据传输的信号返回给有效的主机。

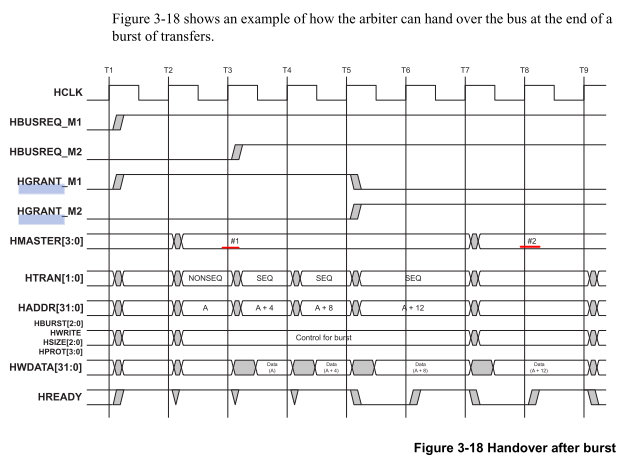

AHB 仲裁器: 总线仲裁器确保每次只有一个总线主机被允许发起数据传输。即使仲裁协议已经固定,任何一种仲裁算法,比如最高优先级或者公平访问都能够根据应用要求而得到执行。AHB 必须只包含一个仲裁器,尽管在单总线主机系统中这显得并不重要。

AHB 译码器: AHB 译码器用来对每次传输进行地址译码并且在传输中包含一个从机选择信号。

所有 AHB 执行都必须仅要求有一个中央译码器。

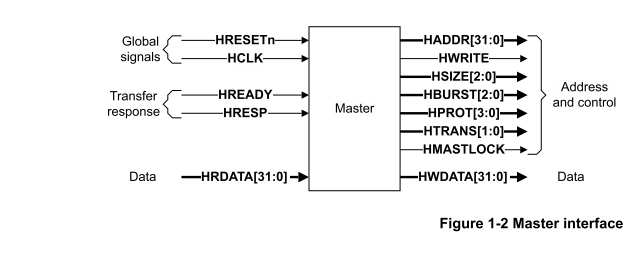

master interface

slave interface

master侧时序和信号分析:

- hburst[2:0] :用于控制突发类型(模式)

- hbusreq

master向bus仲裁器申请bus总线使用权;最多可以有16个master。

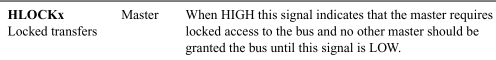

hlock

当该信号为高时,表示master请求锁定对总线的访问,在HLOCK为LOW之前,其他master不允许获得总线。

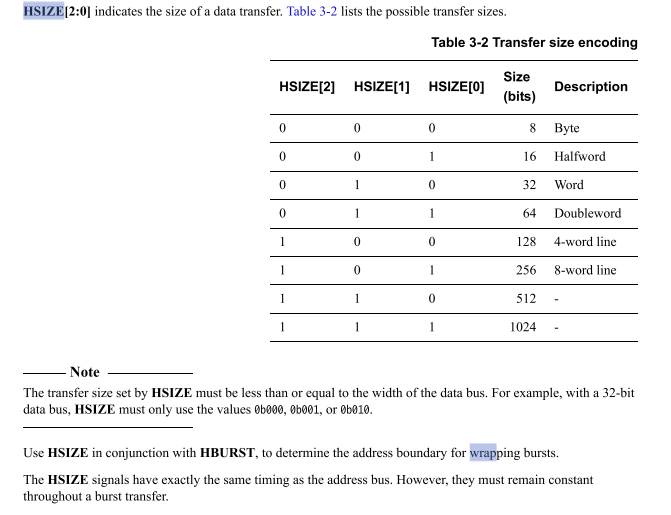

- HSIZE[2:0]

HTRANS[1:0]

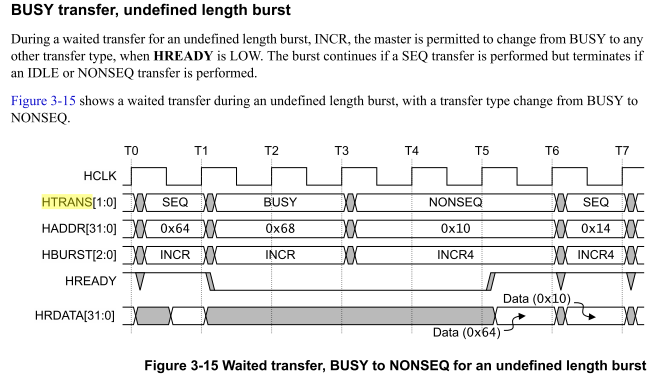

在wait Undefine Length busrt(INCR)的传输期间,当HREADY为低时,允许主机从BUSY改变为任何其它传输类型。如果执行SEQ传输,则burst继续,如果执行IDLE或NONSEQ传输,则burst终止。在T3~T5,HREADY为LOW时,HTRANS需保持。

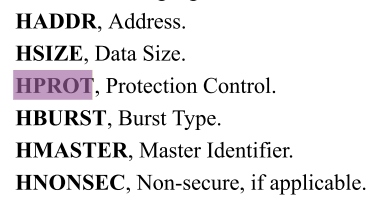

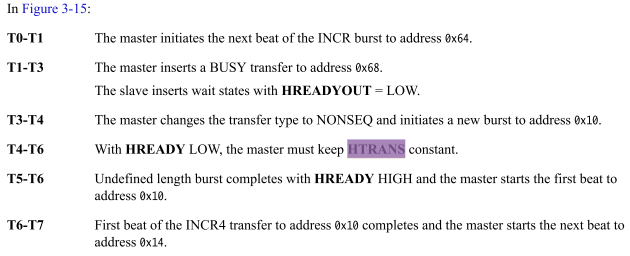

- HPROT

HPROT[6:4]是AHB5新增的,用来表示extended memory types,如果Extended_Memory_Types是True,HPROT[6:4]有效。 Issue A of this specification defined a 4-bit HPROT signal, which is described in this section.

Issue B of this specification adds extended memory types and this is described in more detail in Memory types on page 3-45.

-------------Note---------------

The name of HPROT[3] is changed between Issue A and Issue B of this specification, but the definition remains the same. In Issue A HPROT[3] was designated Cacheable, in Issue B it is designated Modifiable. ------------------------------------------------------------------------------------------------------------------------------- The protection control signals, HPROT[3:0], provide additional information about a bus access and are primarily intended for use by any module that implements some level of protection.

slave一般不使用HPROT信号。(Bufferable和Cacheable的区别详见相应博客随笔)

AHB5 defines the Extended_Memory_Types property. This property defines whether an interface supports the extended memory types described in this section. If this property is not defined, then the interface does not support the extended memory types.

This issue of the specification adds additional HPROT signaling and provides a more detailed list of requirements for each of the memory types. 该规范的这一期增加了额外的HPROT信令,并提供了每种存储器类型的更详细的要求列表。

- HGRANT:

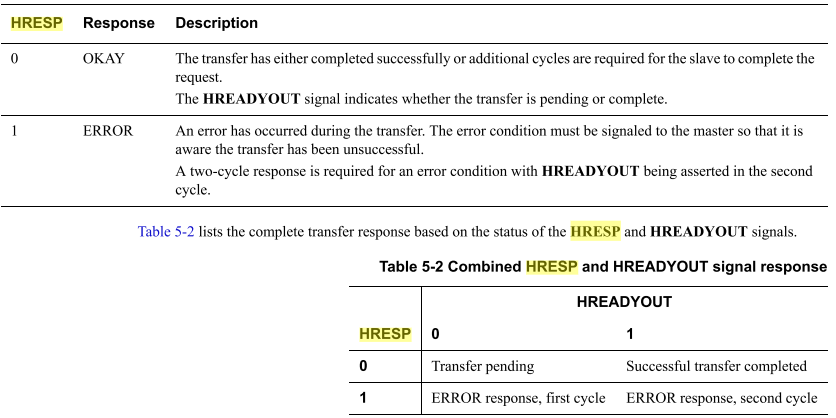

HRESP[1:0]

在AHB 5.0中描述如下:

在AHB 2.0中描述如下:

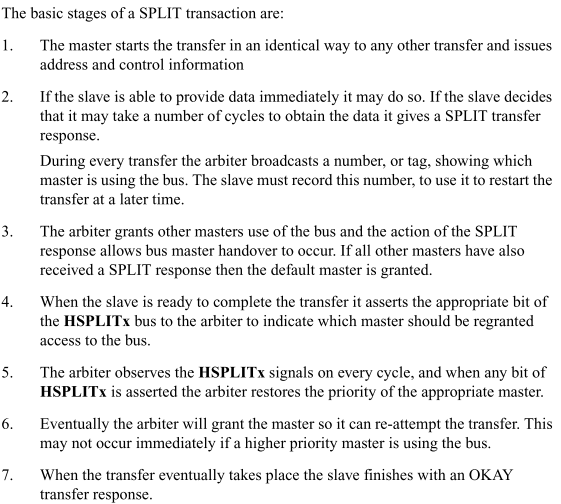

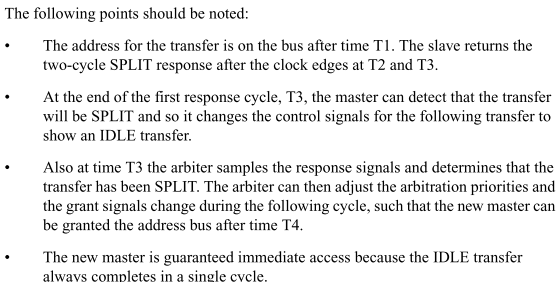

除了OKAY之外,其他都需要两拍;RETRY和SPLIT的发生时,当前master都会释放总线,区别如下:

- The difference between SPLIT and RETRY is the way the arbiter allocates the bus after a SPLIT or a RETRY has occurred:

• For RETRY the arbiter will continue to use the normal priority scheme and therefore only masters having a higher priority will gain access to the bus. 对于RETRY,只有较高优先级的master可以获得总线。

• For a SPLIT transfer the arbiter will adjust the priority scheme so that any other master requesting the bus will get access, even if it is a lower priority. In order for a SPLIT transfer to complete the arbiter must be informed when the slave has the data available. 对于SPLIT,仲裁器会调整优先级,让其他所有master都可以获得总线,即使是优先级低的master也可以获得总线,当slave有足够的空间完成split传输时,通知arbiter,arbiter恢复master的优先级,等待高优先级传输完成之后,传输该master的split传输。 - The SPLIT and RETRY responses provide a mechanism for slaves to release the bus when they are unable to supply data for a transfer immediately. Both mechanisms allow the transfer to finish on the bus and therefore allow a higher-priority master to get access to the bus

- The difference between SPLIT and RETRY is the way the arbiter allocates the bus after a SPLIT or a RETRY has occurred:

疑问:当slave返回split之后,arbiter仍然按照优先级优先处理其他优先级mater的业务,还是处理完上一个master的业务之后,优先初理split?----恢复该master的优先级,按照优先级正常传输。

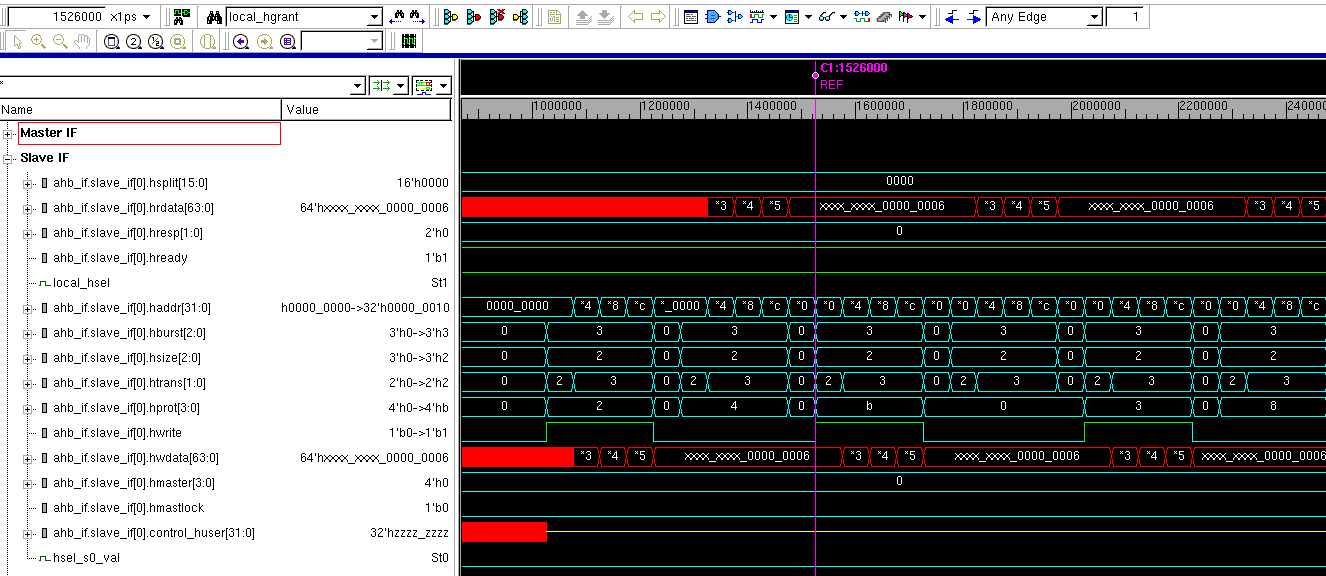

slave侧时序和信号分析:

- HSPLIT[15:0]:当slave认为需要多次初理时,用于分割传输,该信号在slave和arbiter之间使用。

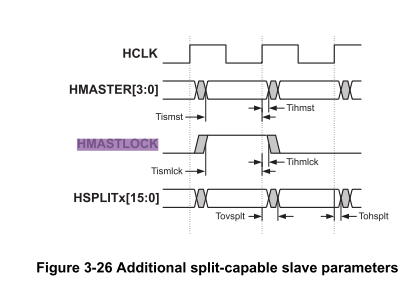

- hmaster[3:0]:用来表示哪个master正在占用总线

- hmastlock:表示当前master正在执行锁定的传输序列,该信号与hmaster具有相同的时序。

参考资料:

ahb时序解析的更多相关文章

- AHB接口转APB

AHB接口转APB 情景 有一个以AHB接口时序设计的IP,现在需将其移至APB总线上,即将使用APB接口时序驱动该IP. 基本思路 将APB的接口信号映射到AHB的接口信号 要点 APB挂接在AHB ...

- ARM40-A5应用——fbset与液晶屏参数的适配【转】

转自:https://blog.csdn.net/vonchn/article/details/80784579 ARM40-A5应用——fbset与液晶屏参数的适配 2018.6.18 版权声明:本 ...

- 海思hi35xx 开发学习(3):视频输入

视频输入(VI)模块实现的功能:通过 MIPI Rx(含 MIPI 接口.LVDS 接口和 HISPI 接口),SLVS-EC,BT.1120,BT.656,BT.601,DC 等接口接收视频数据.V ...

- AHB2reg接口转换

assign mcu_xxx_addr = (rd_after_wr_reg || reg_valid_write_trans) ? haddr_reg[ADDR_WIDTH+:] : haddr[A ...

- 3. 海思Hi3519A MPP从入门到精通(三 视频输入)

视频输入(VI)模块实现的功能:通过 MIPI Rx(含 MIPI 接口.LVDS 接口和 HISPI 接 口),SLVS-EC,BT.1120,BT.656,BT.601,DC 等接口接收视频数据. ...

- Hi3559AV100的VI细节处理说明

因为项目后期涉及到MPP平台下的VI接口,现把有关视频输入VI模块的实现细节总结,也方便大家进一步了解. 1.整体概述 视频输入(VI)模块实现的功能:通过 MIPI Rx(含 MIPI 接口.LVD ...

- 时序数据库连载系列: 时序数据库一哥InfluxDB之存储机制解析

InfluxDB 的存储机制解析 本文介绍了InfluxDB对于时序数据的存储/索引的设计.由于InfluxDB的集群版已在0.12版就不再开源,因此如无特殊说明,本文的介绍对象都是指 InfluxD ...

- 时序数据库 Apache-IoTDB 源码解析之文件数据块(四)

上一章聊到行式存储.列式存储的基本概念,并介绍了 TsFile 是如何存储数据以及基本概念.详情请见: 时序数据库 Apache-IoTDB 源码解析之文件格式简介(三) 打一波广告,欢迎大家访问Io ...

- 时序数据库 Apache-IoTDB 源码解析之文件格式简介(三)

上一章聊到在车联网或物联网中对数据库的需求,以及 IoTDB 的整体架构,详情请见: 时序数据库 Apache-IoTDB 源码解析之系统架构(二) 打一波广告,欢迎大家访问IoTDB 仓库,求一波 ...

随机推荐

- SpringBoot系列——附件管理:整合业务表单实现上传、回显、下载

前言 日常开发中,大多数项目都会涉及到附件上传.回显.下载等功能,本文记录封装通用附件管理模块,并与业务模块进行整合实现上传.回显.下载 我们之前已经对文件上传下载有过记录,传送门:基于"f ...

- 在PHP中操作临时文件

关于文件相关的操作,想必大家已经非常了解了,在将来我们刷到手册中相关的文件操作函数时也会进行详细的讲解.今天,我们先来了解一下在 PHP 中关于临时文件相关的一些内容. 获取 PHP 的默认临时创建文 ...

- 写SQL的套路

定义问题 转化问题 如要解决的问题是:查出每门课程成绩都大于80分学生的姓名,可以转化为:只要学生最小分数的课程大于80分,就是所有课程成绩都大于80分. 查询同名同姓学生名单并统计同名人数--> ...

- P5666-[CSP-S2019]树的重心【树状数组】

正题 题目链接:https://www.luogu.com.cn/problem/P5666 题目大意 给出\(n\)个点的一棵树,对于每条边割掉后两棵树重心编号和. \(1\leq T\leq 5, ...

- AT4119-[ARC096C]Everything on It【斯特林数,容斥】

正题 题目链接:https://www.luogu.com.cn/problem/AT4119 题目大意 一个集合\(S=\{k\in[1,n]\cup N\}\),它的所有子集作为元素组成的集合中要 ...

- Python代码阅读(第8篇):列表元素逻辑判断

Python 代码阅读合集介绍:为什么不推荐Python初学者直接看项目源码 本篇阅读的三份代码的功能分别是判断列表中的元素是否都符合给定的条件:判断列表中是否存在符合给定的条件的元素:以及判断列表中 ...

- .Net Core 实现 自定义Http的Range输出实现断点续传或者分段下载

一.Http的Range请求头,结合相应头Accept-Ranges.Content-Range 可以实现如下功能: 1.断点续传.用于下载文件被中断后,继续下载. 2.大文件指定区块下载,如视频.音 ...

- MySQL强人“锁”难《死磕MySQL系列 三》

系列文章 一.原来一条select语句在MySQL是这样执行的<死磕MySQL系列 一> 二.一生挚友redo log.binlog<死磕MySQL系列 二> 前言 最近数据库 ...

- .NET 开发一个服务器 应用管理工具

一:背景 1.Anno.Deploy Anno.Deploy可以和 Anno集成使用,用于部署新的服务.启动服务.停止服务.清理服务.也可以单独使用,用于守护程序. 使用方法 1.和Anno集成使用 ...

- python 注册 gin consul

import requests headers = { "contentType": "application/json" } def register(nam ...