verilog中always块延时总结

在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论。

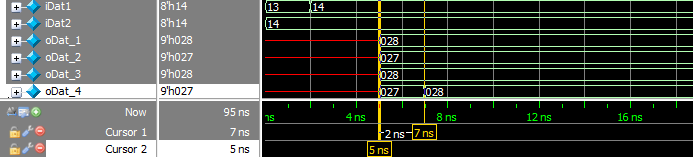

观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 。

@2时刻,输入数据分别是0x14,,0x14 。

四个输出应该是什么样子呢?

always @ (iDat1 or iDat2)

# oDat_1 = iDat1 + iDat2; always @ (iDat1 or iDat2)

oDat_2 = # iDat1 + iDat2; always @ (iDat1 or iDat2)

# oDat_3 <= iDat1 + iDat2; always @(iDat1 or iDat2)

oDat_4 <= # iDat1 + iDat2;

直接上图吧

作为阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_1延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_2 是先取了旧值,再延时赋值,中间如果等号右边有变化,被阻塞了。所以oData_2是旧值 。

always @ (iDat1 or iDat2)

# oDat_1 = iDat1 + iDat2; always @ (iDat1 or iDat2)

oDat_2 = # iDat1 + iDat2;

作为非阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_3延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_4 是先取了旧值,再延时赋值,中间如果等号右边有变化,没有被阻塞,新建event,所以oData_2是旧值之后再更新为新值 。

always @ (iDat1 or iDat2)

# oDat_3 <= iDat1 + iDat2; always @(iDat1 or iDat2)

oDat_4 <= # iDat1 + iDat2;

所以,这以后写TB的时候要慎重啊。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

verilog中always块延时总结的更多相关文章

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- 【转载】Verilog中的parameter

1. 概述 在Verilog中我们常常会遇到要将一个常量(算法中的某个参数)赋给很多个变量的情况,如: x = 10;y = 10;z = 10;如果此时10要改为9,就需要在代码中修改3个地方,非常 ...

- verilog中timescale

1. `timescale `timescale是Verilog中的预编译指令,指定位于它后边的module的时间单位和时间精度,直到遇到新的`timescale指令或者`resetall指令.它的语 ...

- Verilog中的$display和$write任务

$display(p1,p2, …,pn); $write(p1,p2, …,pn); 这两个函数和系统任务的作用都是用来输出信息,即将参数p2到pn按参数p1给定的格式输出.参数p1通常称为:“格式 ...

- Verilog中的阻塞与非阻塞

这篇文档值得阅读 按说阻塞与非阻塞是Verilog中最基本的东西,也是老生常谈.但是最近看到很多程序里用到阻塞语句竟然不是很明白,说到底是从来没有自己仔细分析过.当然一般情况程序中也是推荐用非阻塞的. ...

- 在verilog中调用VHDL模块

习惯了自己发现一些小问题,既然发现了,就记下来吧,不然又要忘了,这是多么悲痛的领悟. 今天在用vivado进行块设计时所生成的顶层模块居然是用VHDL语言描述的,这时郁闷了,表示只看过VHDL语法但没 ...

- 总结Verilog中always语句的使用

always语句包括的所有行为语句构成了一个always语句块.该always语句块从仿真0时刻开始执行其中的行为语句:最后一条执行完成后,再开始执行其中的第一条语句,如此往复循环,直到整个仿真结束. ...

- verilog中的timescale

`timescale是Verilog HDL 中的一种时间尺度预编译指令,它用来定义模块的仿真 时的时间单位和时间精度.格式如下: `timescale 仿真时间单位/时间精度 注意:,不能为其它的 ...

随机推荐

- 君子性非异也,善假于物也 - Threejs 引入TrackballControls 查看场景

君子性非异也,善假于物也 - Threejs 引入TrackballControls 查看场景 太阳火神的漂亮人生 (http://blog.csdn.net/opengl_es) 本文遵循" ...

- sql server dateadd()

定义和用法 DATEADD() 函数在日期中添加或减去指定的时间间隔. 语法 DATEADD(datepart,number,date) date 参数是合法的日期表达式.number 是您希望添加的 ...

- JavaScript之ClassName属性学习

在前面的style属性学习中,知道了通过style属性可以控制元素的样式,从而实现了行为层通过DOM的style属性去干预变现层显示的目地,但是这种就是不好的,而且为了实现通过DOM脚本设置的样式,你 ...

- Samba在CentOS下的图形化界面的安装

第一步:构建yum仓库(在此用的是北交大的yum仓库) 打开目录/etc/yum.repos.d下的CentOS-Base.repo文件,此处是我自己建的yum仓库,修改里面的链接地址为北交大的镜像的 ...

- iOS 设置UIDatePiicer为24小时制

直接上代码: NSDateFormatter* dateFormatter = [[NSDateFormatter alloc] init]; [dateFormatter setDateFormat ...

- Filemanager 的使用

filemanager的使用包括: 1.创建文件夹 2.删除文件夹 3.写入文件 4.复制文件 5.移动文件 6.删除文件 一.创建文件夹 首先宏的定义一个字符串作为地址的来获取当前的docum ...

- 浅谈Spring(二)

一.AOP编程(面向切面编程) AOP的本质是代理. 1.静态代理设计模式 概念:通过代理类为原始类增加额外功能. 代理类 = 原始类 + 额外功能 +实现原始类的相同接口. 优点:避免原始类因为额外 ...

- 理解ROS的节点(NODE)

经过前面的学习,我们已经知道了如何构建一个ROS的包,这篇博客将介绍ROS中的节点的概念. 在继续之前,请按ctrl+alt+t打开一个终端,在里面输入: sudo apt-get install r ...

- C学习之指针强化

char *p = (char *)malloc(100); malloc是用于分配内存的函数,它的参数为int型,表示分配多少个字节长度,其返回类型为void*,在这里用char*就是强制转化,指定 ...

- 新视野OJ 2705 [SDOI2012]Longge的问题 (数论)

传送门:http://www.lydsy.com/JudgeOnline/problem.php?id=2705 题解:求 sigma(gcd(i,n), 1<=i<=n<2^32) ...