移位寄存器及verilog代码

一、移位器(shifter)

作用:移位器和循环移位器用于移动位并完成2的幂的乘法或除法。

分类:

逻辑移位器——左移(LSL)或右移(LSR),以0填充空位。11001 LSR 2 =00110; 11001 LSL 2 = 00100;(veilog 操作符号>> or <<)

算数移位器——算数左移(ASL)与逻辑左移相同,但算数右移(ASR)时会把原来数据的最高有效位填充在数据的最高有效位上,对于有符号数的乘法或除法有用。11001 ASR 2 = 11110; 11001 ASL 2 =00100;(verilog操作符号>>> or <<<)

循环移位器——循环移动数字,从一端移走的位重新填充到另一端的空位。11001 ROR 2 = 01110;11001 ROL 2 = 00111。

二、移位寄存器(shift register)

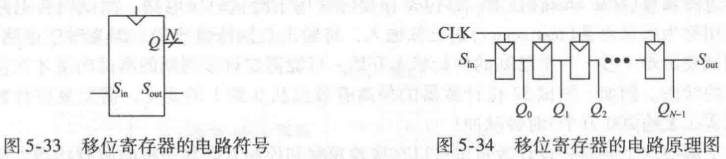

输入:包括时钟clk,串行输入Sin,串行输出Sout和N位并行输出QN-1:0。

工作原理:在时钟的边沿,从Sin移入一个新的位,所有后续内容都向前移动,最后一位在Sout中。

作用:可以作为串行到并行(serial-to-parrallel)的转换器,输入由Sin提供,经N个周期后,前面的N位输入可以在Q中进行并行访问。

组成:如图5-34所示,N位的移位寄存器由N个触发器串联而成,有些移位寄存器还有触发器的复位信号。

相关电路:包含并行到串行转换器(parrallel-to-serial)的移位寄存器,并行加载N位,然后依次移出一位。

工作原理:相比于移位寄存器增加了并行输入DN-1:0和控制信号Load。当Load信号有效时,触发器从D中并行加载数据;否则正常移位。

通用移位寄存器

作用:后续补全

//通用移位寄存器

module Universal_Shift_Reg#(parameter word_size = )(

output reg[word_size-:] Data_out,

output MSB_out, LSB_out,

input [word_size-:] Data_in,

input MSB_in, LSB_in,

input s0, s1, clk, rst

);

assign MSB_out = Data_out[word_size-];

assign LSB_out = Data_out[]; always @(posedge clk)

begin

if(rst=='b1) Data_out <= 0;

else

case({s1, s0})

: Data_out <= Data_out; //maintain

: Data_out <= {MSB_in, Data_out[word_size-:]}; //MSB shift

: Data_out <= {Data_out[word_size-:], LSB_in}; //LSB shift

: Data_out <= Data_in; //parallel input

endcase end

endmodule

移位寄存器

作用

module shift_reg#(parameter word_size = )(

output reg_out,

input clk, rst,reg_in

);

reg [word_size-:] reg_data;

assign reg_out = reg_data[];

always @(posedge clk, negedge rst)

if(!rst) reg_data <= {word_size{'b0}}; //nonblock assignment

else reg_data <= {reg_in, reg_data[word_size-:]};

endmodule

桶形移位寄存器

作用

module barrel_reg #(parameter word_size = )(

output reg [word_size-:] data_out,

input [word_size-:] data_in,

input load, clk, rst

);

always @(posedge clk, posedge rst)

begin

if(rst) data_out <= {word_size{'b0}};

else if(load) data_out <= {data_in[word_size-:], data_in[word_size-]};

end

endmodule

算术移位寄存器

// 移一位和八位的算数寄存器

module top_module(

input clk,

input load,

input ena,

input [:] amount,

input [:] data,

output reg [:] q);

always @(posedge clk)

if(load)

q <= data;

else if(ena)

begin

case(amount)

'b00: q <= {q[62:0], 1'b0};

'b01: q <= {q[55:0], 8'b0};

'b10: q <= {q[63], q[63:1]};

'b11: q <= {{8{q[63]}}, q[63:8]};

endcase

end

else

q <= q; endmodule

扫描链(scan chain)

作用:通过扫描链技术,移位寄存器经常用于测试时序电路。

原因:由于时序电路中存在状态,测试相对困难。从一个已知的初始装填开始,可能需要许多周期的测试向量才能使电路进入期望状态。为解决这一问题,希望可以通过增加测试模式来实现直接观察和控制有限状态机的所有状态。。然而由于系统中触发器太多以至于无法为每个触发器分配一个管脚进行读写。但是,系统中所有触发器都连接在扫描链的以为寄存器中。

测试模式:允许自由地向所有触发器的内容读出或者加载所需要的值。在测试模式中,扫描链通过Sin和Sout串行地移出内容或写入新的内容。

移位寄存器及verilog代码的更多相关文章

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- HD,3G视频数据中行号的插入方法---Verilog代码实现

HD,3G视频数据中行号的插入方法---Verilog代码实现 行号的生成: `timescale 1ns / 1ps //////////////////////////////////////// ...

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- 串口发送端verilog代码分析

串口发送端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- 总线读写---verilog代码

总线读写---verilog代码 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- FIFO 的控制逻辑---verilog代码

FIFO 的控制逻辑---verilog代码 //fifo的例化 wire fifo_full; wire fifo_empty; : ] fifo_dout; :]rd_data_count; :] ...

- 信号滤波模块verilog代码---UNLOCK,LOCK状态机方式

信号滤波模块verilog代码 `timescale 1ns / 1ps /////////////////////////////////////////////////////////////// ...

- verilog代码 想法验证---与寄存器输出有关

verilog代码 想法验证---与寄存器输出有关 1. module test_mind( input wire clk, input wire reset, input wire i, outpu ...

随机推荐

- 基于Redis消息的订阅发布应用场景

目录 基于Redis消息的订阅发布应用场景 1.应用背景 2.困境 2.1 锁表风险 2.2 实时性差 2.3 增加编程复杂性 2.4 实时效果 3.解决方案 3.1 前端传值给服务端 3.2 服务端 ...

- echarts 双Y轴图表

直接代码: <!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF ...

- Kali Linux configuration "Ettercap"

Xx_Instroduction Ettercap is a man-in-the-middle attack(MITM) tool,kali take this tool,so,use front ...

- Hyper-V “SP2019SER”无法更改状态。操作失败,错误代码为“32788”。

卸载Hyper-V,然后重装,再重启已有的Hyper-V服务器,报错如下: 尝试启动选定的虚拟机时出错.“SP2019SER”无法更改状态. 原因:卸载后导致虚拟网卡出现问题导致的. 解决办法: 右击 ...

- 【转】#define 定义别名和 typedef 声明类型的区别

下面一段程序的执行结果是: #include <stdio.h>#define CHAR2 char*int main(){ typedef char* CHAR; CHAR ...

- jq实现回车键事件

我们写系统的时候常常因为要点击显得很麻烦,习惯了回车键完成一些东西. 接下来就直接上代码吧.jq实现回车键事件 keyDowm: () => { $("body").keyd ...

- 阿里云ECS服务器部署HADOOP集群(四):Hive本地模式的安装

本篇将在阿里云ECS服务器部署HADOOP集群(一):Hadoop完全分布式集群环境搭建的基础上搭建. 本地模式需要采用MySQL数据库存储数据. 1 环境介绍 一台阿里云ECS服务器:master ...

- (办公)记事本_Linux常用的目录命令

参考尚硅谷的谷粒学院:http://www.gulixueyuan.com/course/300/task/7078/show#(免费看,课程很全面,用手机登录一下就行.) .[root@localh ...

- ResultSet RS_resultxtgg=connDbBean.executeQuery(sqlxtgg);

<%String sqlxtgg="select * from dx where leibie='系统公告'"; ResultSet RS_resultxtgg=connDb ...

- error: [debug/qrc_resource.cpp] Error 1

t在进行debug时,出现这个错误,去资源文件夹,用资源编辑器打开resource.qrc文件,查看是否有标红的资源文件. 如果有红色名称的资源文件,那么就是因为缺少该资源文件,导致的这个错误. 改正 ...