EDA课设-交通灯-Verilog版----FPGA--004

- 分得到析四个状态:

S1: 主干道(绿灯亮) ,支干道(亮红灯);--40S

S1: 主干道 (黄灯亮) ,支干道(亮红灯);--4S

S1: 主干道 (亮红灯),支干道(绿灯亮);--20S

S1: 主干道 (亮红灯),支干道(黄灯亮);--4S

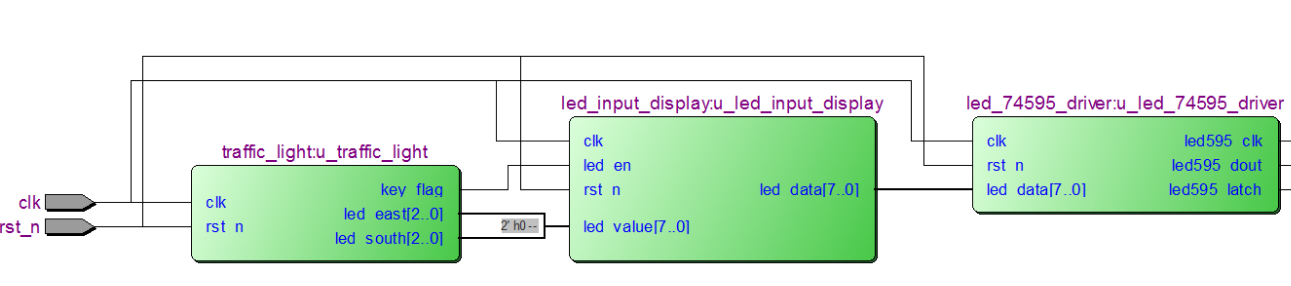

代码:包括四部分:traffic_ligh_top(顶层例化)、traffic_light(交通灯控制部分)、led_input_display(把(交通灯控制部分的)数据打一拍(再送给74595))、led_74595_driver(串转并-进行显示)

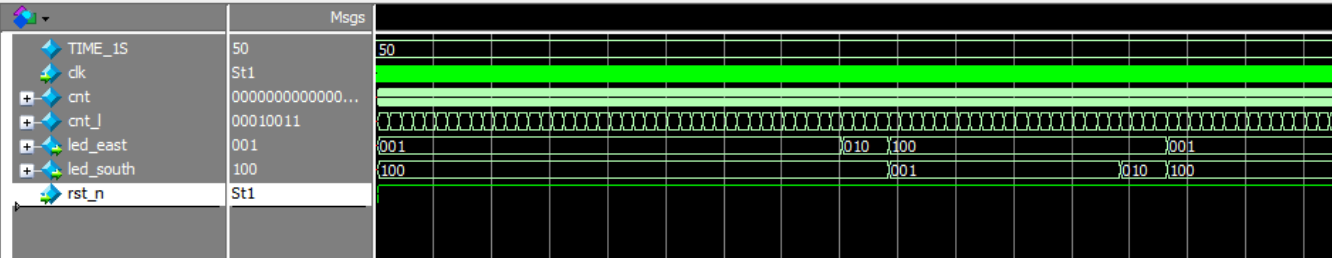

仿真:代码及波形显示

- 代码编写

//---------------------------------------------------------------------------------------

- RTL Viewer

- traffic_ligh_top(顶层例化)

/*-----------------------------------------------------------------------

Author : WHaoL

Technology blogs : http://www.cnblogs.com/luckySuperman/

: http://blog.chinaaet.com/eWorld

Email Address : liangwenhao0603@163.com

Filename : traffic_ligh_top.v

Data : 2016-09-26

Description :

modification history :

Data By Version Change Description

=========================================================================

16/9/26 WHaoL 1.0 Original

=======================================================================*/

`timescale 1ns/1ns

module traffic_ligh_top

(

input clk,

input rst_n, //matrix keyboard interface output led595_clk,

output led595_dout,

output led595_latch

); wire [:] led_east;

wire [:] led_south; wire key_flag;

//-------------------------------------

traffic_light u_traffic_light

(

.clk(clk), //时钟 50MHz

.rst_n(rst_n), //复位 低电平有效 // south north east west

//.e_light(e_light), // 东方向 指示灯

//w_light, //西方向 指示灯 //.s_light(s_light), //南方向 指示灯

//n_light, //北方向 指示灯

.led_east(led_east),

//.led_wast(led_wast), .led_south(led_south),

//.led_nouth(led_nouth)

.key_flag(key_flag)

); //---------------------------------

//led data input with enable signal.

wire [:] led_data;

led_input_display

#(

.LED_WIDTH ()

)

u_led_input_display

(

//global

.clk (clk),

.rst_n (rst_n), //user interface

.led_en (key_flag),

.led_value ({led_east[:],'b00,led_south[2:0]}), //led interface

.led_data (led_data)

); //-------------------------------------------

led_74595_driver u_led_74595_driver

(

//global clock

.clk (clk),//50MHz

.rst_n (rst_n), //user led output

.led_data (led_data),

.led595_clk (led595_clk),

.led595_dout (led595_dout),

.led595_latch (led595_latch)

); endmodule

- traffic_light(交通灯控制部分)

`timescale 1ns/1ns

module traffic_light

(

clk,

rst_n, key_flag, led_east,

//led_wast, led_south

//led_nouth );

parameter TIME_1S = 50_000_000; input clk;

input rst_n; output [:] led_east;

//output [2:0] led_wast;

output [:] led_south;

//output [2:0] led_nouth;

output key_flag; reg [:] led_east;

//reg [2:0] led_wast;

reg [:] led_south;

//reg [2:0] led_nouth; reg key_flag; reg [:] cnt;

reg [:] cnt_l; //---------------------------------------------------------

//led_east

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_east <= 'b001;//G

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_east <= 'b010;//Y

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_east <= 'b100;//R

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_east <= 'b001;//G

else

led_east <= led_east;

end //---------------------------------------------------------

//wast

//always@(posedge clk or negedge rst_n)

//begin

// if(!rst_n)

// led_wast <= 3'b001;

// else if((cnt_l == 39)&&(cnt == TIME_1S-1'b1))

// led_wast <= 3'b010;

// else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1))

// led_wast <= 3'b100;

// else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1))

// led_wast <= 3'b001;

// else

// led_wast <= led_wast;

//end

//---------------------------------------------------------/////////////////////////////////////

//led_south

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_south <= 'b100;//R

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_south <= 'b001;//G

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_south <= 'b010;//Y

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_south <= 'b100;//R

else

led_south <= led_south;

end

//---------------------------------------------------------

//led_nouth

//always@(posedge clk or negedge rst_n)

//begin

// if(!rst_n)

// led_nouth <= 3'b100;//R

// else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1))

// led_nouth <= 3'b001;//G

// else if((cnt_l == 63)&&(cnt == TIME_1S-1'b1))

// led_nouth <= 3'b010;//Y

// else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1))

// led_nouth <= 3'b100;//R

// else

// led_nouth <= led_nouth;

//end

//----------------------------------------------------------

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= ;

else if(cnt==(TIME_1S-'b1))

cnt <= ;

else

cnt <= cnt+'b1;

end always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_l <= ;

else if((cnt==(TIME_1S-'b1))&&(cnt_l==8'd67))

cnt_l <= ;

else if(cnt==(TIME_1S-'b1))

cnt_l <= cnt_l+'b1;

else

cnt_l <= cnt_l;

end //----------------------------------------------------------------------------

//wire key_trigger = ((cnt==TIME_1S-1'b1)&&((cnt_l==8'd39)||(cnt_l==8'd43)||(cnt_l==8'd67)||(cnt_l==8'd63))) ? 1'b1 : 1'b0; wire key_trigger = (cnt==(TIME_1S-'b1)) ? 1'b1 : 'b0;

//---------------------------------

//Lag 1 clock for valid read enable

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

key_flag <= ;

else

key_flag <= key_trigger;

end endmodule

- led_input_display(把(交通灯控制部分的)数据打一拍(送给74595))

`timescale 1ns/1ns

module led_input_display

#(

parameter LED_WIDTH =

)

(

//global clock

input clk,

input rst_n, //user interface

input led_en,

input [LED_WIDTH-:] led_value, //led interface

output reg [LED_WIDTH-:] led_data

); //--------------------------------------

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_data <= 'b001_00_100;

else if(led_en)

led_data <= led_value;

else

led_data <= led_data;

end endmodule

- led_74595_driver(串转并-进行显示)

`timescale 1ns/1ns

module led_74595_driver

(

//global clock

input clk,//50MHz

input rst_n, //user led output

input [:] led_data, output led595_clk,

output led595_dout,

output led595_latch

);

//-----------------------------

//update display when led_data is update

//generate led_data_r and update_flag

reg [:] led_data_r;

reg update_flag;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

led_data_r <= ;

update_flag <= ;

end

else

begin

led_data_r <= led_data;

update_flag <= (led_data_r == led_data)?'b1:1'b0;

end

end

//------------------------------

//74HC595 clk delay for enough setup time

// generate shift_flag and shift_clk

localparam DELAY_CNT = 'd7;

reg shift_state;

reg [:] delay_cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

delay_cnt <= ;

else if(shift_state == 'b1)

delay_cnt <= (delay_cnt < DELAY_CNT) ? (delay_cnt+'b1):3'd0;

else

delay_cnt <= ;

end

wire shift_clk = (delay_cnt > DELAY_CNT/) ? 'b1 : 1'b0;

wire shift_flag = (delay_cnt == DELAY_CNT) ? 'b1 : 1'b0;

//----------------------------------------

//74HC595 shift data output state

reg [:] led_cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

shift_state <= ;

led_cnt <= ;

end

else

begin

case(shift_state)

: begin

led_cnt <= ;

if(update_flag)

shift_state <= 'b1;

else

shift_state <= ;

end

: begin

if(shift_flag)

begin

if(led_cnt < 'd8)

begin

led_cnt <= led_cnt + 'b1;

shift_state <= 'd1;

end

else

begin

led_cnt <= ;

shift_state <= ;

end

end

else

begin

led_cnt <= led_cnt;

shift_state <= shift_state;

end

end

endcase

end

end

assign led595_dout = (led_cnt < 'd8&&shift_state == 1'b1) ? led_data['d7-led_cnt]: 1'b0;

assign led595_clk = (led_cnt < 'd8&&shift_state == 1'b1) ? shift_clk : 'b0;

assign led595_latch = (led_cnt =='d8&&shift_state == 1'b1) ? 'b1 : 1'b0; endmodule

- 仿真

//-----------------------------------------------------------------------------------------

- 仿真代码--第一部分 --traffic_light

`timescale 1ns/1ns

module traffic_light

(

clk,

rst_n, //key_flagï¼

led_east,

//led_wast, led_south

//led_nouth );

parameter TIME_1S = ; input clk;

input rst_n; output [:] led_east;

//output [2:0] led_wast;

output [:] led_south;

//output [2:0] led_nouth;

//output key_flag; reg [:] led_east;

//reg [2:0] led_wast;

reg [:] led_south;

//reg [2:0] led_nouth; //reg key_flag; reg [:] cnt;

reg [:] cnt_l; //---------------------------------------------------------

//led_east

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_east <= 'b001;//G

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_east <= 'b010;//Y

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_east <= 'b100;//R

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_east <= 'b001;//G

else

led_east <= led_east;

end //---------------------------------------------------------

//wast

//always@(posedge clk or negedge rst_n)

//begin

// if(!rst_n)

// led_wast <= 3'b001;

// else if((cnt_l == 39)&&(cnt == TIME_1S-1'b1))

// led_wast <= 3'b010;

// else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1))

// led_wast <= 3'b100;

// else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1))

// led_wast <= 3'b001;

// else

// led_wast <= led_wast;

//end

//---------------------------------------------------------/////////////////////////////////////

//led_south

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_south <= 'b100;//R

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_south <= 'b001;//G

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_south <= 'b010;//Y

else if((cnt_l == )&&(cnt == TIME_1S-'b1))

led_south <= 'b100;//R

else

led_south <= led_south;

end

//---------------------------------------------------------

//led_nouth

//always@(posedge clk or negedge rst_n)

//begin

// if(!rst_n)

// led_nouth <= 3'b100;//R

// else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1))

// led_nouth <= 3'b001;//G

// else if((cnt_l == 63)&&(cnt == TIME_1S-1'b1))

// led_nouth <= 3'b010;//Y

// else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1))

// led_nouth <= 3'b100;//R

// else

// led_nouth <= led_nouth;

//end

//----------------------------------------------------------

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= ;

else if(cnt==(TIME_1S-'b1))

cnt <= ;

else

cnt <= cnt+'b1;

end always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_l <= ;

else if((cnt==(TIME_1S-'b1))&&(cnt_l==8'd67))

cnt_l <= ;

else if(cnt==(TIME_1S-'b1))

cnt_l <= cnt_l+'b1;

else

cnt_l <= cnt_l;

end //----------------------------------------------------------------------------

//wire key_trigger = ((cnt==TIME_1S-1'b1)&&((cnt_l==8'd39)||(cnt_l==8'd43)||(cnt_l==8'd67)||(cnt_l==8'd63))) ? 1'b1 : 1'b0; //wire key_trigger = (cnt==(TIME_1S-1'b1)) ? 1'b1 : 1'b0;

//---------------------------------

//Lag 1 clock for valid read enable

//always@(posedge clk or negedge rst_n)

//begin

// if(!rst_n)

// key_flag <= 0;

// else

// key_flag <= key_trigger;

//end endmodule

- 仿真代码--第二部分 --traffic_light_tb

`timescale 1ns/1ns

module traffic_light_tb; //------------------------------------------

//clock generate module

reg clk;

reg rst_n;

localparam PERIOD = ; //50MHz

initial

begin

clk = ;

forever #(PERIOD/)

clk = ~clk;

end task task_reset;

begin

rst_n = ;

repeat() @(negedge clk);

rst_n = ;

end

endtask

//------------------------------------------

wire [:] led_east;

wire [:] led_south;

traffic_light u_traffic_light

(

.clk(clk),

.rst_n(rst_n), .led_east(led_east),

.led_south(led_south)

); //---------------------------------------

//system initialization

task task_sysinit;

begin

// e_light = 3'b100; //?? R

// s_light = 3'b001; //?? G

end

endtask //----------------------------------------

//testbench of the RTL

initial

begin #; task_sysinit;

task_reset; end endmodule

- 仿真时序图

EDA课设-交通灯-Verilog版----FPGA--004的更多相关文章

- 基于BASYS2的VHDL程序——交通灯

请尊重作者版权,转载请注明原地址: http://www.cnblogs.com/connorzx/p/3676746.html 数电实验交通灯VHDL版,程序写的扩展性很差,待以后有时间进行优化. ...

- FPGA课设-基于Xilinx Basys2开发板的除法器设计

介绍一下Basys开发板: Basys2 FPGA开发板是一个电路设计实现平台,任何人都可以通过它来搭建一个真正的数字电路.Basys2是围绕着一个Spartan-3E FPGA芯片和一个Atmel ...

- 黑马程序猿_7K面试题之交通灯系统

交通灯信号模拟系统 一.概述 模拟实现十字路口的交通灯管理系统逻辑,详细需求例如以下:(需求直接来源于老师的文档) ① 异步随机生成依照各个路线行驶的车辆. 比如: 由南向而来去往北向的车辆 ...

- 【js课设】电子画板01

这学期web开发课的课设选了电子画板课题.(人家本来想做富文本编辑器的嘛然鹅老师在第二版里把这题删掉了。゚ヽ(゚´Д`)ノ゚。) 主要考虑的有[界面美观][画笔类型][画布分层]这三个点了. [界面美 ...

- C语言课设——电影院选票系统

C语言课设--电影院选票系统 1.课题介绍 大家都爱看电影,现请参考一个熟悉电影票预订系统,实现C语言版的订票系统.了解订票如何实现的.系统主要有2类用户:管理员用户和顾客用户. 管理员用户 1.电影 ...

- JAVA课设——中药古籍《太平圣惠方》数据处理与分析系统

一.配置JAVA环境 本次课设是在Windows 10(64bit)平台上实现的,所以首先得配置下JAVA环境. 步骤一:先下载一个JDK(1.7)安装包,安装好JDK: 步骤二:JDK环境配置(由于 ...

- 微型计算机系统实验总结(学习性实验:IO地址译码,可编程并行接口8255,交通灯控制实验 + 自主设计实验:汽车信号灯控制系统,电风扇控制器,洗衣机控制系统,霓虹灯,电梯控制系统)

实验配套软件: https://download.csdn.net/download/qq_39932172/11221584 实验指导用书: 教师版: https://download.csdn.n ...

- 黑马程序员——【Java高新技术】——案例:交通灯管理系统

---------- android培训.java培训.期待与您交流! ---------- 一.交通灯管理系统的项目需求 Ø 异步随机生成按照各个路线行驶的车辆 例如: 由南向而来去往北向的车辆 - ...

- 黑马程序员:Java编程_7K面试题之交通灯管理系统

=========== ASP.Net+Android+IOS开发..Net培训.期待与您交流!=========== 模拟实现十字路口的交通灯管理系统逻辑,具体需求如下: 异步随机生成按照各个路线行 ...

随机推荐

- P1063能量项链

传送 这又是一道经典的区间DP题. 复习一下区间DP的做法. 三重循环,第一层枚举区间长度,第二层枚举起点,第三层枚举断点. 区间长度是从1到n-1(因为如果是从1到n的话,1+n≠n,所以是1到n- ...

- 拒绝从入门到放弃_《Python 核心编程 (第二版)》必读目录

目录 目录 关于这本书 必看知识点 最后 关于这本书 <Python 核心编程 (第二版)>是一本 Python 编程的入门书,分为 Python 核心(其实并不核心,应该叫基础) 和 高 ...

- JavaScript 表单验证正则表达式大全

JavaScript 表单验证正则表达式大全[转载] 匹配中文字符的正则表达式: [u4e00-u9fa5] 评注:匹配中文还真是个头疼的事,有了这个表达式就好办了 匹配双字节字符(包括汉字在内):[ ...

- tp 框架 -文件上传

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 <?ph ...

- telnet批量检测端口状态(linux)

批量检测端口通信: 准备文件树状图 telnet.sh 脚本内容如下: 文件说明 telnet_alive.txt : 活动的端口 telnet_die.txt : 离线的端口 telnet ...

- Java thread(1)

这一部分主要讨论 java多线程的基本相关概念以及两种java线程的实现方式: 线程与进程: 这个操作系统书上介绍得很详细,这里就列出一些比较主要的: 线程: 线程本身有很少的资源,因为所拥有的资源较 ...

- ScoutSuite:一款针对云集群环境的安全审计工具

工具介绍 Scout Suite是一款针对云集群环境的开源安全审计工具,主要针对的是云端环境的安全状况.通过使用云服务提供商暴露的API,Scout Suite可以从高安全风险区域收集配置数据以备研究 ...

- [Python3] 021 面向对象 第一弹

目录 1. 面向对象概述 1.1 OOP 思想 1.2 几个名词 1.3 类与对象 2. 类的基本实现 2.1 类的命名 2.2 如何声明一个类 2.3 如何实例化一个类 2.4 如何访问对象成员 2 ...

- RedHat可用的几处软件源

rpmforge仓库 http://repoforge.org/use/ http://rpms.famillecollet.com/

- P3826 [NOI2017]蔬菜

传送门 注意每一单位蔬菜的变质时间是固定的,不随销售发生变化 固定的...... 就是每一个单位的蔬菜在哪一天变质是早就定好了的 发现从第一天推到最后一天很不好搞 考虑反过来,从最后一天推到第一天,这 ...