Verilog分频器的设计

大三都要结束了,才发现自己太多东西没深入学习。

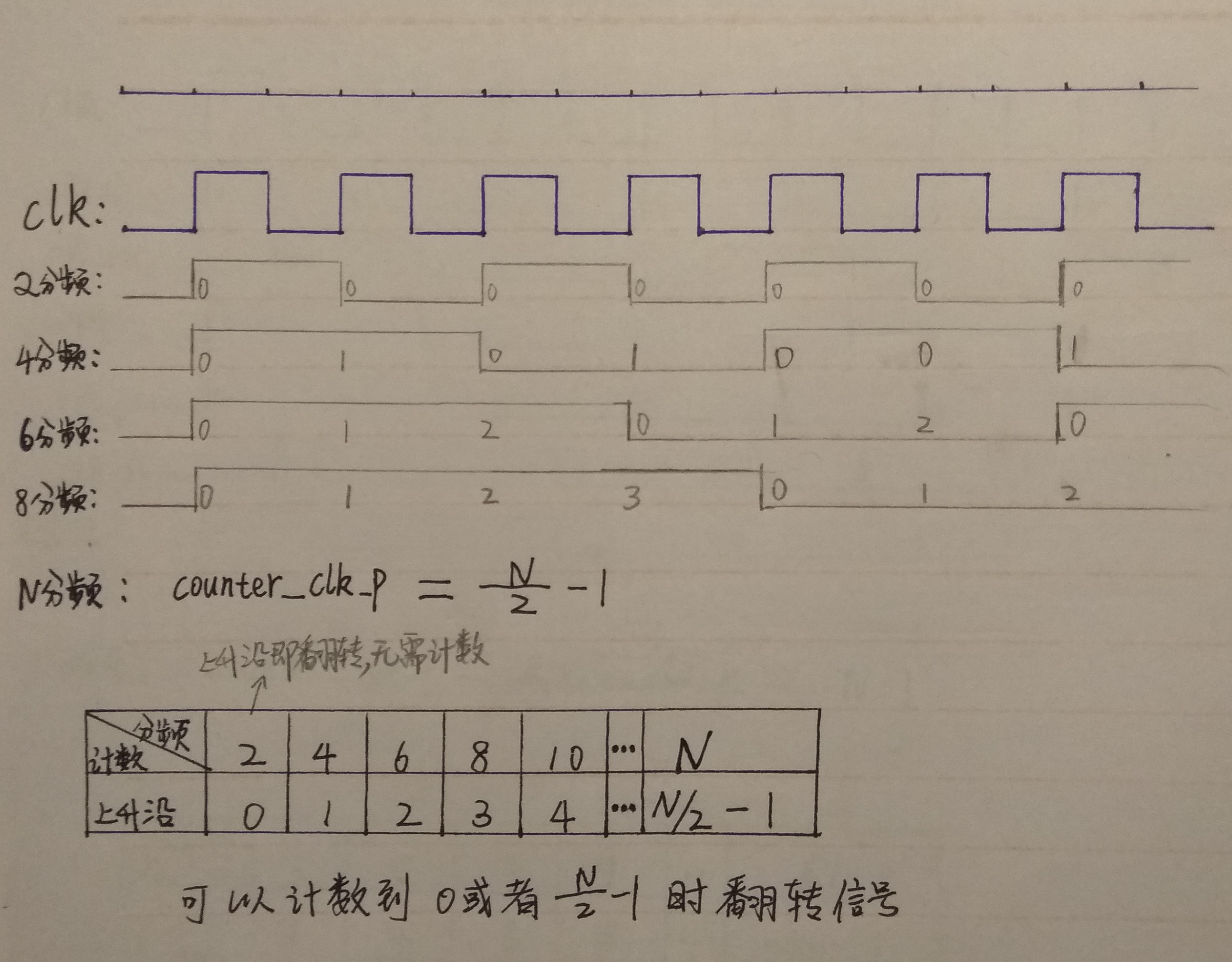

对于偶分频:(计数到分频数的一半就翻转)

注:

图中只用了一个计数器,当然也可以用多个;

图中只计数到需要分频的一半,当然也可计数到更多;

图中从第一个上升沿有效,当然也可延迟多个周期开始。

例如:

//任意偶分频设计

module frequency_divider_6 (clk, rst, data_out);

input clk, rst;

output data_out;

reg [:] counter;

reg data_out;

parameter N = ; //改变N的值变成任意偶分频,同时counter的范围需要相应修改 always @ (posedge clk or negedge rst)

begin

if (!rst) //复位置零

begin

counter <= ;

data_out <= ;

end

else //分频

begin

if (counter == N/ - ) //偶分频数一半时反相

begin

data_out <= ~data_out;

counter <= ; //置0,从0计数

end

else

counter <= counter + ;

end

end

endmodule

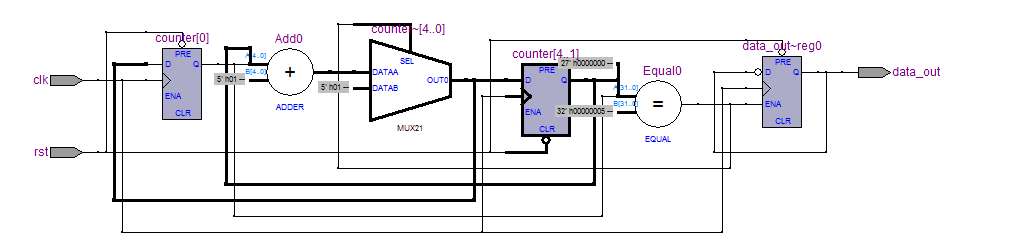

从仿真波形看出复位后并没有立刻达到分频效果,复位结束后的2.5个周期无效,之后才达到分频效果。

如果想从第一个上升沿就开始分频,那么就可以像我画的图中那样计数。如下所示:

/任意偶分频设计

module frequency_divider_6 (clk, rst, data_out);

input clk, rst;

output data_out;

reg [:] counter;

reg data_out;

parameter N = ; //改变N的值变成任意偶分频,同时counter的范围需要相应修改 always @ (posedge clk or negedge rst)

begin

if (!rst) //复位置零

begin

data_out <= ;

end

else //分频,也可用底下注释部分

begin

if (counter == ) //偶分频数一半时反相

begin

data_out <= ~data_out;

end

else

data_out <= data_out;

end

end

always @ (posedge clk or negedge rst)

begin

if (!rst)

begin

counter <= ;

end

else

begin

if (counter == (N / - ))

begin

counter <= ;

end

else

counter <= counter + ;

end

end

endmodule

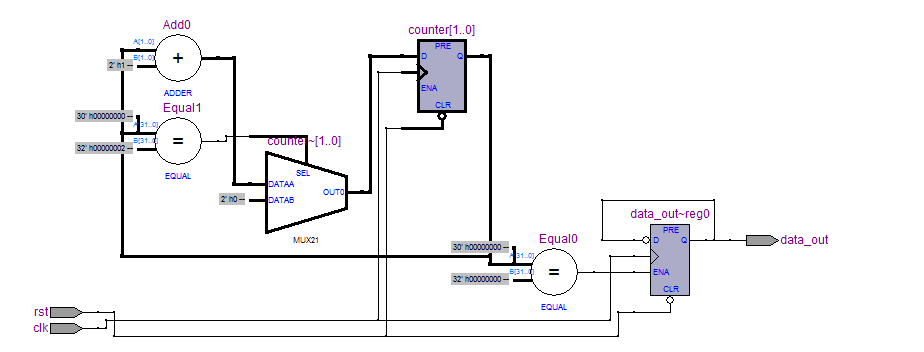

注意到此代码和上一个同样是6分频的,此处把计数部分和分频部分分离开来,可读性强一些吧。此处只计数到 2 就把计数器清零,计数到 0 输出的分频信号就翻转。

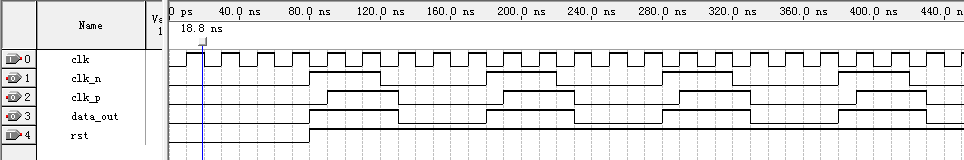

从仿真波形可看出从第一个上升沿就计数了。

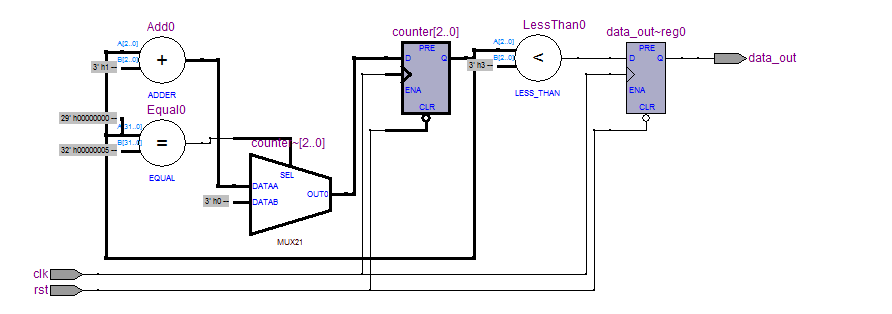

计数到 N - 1 (注意计数器位宽)例如:

//任意偶分频设计

module frequency_divider_6 (clk, rst, data_out);

input clk, rst;

output data_out;

reg [:] counter;

reg data_out;

parameter N = ; //改变N的值变成任意偶分频,同时counter的范围需要相应修改 always @ (posedge clk or negedge rst)

begin

if (!rst) //复位置零

begin

data_out <= ;//此处为1也可,看需求

end

else //分频,也可用底下注释部分

begin

if (counter < (N >> )) //偶分频数一半时反相

begin

data_out <= ;

end

else

data_out <= ;

end

end

always @ (posedge clk or negedge rst)

begin

if (!rst)

begin

counter <= ;

end

else

begin

if (counter == (N - ))

begin

counter <= ;

end

else

counter <= counter + ;

end

end

endmodule

写法多种多样,差别都不太大,不再一一举例,根据需求设计即可。

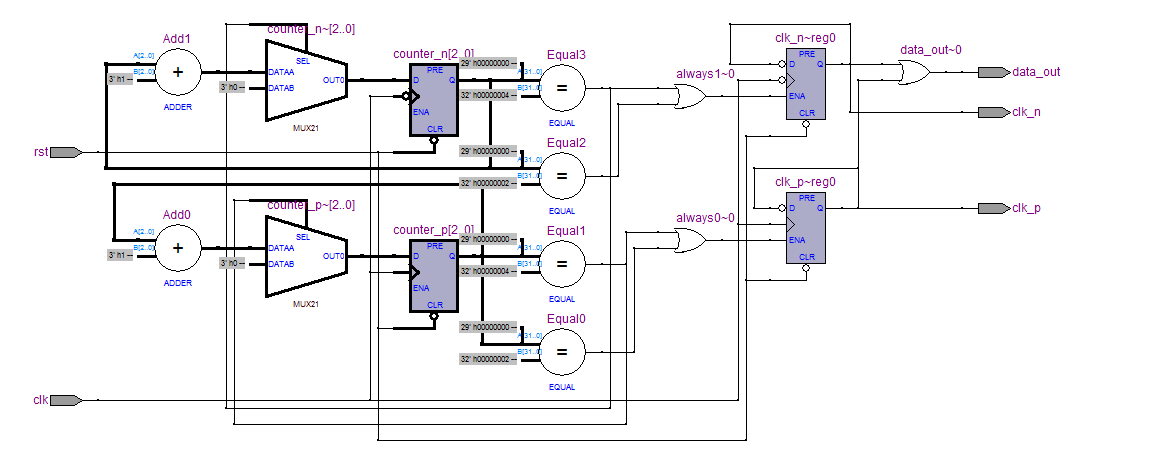

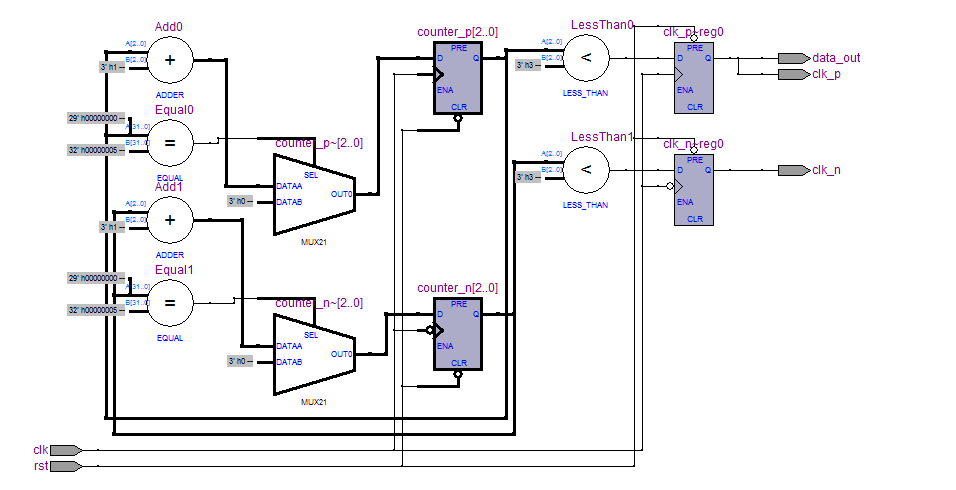

对于奇分频:(用两个计数器分别计到上升沿和下降沿达到分频数 (N - 1) / 2 和 (N + 1) / 2 时翻转)

注:

图中用了两个计数器,当然也可以用多个(两个就够了);

图中只计数到需要分频数的(N - 1) / 2 和 (N + 1) / 2,时翻转,得到的波形需要相或;

图中从第一个上升沿有效,当然也可延迟多个周期开始。

例如:

//任意奇分频设计

module frequency_divider_5 (clk, rst, clk_p, clk_n, data_out);

input clk, rst;

output clk_p, clk_n, data_out;

reg clk_p, clk_n;

reg [:] counter_p, counter_n;

parameter N = ; //改变N的值实现任意奇分频,注意counter_p和counter_n的范围

//分频

always @ (posedge clk or negedge rst) //上升沿计数与反相

begin

if (!rst) //复位置0,从0计数

begin

counter_p <= ;

clk_p <= ;

end

else

begin

if (counter_p == N - )

counter_p <= ;

else

counter_p <= counter_p + ;

if ((counter_p == (N - ) / ) || (counter_p == N - ))

clk_p <= ~clk_p;

end

end

always @ (negedge clk or negedge rst) //下降沿计数与反相

begin

if (!rst)

begin

counter_n <= ;

clk_n <= ;

end

else

begin

if (counter_n == N - )

counter_n <= ;

else

counter_n <= counter_n + ;

if ((counter_n == (N - ) / ) || (counter_n == N - ))

clk_n <= ~clk_n;

end

end

assign data_out = clk_p | clk_n; //相或运算,得到50%占空比的分频输出信号

endmodule

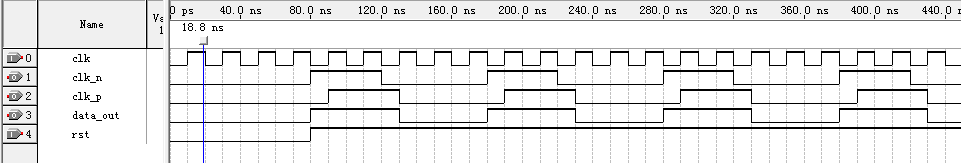

和偶分频同样的情况,复位后有多个无效周期。

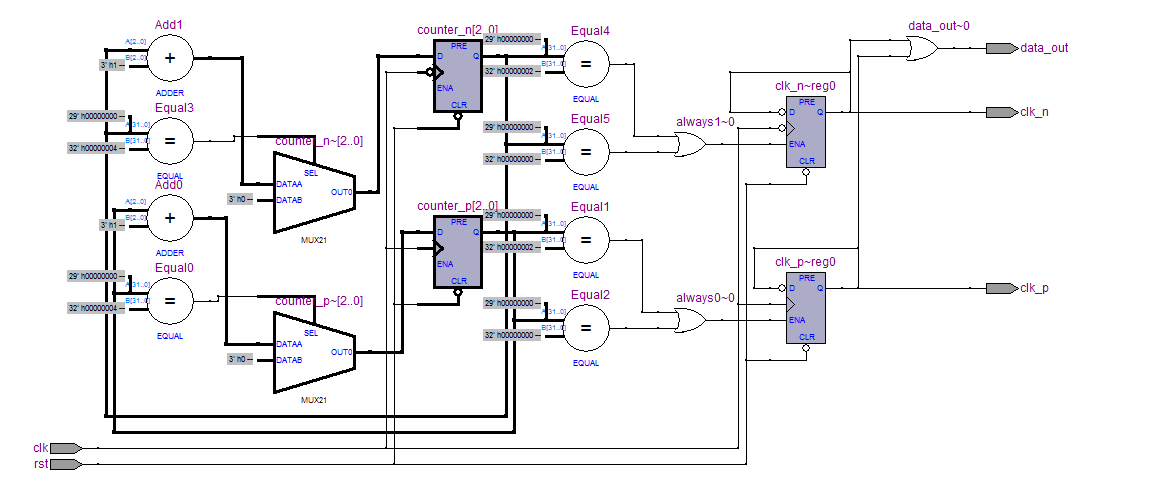

如果想从第一个上升沿就开始分频,那么就可以像我画的图中那样计数。如下所示:

从仿真波形可看出从第一个上升沿就计数了。

除此之外,还可以计数到这些就翻转:

1 和 (N - 1) / 2

(N - 1) / 2 和 N - 1

等等,根据需求即可

比如:

//任意奇分频设计

module frequency_divider_5 (clk, rst, clk_p, clk_n, data_out);

input clk, rst;

output clk_p, clk_n, data_out;

reg clk_p, clk_n;

reg [:] counter_p, counter_n;

parameter N = ; //改变N的值实现任意奇分频,注意counter_p和counter_n的范围 always @ (posedge clk or negedge rst) //上升沿计数器

begin

if (!rst)

counter_p <= ;

else

if (counter_p == N - )

counter_p <= ;

else

counter_p <= counter_p + ;

end

always @ (posedge clk or negedge rst) //上升沿反相

begin

if (!rst)

clk_p <= ;

else

if (counter_p < (N >> )) //N整体向右移动一位,最高位补零,其实就是N/2,不过在计算奇数的时候有很明显的优越性

clk_p <= ;

else

clk_p <= ;

end always @ (negedge clk or negedge rst) //下降沿计数器

begin

if (!rst)

counter_n <= ;

else

if (counter_n == N - )

counter_n <= ;

else

counter_n <= counter_n + ;

end

always @ (negedge clk or negedge rst) //下降沿反相

begin

if (!rst)

clk_n <= ;

else

if ((counter_n < (N >> ))

clk_n <= ;

else

clk_n <= ;

end

assign data_out = clk_p | clk_n; //相或运算,得到50%占空比的分频输出信号

endmodule

任意分频设计:

//下面是任意正整数的分频/ 此时举例是6倍频 /

module frequency_divider_all (clk, rst, data_out, clk_p, clk_n); input clk, rst;

output data_out, clk_p, clk_n; parameter WIDTH = ; //计数器二进制位宽

parameter N = ; //分频数(任意正整数) reg [WIDTH-:] counter_p;// 上升沿计数单位

reg [WIDTH-:] counter_n;// 下降沿计数单位

reg clk_p;// 上升沿时钟

reg clk_n;// 下降沿时钟 assign data_out = (N == ) ? clk : (N[]) ? (clk_p | clk_n) : clk_p;//其中N==1是判断不分频,N[0]是判断是奇数还是偶数,若为1则是奇数分频,若是偶数则是偶数分频。 always @ (posedge clk or negedge rst)

begin

if (!rst)

counter_p <= ;

else

if (counter_p == (N - ))

counter_p <= ;

else

counter_p <= counter_p + ;

end always @ (posedge clk or negedge rst)

begin

if (!rst)

clk_p <= ;//此处设置为0也是可以的,这个没有硬性的要求,不管是取0还是取1结果都是正确的。

else

if (counter_p < (N >> ))//N整体向右移动一位,最高位补零,其实就是N/2,不过在计算奇数的时候有很明显的优越性

clk_p <= ;

else

clk_p <= ;

end always @ (negedge clk or negedge rst)

begin

if (!rst)

counter_n <= ;

else

if (counter_n == (N - ))

counter_n <= ;

else

counter_n <= counter_n + ;

end always @ (negedge clk or negedge rst)

begin

if (!rst)

clk_n <= ;

else

if (counter_n < (N >> ))

clk_n <= ;

else

clk_n <= ;

end endmodule

总结

多思考总有新发现。

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!

本人博客:http://www.cnblogs.com/yllinux/

Verilog分频器的设计的更多相关文章

- verilog分频模块设计

verilog设计: 分频器的设计: 分频器就是将一个时钟源的频率降低的过程(可以通过观察分频之后周期中包含几个原时钟周期来看是几分频),分频分为基数分频也分为偶数分频, 偶数分频的代码如下:(其中就 ...

- Verilog学习笔记设计和验证篇(三)...............同步有限状态机的指导原则

因为大多数的FPGA内部的触发器数目相当多,又加上独热码状态机(one hot code machine)的译码逻辑最为简单,所以在FPGA实现状态机时,往往采用独热码状态机(即每个状态只有一个寄存器 ...

- Verilog分频器

verilog设计进阶 时间:2014年5月6日星期二 主要收获: 1.自己动手写了第一个verilog程序. 题目: 利用10M的时钟,设计一个单周期形状例如以下的周期波形. 思考: 最開始的想法是 ...

- 8421BCD转余3码Verilog HDL的设计(1)

近期阅读Verilog HDL高级数字设计(第二版)中,遇到了串行比特流BCD码转余3码转换器的设计,比较独特的是: (1)该转换器的输入为1位串行比特流,输出也为1位串行比特流. BCD码与余三码的 ...

- Verilog 分频器

verilog设计进阶 时间:2014年5月6日星期二 主要收获: 1. 自己动手写了第一个verilog程序. 题目: 利用10M的时钟,设计一个单周期形状如下的周期波形. 思考: 最开始的想法是: ...

- Verilog学习笔记设计和验证篇(五)...............层次化事件队列

详细的了解层次化事件队列有助于理解Verilog的阻塞赋值和非阻塞赋值功能.所谓层次化事件队列指的是用于调度仿真时间的不同Verilog事件队列.在IEEE的5.3节中定义了层次化事件队列在逻辑上分为 ...

- Verilog学习笔记设计和验证篇(一)...............总线和流水线

总线 总线是运算部件之间数据流通的公共通道.在硬线逻辑构成的运算电路中只要电路的规模允许可以比较自由的确定总线的位宽,从而大大的提高数据流通的速度.各个运算部件和数据寄存器组可以通过带有控制端的三态门 ...

- Verilog学习笔记设计和验证篇(二)...............同步有限状态机

上图表示的就是数字电路设计中常用的时钟同步状态机的结构.其中共有四个部分产生下一状态的组合逻辑F.状态寄存器组.输出组合逻辑G.流水线输出寄存器组.如果状态寄存器组由n个寄存器组成,就可以记忆2^n个 ...

- verilog乘法器的设计

在verilog编程中,常数与寄存器变量的乘法综合出来的电路不同于寄存器变量乘以寄存器变量的综合电路.知乎里的解释非常好https://www.zhihu.com/question/45554104, ...

随机推荐

- centos6.4安装过程中无法出现图形化界面

今天在VMware9.0安装centos6.4的时候,前面的步骤都没问题,到跳过媒体检查这一步后,就发现和之前的不一样了,这次安装不是图形界面,导致后面的安装不方便 一开始以为是centos的版本不一 ...

- Python集合字典运算符

1.集合2.字典3.运算符优先级 1.集合 创建:{} set([]) 注意:创建空的集合要用set() 特点:元素唯一,无序 运算: & 交集 | 并集 - 差集 方法: s ...

- Photoshop入门教程(五):滤镜

学习心得:滤镜通常用于摄影行业,是安装在相机镜头前用于过滤自然光的附加镜头,从而获得一些特殊的效果.同理,Photoshop的滤镜也是为了产生特殊的效果.Photoshop滤镜分为两类:一种是内部滤镜 ...

- 问题解决Determine IP information for eth0.. no link present check cable

网上方法都没有解决:简单粗暴编辑里还原了默认设置OK了 网上方法1 一般解决办法: 第一步: 到/etc/sysconfig/network-scripts/ifcfg-eth<n>/et ...

- Vuejs 实现权限管理

程序运行时,router只配置登陆 首页404 等基本页面 import Main from '@/views/Main.vue'; // 不作为Main组件的子页面展示的页面单独写,如下 expor ...

- flume failed to start agent because dependencies were not found in classpath

FLUME_CLASSPATH=/root/flume/lib/ copied comon jar files from hadoop folder to the flume folder. cp / ...

- vue首次赋值不触发watch(deep immediate handler)

deep:默认值是 false,代表是否深度监听.immediate:true代表如果在 wacth 里声明了之后,就会立即先去执行里面的handler方法,如果为 false就跟我们以前的效果一样, ...

- 转 Django中的Form

https://www.cnblogs.com/chenchao1990/p/5284237.html Form 一.使用Form Django中的Form使用时一般有两种功能: 1.生成html标签 ...

- Microsoft使用技巧

1.拍摄屏幕内容的截图 按 Win + Shift + S 以打开截图栏,然后将光标拖动到要捕获的区域. 截图区域将保存到剪贴板. 2.使用键盘添加表情符号 随心随处表达自我. 按 Ctrl + Sh ...

- Mybatis学习笔记3 - 增删改查示例

1.接口定义 package com.mybatis.dao; import com.mybatis.bean.Employee; public interface EmployeeMapper { ...