利用IP核设计高性能的计数器

利用Quartus II的LPM_counter IP核进行设计(利用IP核设计可以迅速高效的完成产品的设计)

新建工程

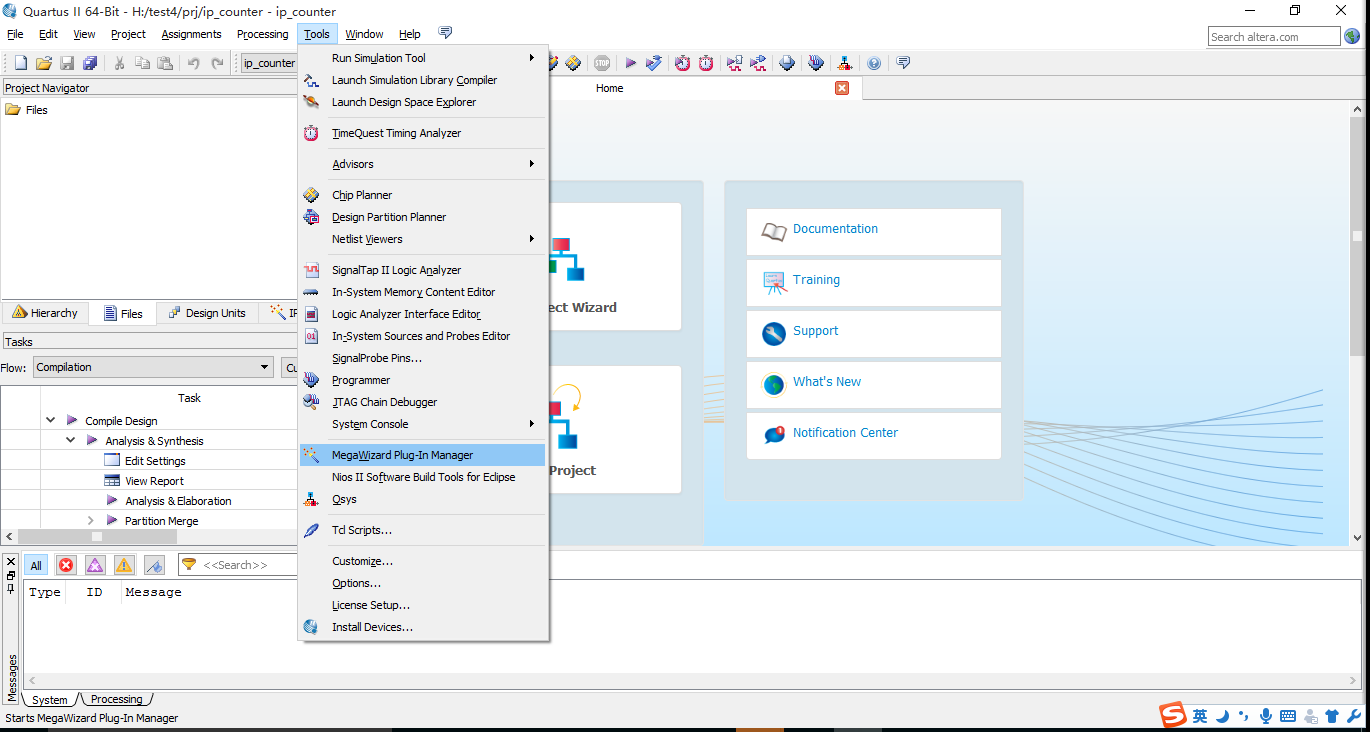

调用IP核

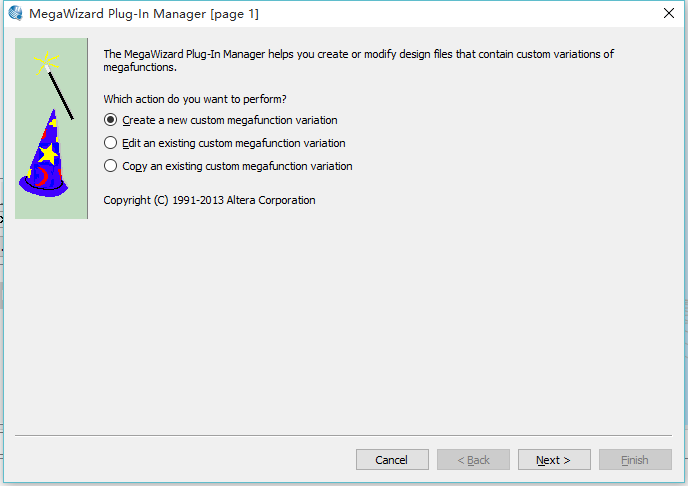

创建一个新的IP核

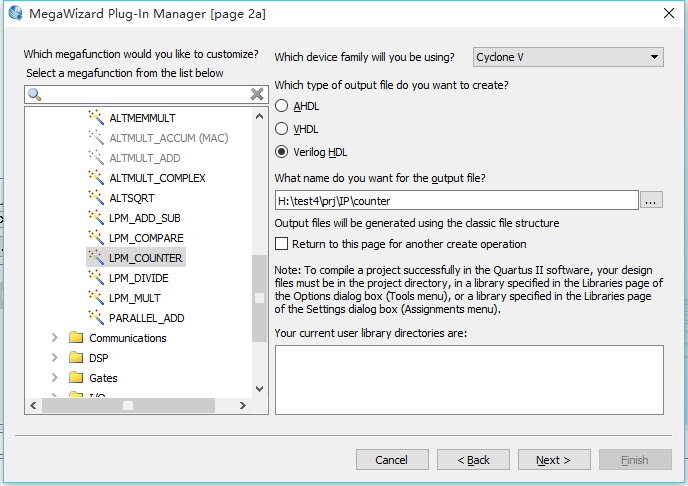

选择LMP_COUNTER,语言类型,输出路径。

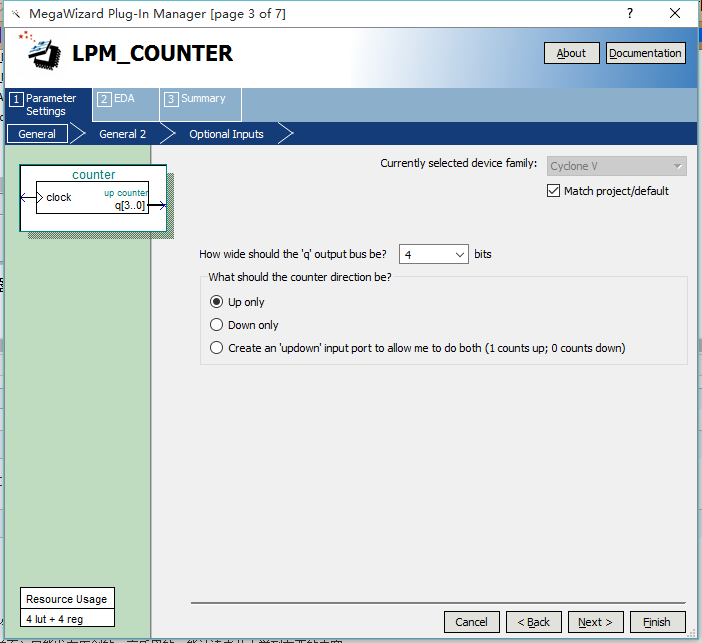

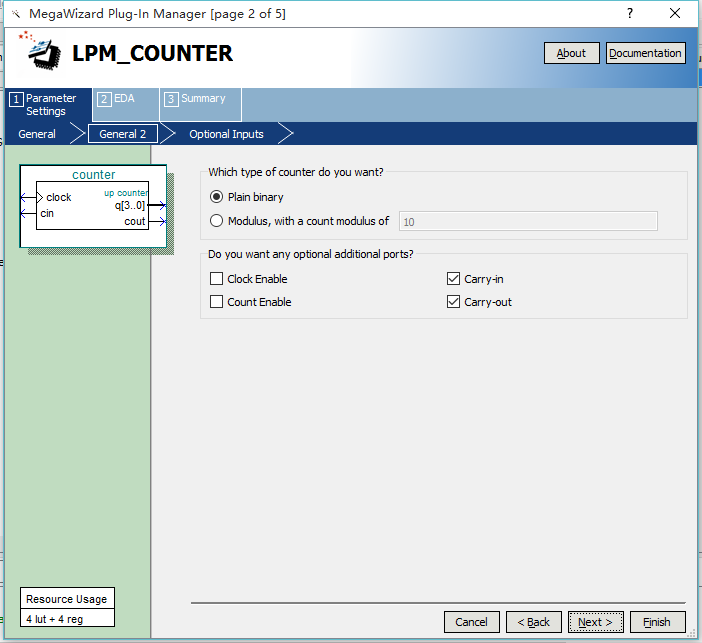

选择希望输出的寄存器是多少位的,计数类型,

选择计数器类型(直接计数还是以模的形式计数),是否需要时钟使能和计数使能信号、进位链的输入和进位链的输出。

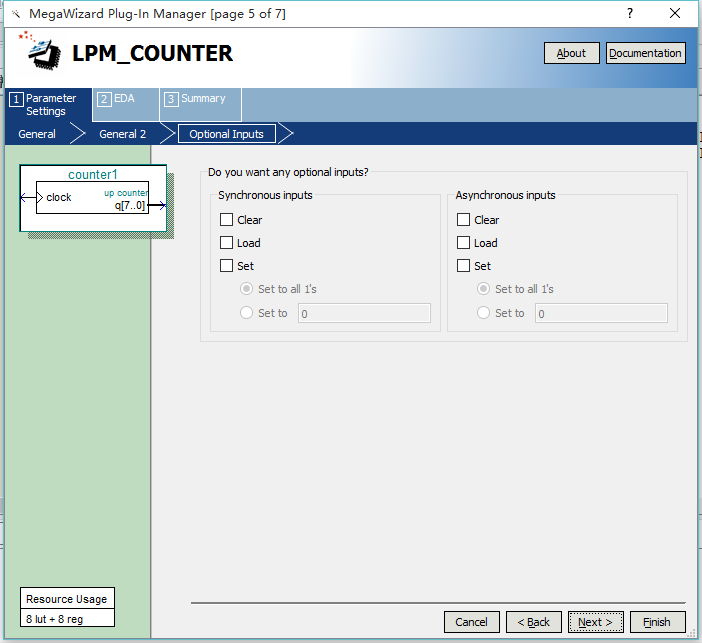

清零加载等信号

之后一直next直到finish

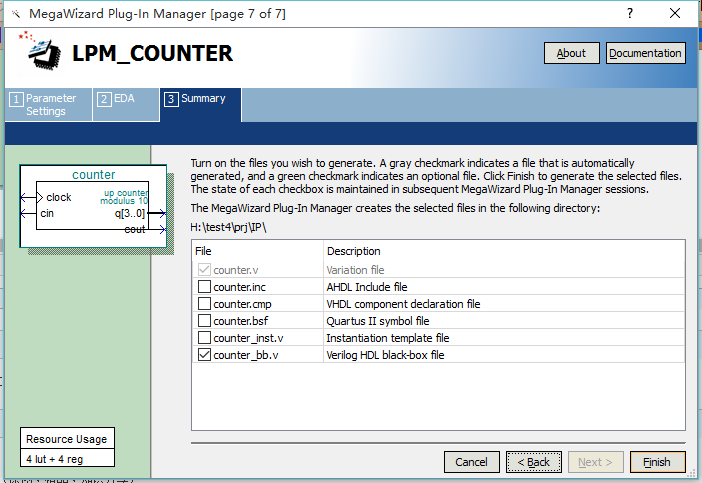

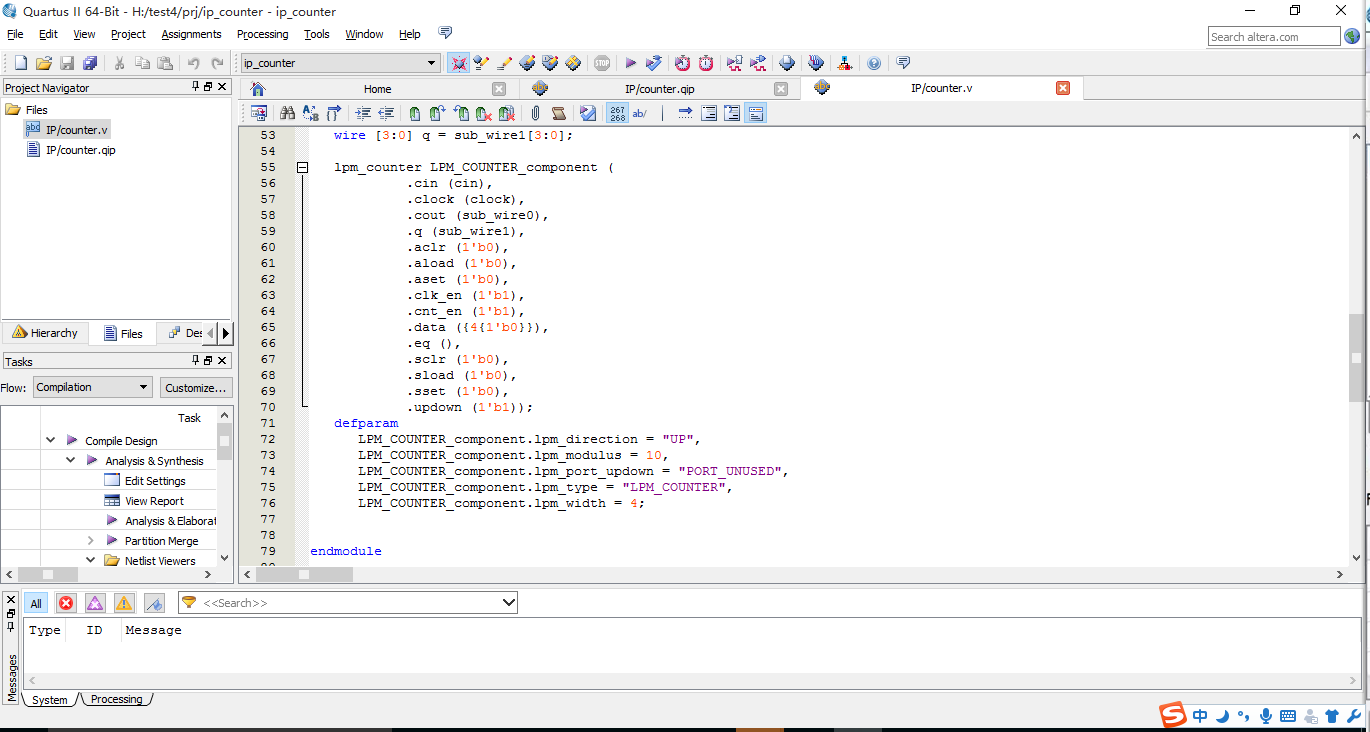

创建成功后的IP核的文件信息

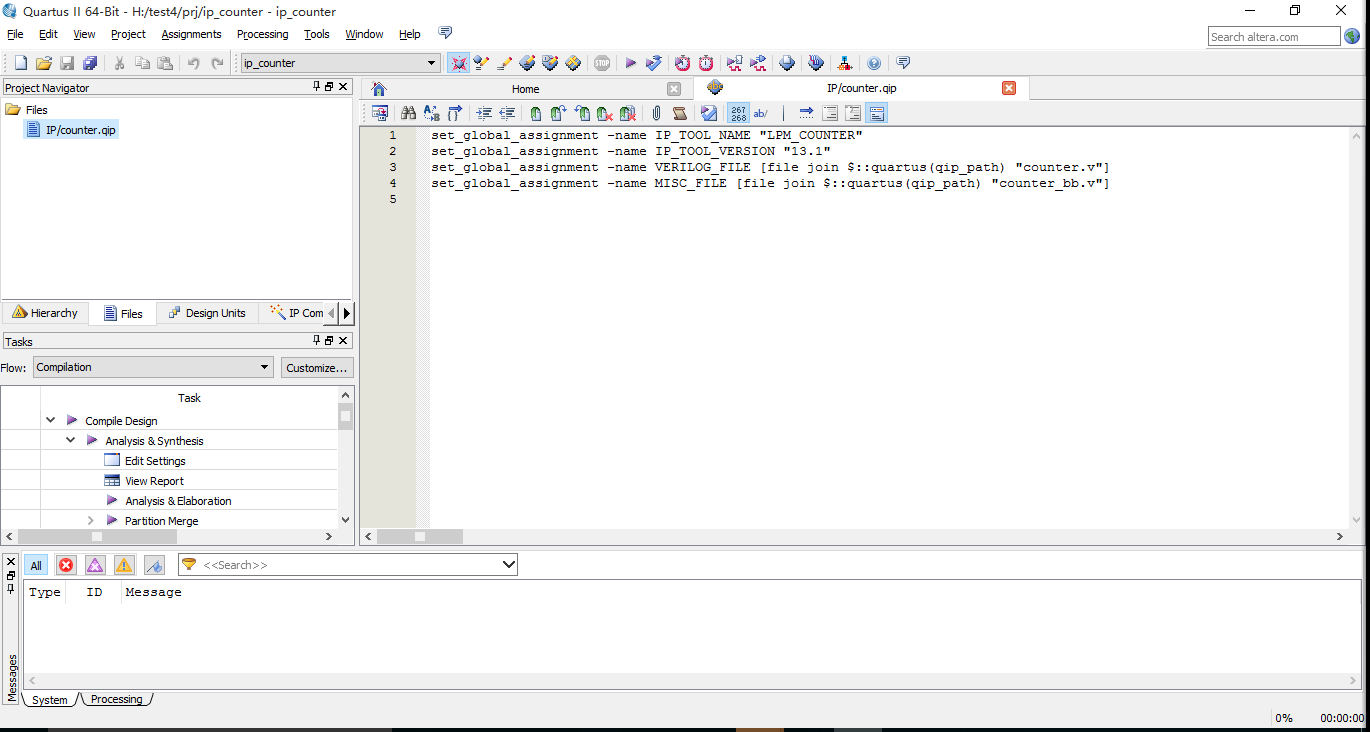

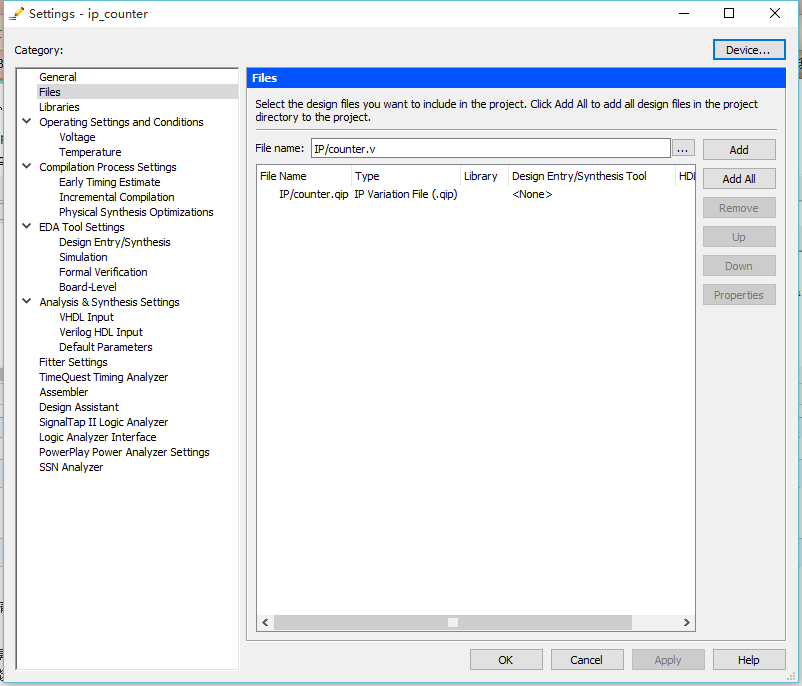

将counter.v文件加载到软件中

打开可以看到其中的接口文件。

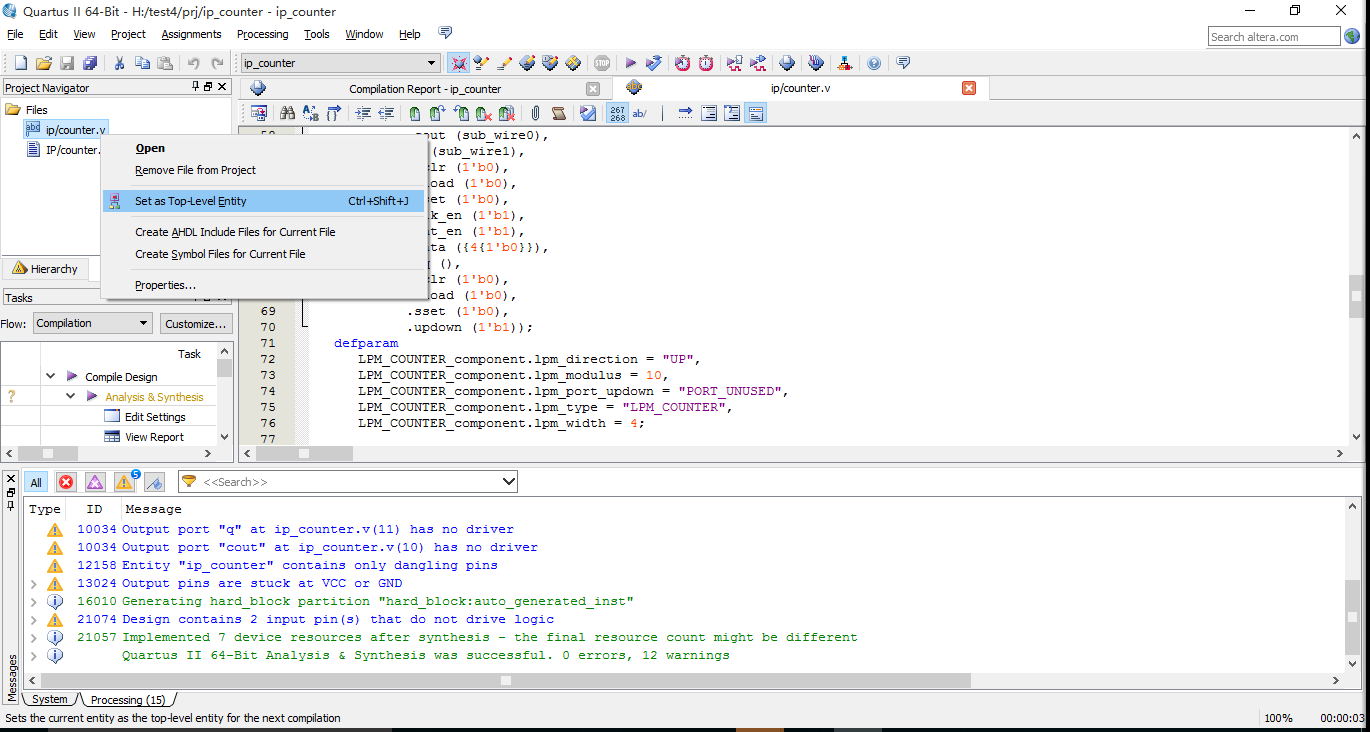

把ip_counter设置为顶层文件后进行编译。

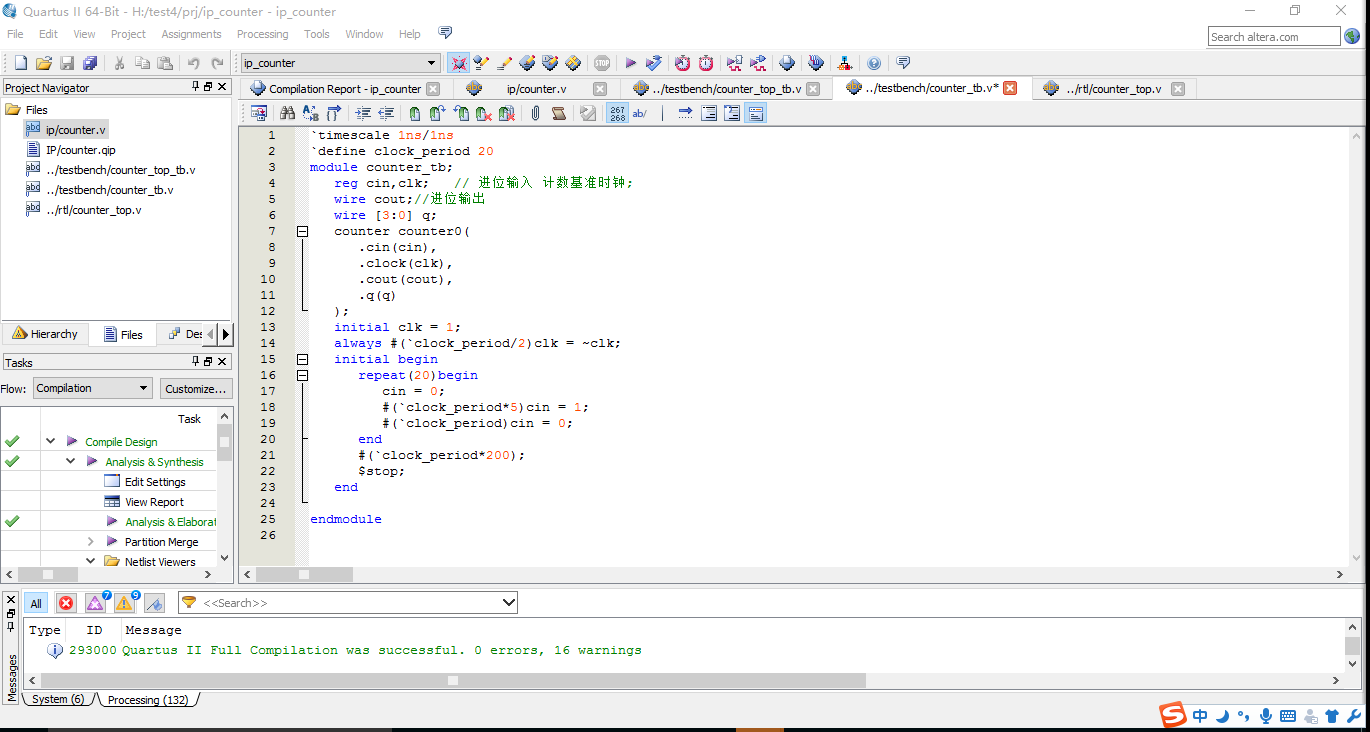

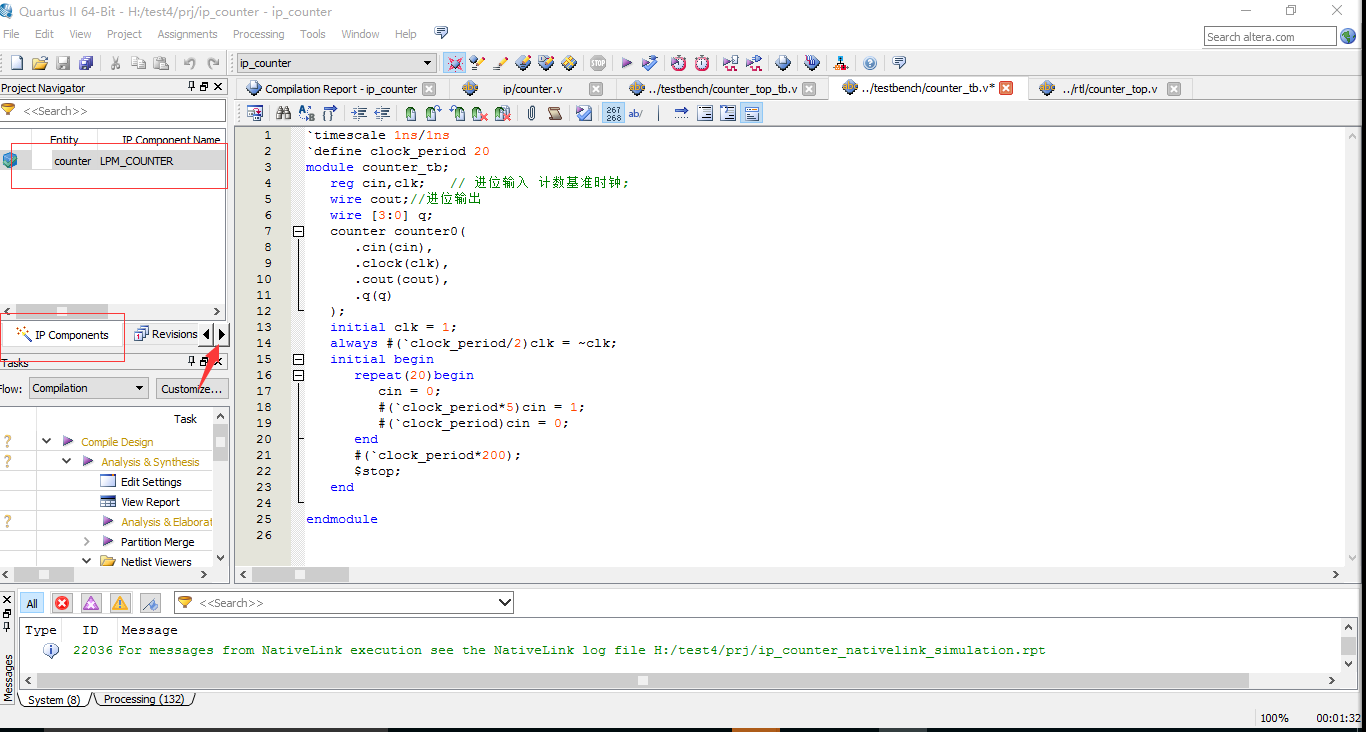

编写testbench文件

`timescale 1ns/1ns

`define clock_period 20

module counter_tb;

reg cin,clk; // 进位输入 计数基准时钟;

wire cout;//进位输出

wire [3:0] q;

counter counter0(

.cin(cin),

.clock(clk),

.cout(cout),

.q(q)

);

initial clk = 1;

always #(`clock_period/2)clk = ~clk;

initial begin

repeat(20)begin

cin = 0;

#(`clock_period*5)cin = 1;

#(`clock_period)cin = 0;

end

#(`clock_period*200);

$stop;

end

endmodule

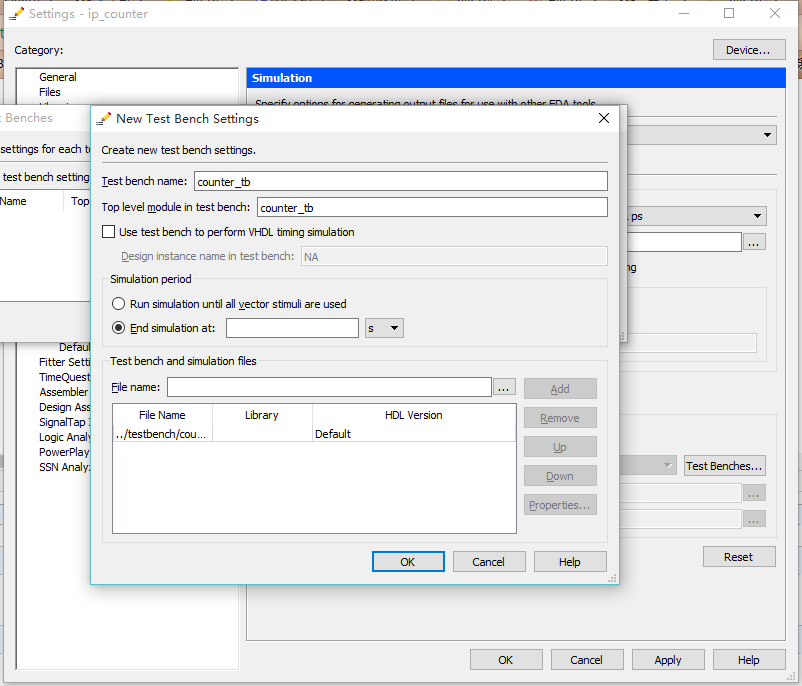

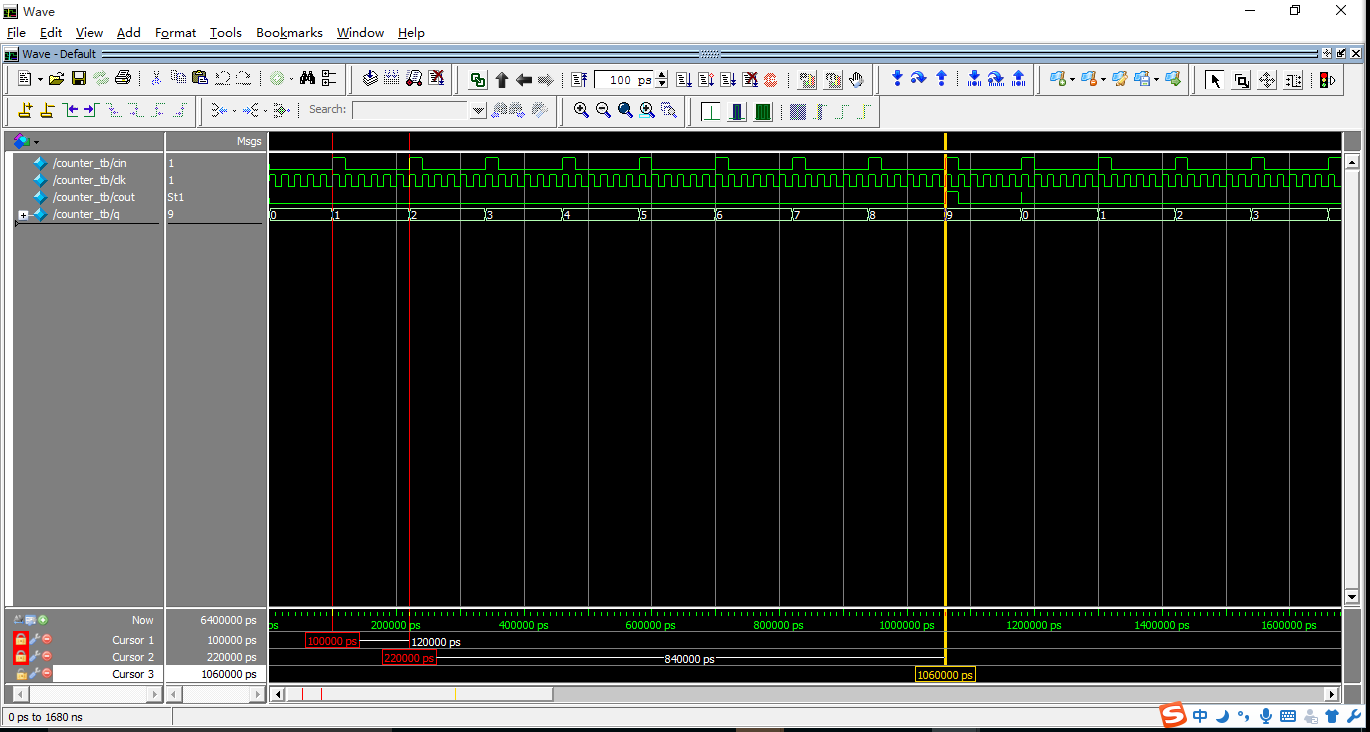

设置仿真链

运行 仿真,可以看到每隔5个clk有一个cin信号,计数器完成一次计数,到计数到设定的模值10时会产生一次c_out信号,然后计数器重新开始从0开始计数,与设计的期望。

在软件中点击箭头指向的方向键,左右切换显示到IP components,双击方框中的文件可以修改IP核的设置。

但是,IP核设置的位数是有上限的,为了提供更好的方法,下面提供一种级联的方法对计数值进行拓展。

在IP核中将计数模值改为直接技术模式

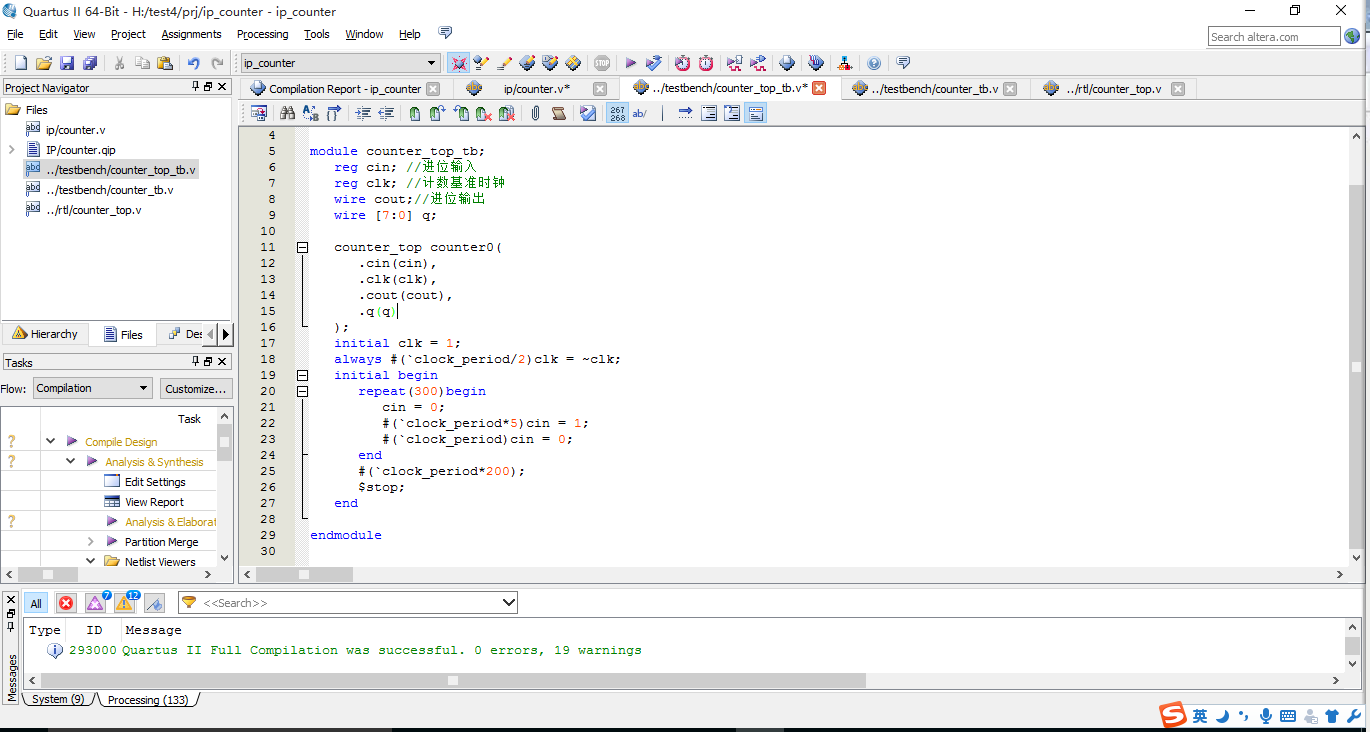

新建Verilog文件进行编程如下。

module counter_top(cin,clk,cout,q);

input cin;

input clk;

output cout;

output [7:0]q;

wire cout0;

counter counter0(

.cin(cin),

.clock(clk),

.cout(cout0),

.q(q[3:0])

);

counter counter1(

.cin(cout0),

.clock(clk),

.cout(cout),

.q(q[7:4])

);

endmodule

这里的原理是将前一级的c_out作为下一级计数的c_in,此时即将两个计数器级连起来了,这样就将一个四位的计数器转换成了一个八位的计数器。

将这个文件设置为顶层文件

编写testbench如下

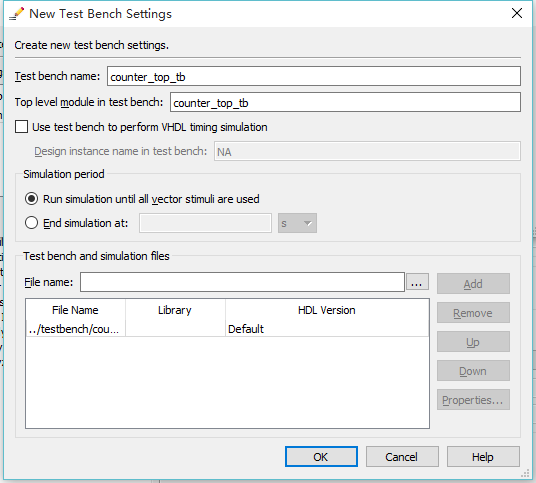

设置仿真脚本

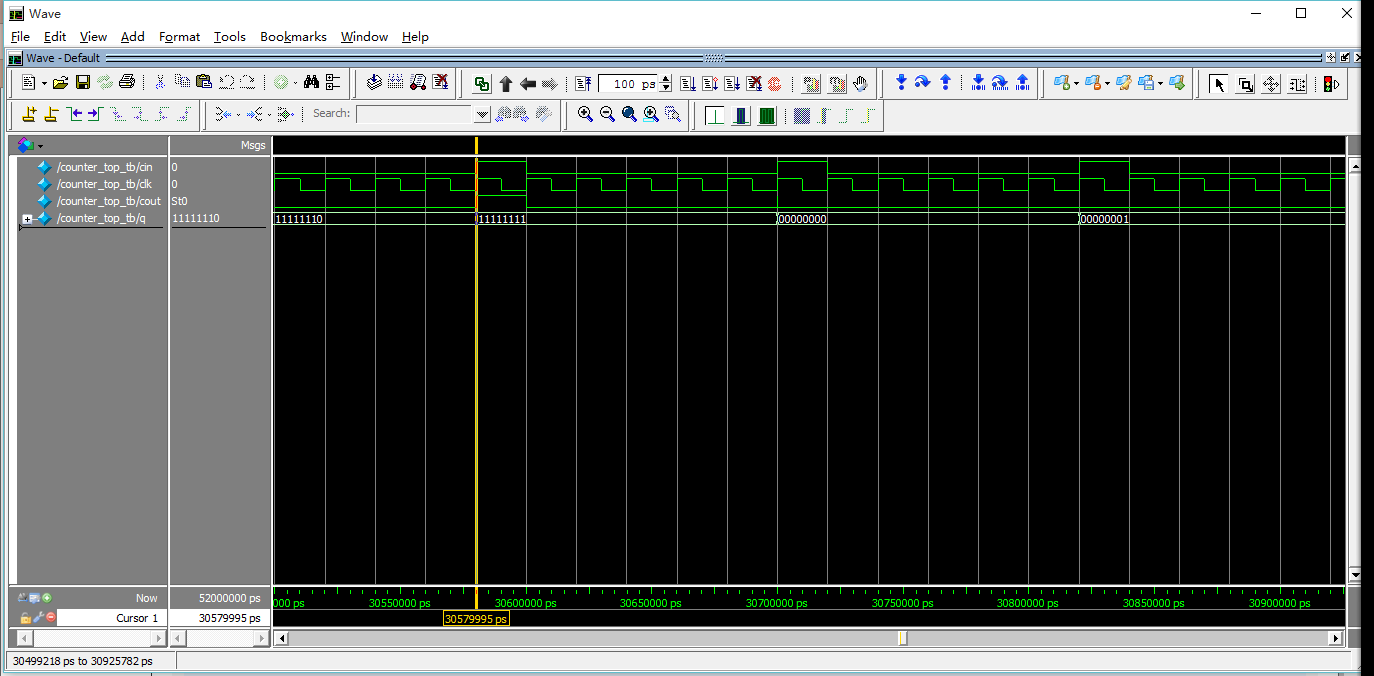

点击仿真工具进行仿真可以看到计数为8个1时输出c_out ,这与我们期望的是一样的。

至此,基于IP核设计一个计数器的方法就设计完成了。可以对应的将c_out,输出到LED上进行观察,这里就不再实际操作了。

利用IP核设计高性能的计数器的更多相关文章

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- IP包设计

IP包 IP核(Intellectual Property core)就是知识产权核或知识产权模块的意思,用于配置FPGA或其它硅芯片上的逻辑资源. 引用链接https://blog.csdn.net ...

- 计数器IP核

Quartus II提供的LPM_couter IP核的使用 FPGA设计方式: 原理图,Verilog HDL设计方式,IP核输入方式 创建IP核 点击TOOLS—IP catalog-libray ...

- Vivado使用技巧(二):封装自己设计的IP核

由 judyzhong 于 星期五, 09/08/2017 - 14:58 发表 概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原 ...

- Vivado设计二:zynq的PS访问PL中的自带IP核(基于zybo)

1.建立工程 首先和Vivado设计一中一样,先建立工程(这部分就忽略了) 2.create block design 同样,Add IP 同样,也添加配置文件,这些都和设计一是一样的,没什么区别. ...

- Vivado使用技巧:封装自己设计的IP核

概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原理图设计的方式,只需要在其中调用设计好的IP核连线.IP核一部分来自于Xilinx ...

- Altera三速以太网IP核使用(下篇)--- 百兆网接口设计与使用

MAC IP核的主要作用是:实现数据链路层协议,分为TX方向与RX方向,TX方向实现的是在原包文的前面加上7个55和1个D5,RX方向则相反.在使用这个 MAC IP核之前,首先确认下自己使用的网卡是 ...

- vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核. 那么接下来,我们对这个自定义IP核进行测试了:我们 ...

- Quartus设计FIR滤波器的系数文件格式(适用于FIR II的IP核)

对常用的FIR,我们使用MATLAB的fdatool(或者filterDesigner) 设计滤波器,给定指标,生成系数.为了方便,我们将系数保存到文件,其保存格式比较简介,在此进行说明. 1.FIR ...

随机推荐

- pass parameter by endpoint, this is for websocket

使用了Java的字符串:@ServerEndpoint("/chat/{room}")public class MyEndpoint {@OnMessagepublic void ...

- 李清华201772020113《面向对象程序设计(Java)》第六周学习总结

第一部分 理论知识 1.继承 用已有类来构建新类的一种机制.新类可以继承父类的方法和域,同时可以在新类中添加新的方法和域. 已有类称为:超类.基类或父类.新类称作:子类.派生类或孩子类. 子类的构造器 ...

- c#操作excel方式三:使用Microsoft.Office.Interop.Excel.dll读取Excel文件

1.引用Microsoft.Office.Interop.Excel.dll 2.引用命名空间.使用别名 using System.Reflection; using Excel = Microsof ...

- spring @transactional 注解事务

1.在spring配置文件中引入<tx:>命名空间 <beans xmlns="http://www.springframework.org/schema/beans&qu ...

- springboot注解大全

springboot注解:@Service: 注解在类上,表示这是一个业务层bean@Controller:注解在类上,表示这是一个控制层bean@Repository: 注解在类上,表示这是一个数据 ...

- Jenkin配置执行远程shell命令

转载自 http://www.cnblogs.com/parryyang/p/6261730.html 在利用jenkins进行集成化部署的时候,我们在部署生成的war包时,往往需要进行一些备份,或者 ...

- 【Django】关于设置和获取cookies

def TestCookies(request): response=HttpResponse() # cookie=request.COOKIES#下面两句等cookies设置以后,才使用 # if ...

- 织梦会员 Warning: preg_replace(): The /e modifier is no longer supported, us...

http://php.net/manual/zh/reference.pcre.pattern.modifiers.php#reference.pcre.pattern.modifiers.eval ...

- C#删除文件夹以及删除文件

public static void DelectDir(string srcPath) { try { DirectoryInfo dir = new DirectoryInfo(srcPath); ...

- python基础 ---- 使用pyCharm 调试

debug -- 为了分析程序的异常 单步调试 1.设置断点 2.debug.启动 3.监控变量