verilog之时钟信号的编写2

verilog之时钟信号的编写2

1、时钟信号的特点

时钟信号除了可以根据时序一个个变化列举出来,还可以利用其循环的变化的特点,使用循环执行语句always来实现。这种方法实现的时钟信号可以一直执行且不需要关注每个变化点的延时。

2、基于begin-end块的时钟信号

initial begin

clk=0;

clk1=0;

clk2=0;

end

//way1

always #1 clk=~clk;

//way2

always begin

#1 clk1=~clk1;

#1 clk2=~clk2;

end

方法1是最方便的时钟信号,只有一条执行语句,甚至不需要使用块来封装。

方法2则是使用begin-end来实现两个时钟信号clk1和clk2,可以简单地分析出clk2的周期是clk1的两倍。clk1是2系统周期,clk2是4系统周期。占空比就是50%,一条语句是无法实现其他占空比的时钟信号的。

3、基于fork-join块的时钟信号

initial begin

clk=1;

clk1=1;

end

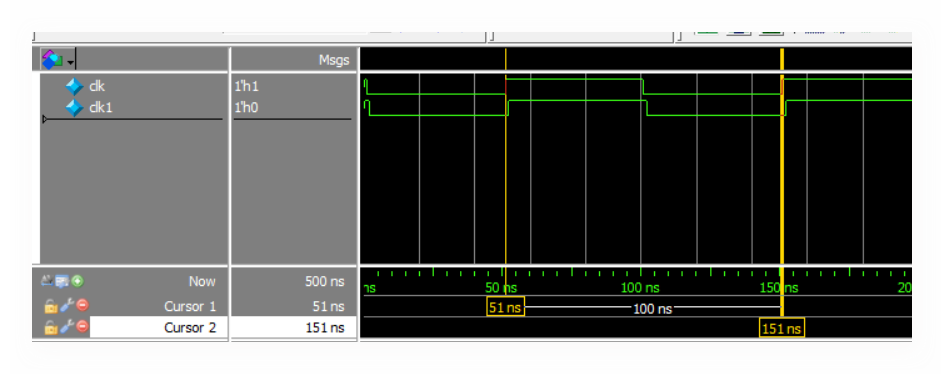

always fork

#1 clk=~clk;

#2 clk1=~clk1;

#3 ;

#50 ;

join

可以观察到fork-join的时钟信号的周期是最大延时的两倍。每个时钟信号的周期都是一致的。其他延时只会改变时钟信号的相位。从这里也可以看出fork-join的块的工作原理:先找到最大延时,其他延时执行语句在其子期间中显示。使用fork-join可以仿真有时钟延时的信号输入。

4、小结

使用循环执行语句来实现时钟信号是常用的方法。一般的时钟信号的激励也是利用循环执行来模拟的。

verilog之时钟信号的编写2的更多相关文章

- Verilog 语言 001 --- 入门级 --- 编写一个半加器电路模块

Verilog 语言编写一个 半加器 电路模块 半加器 的电路结构: S = A 异或 B C = A 与 B 1. 程序代码 module h_adder (A, B, SO, CO); input ...

- 用Sublime Text搭建简易IDE编写Verilog代码

前言 Verilog是一种硬件描述语言(HDL),该语言在Windows上有集成开发环境可以使用,如ModelSim,但ModelSim的编辑器不太好用因此笔者萌生了用Sublime Text3来编写 ...

- FPGA —— Quartus II 15.0 使用 ModelSim SE-64 2019.2 软件进行仿真

Quartus II 15.0 使用 ModelSim SE-64 2019.2 软件进行仿真 ModelSim 仿真 Verilog HDL 时需要编写一个 TestBench 仿真文件,通过仿真文 ...

- 基于串口调试助手的WIFI模块调试-FPGA简单联网(点灯)

根据正点原子的<ATK-ESP8266 WIFI用户手册>,使用XCOM V2.2串口调试助手测试WIFI模块[26].在本系统中运用到的功能主要是TCP/IP模式中的TCP Client ...

- [原创]迈出NIOS的第一步,HelloNIOS

Altera官方推出NIOS已经很久了,个人感觉C+V代码配合会是后面FPGA使用的一个主流,由C来完成一些对时序要求不高,对功能要求偏高的部分,比如运动控制等:由V来配合时序完成高时序要求的需求以及 ...

- vivado hls(1)

笔记 1.vivado hls是fpga高级综合工具,可以将C语言转换成verilog代码,适合编写算法,但是要有硬件思想. 2.软核就是只要资源足够,就可以用逻辑打一个CPU出来,与硬核不一样,硬 ...

- sublime text 2使用方法

笔者用过的一些软件用来写Verilog代码,比如notepad+,ultra,editplus等,近日在群里看到大家在讨论一个比较有意思的软件,sublime text,才发现有种相见恨晚的感觉,其实 ...

- ISE、vivado、QuartusII调用notepad++、UE汇总(整理)

我已经用惯了notepad++编写Verilog代码,很喜欢这款编辑器,功能真的非常强大.所以,当需要对vivado.ISE或quartus ii中的工程进行Verilog代码上的编写或修改时,只需双 ...

- 转载论文关于fir滤波器的fpga实现

摘 要 本文讨论的FIR滤波器因其具有严格的线性相位特性而得到广泛的应用.在工程实践中,往往要求信号处理具有实时性和灵活性,本论文研究FIR的FPGA解决方案正体现了电子系统的微型化和单片化. 本论文 ...

- FPGA 开发详细流程你了解吗?

FPGA 的详细开发流程就是利用 EDA 开发工具对 FPGA 芯片进行开发的过程. FPGA 的详细开发流程如下所示,主要包括电路设计.设计输入.综合(优化).布局布线(实现与优化).编程配置五大步 ...

随机推荐

- CORS就是跨域吗?

首先,跨域的域是什么? 跨域的英文是:Cross-Origin. Origin 中文含义为:起源,源头,出生地. 在跨域中,"域"指的是一个 Web 资源(比如网页.脚本.图片等) ...

- Shiro实战2-Springboot集成Shiro实战

说明 最近打算打造一个简易的权限管理系统,打算用shiro做认证和授权.本篇作为springboot集成shiro的入门实战案例记录下来,希望也可以帮到大家,代码整理自网络. 技术栈 springbo ...

- java学生管理系统(界面版)

运行截图 项目说明: 本系统界面我个人就从简设计了,本来打算使用windowbuilder插件设计的,可想到使用windowbuilder插件之后导致代码冗余,会影响到代码可读性,可能对小白不友好.虽 ...

- 【Filament】绘制圆形

1 前言 Filament环境搭建中介绍了 Filament 的 Windows 和 Android 环境搭,绘制三角形中介绍了绘制纯色和彩色三角形,绘制矩形中介绍了绘制纯色和彩色矩形,本文将使用 ...

- 前后端分离项目(八):后端报错Field 'id' doesn't have a default value

好家伙,又到了修bug的环节,(深叹一口气) 好了,来看报错 2022-10-29 23:27:52.155 WARN 15068 --- [nio-8011-exec-2] o.h.engine.j ...

- 【Azure 应用服务】用App Service部署运行 Vue.js 编写的项目,应该怎么部署运行呢?

问题描述 用App Service部署运行 Vue.js 编写的项目,应该怎么部署运行呢? 问题解答 VUE通常是运行在客户端侧的JS框架. App Service 在这种场景中是以静态文件的形式提供 ...

- 【Azure API 管理】APIM Self-Host Gateway 自建本地环境中的网关数量超过10个且它们的出口IP为同一个时出现的429错误

问题描述 Azure API Management服务支持使用自建网关来实现API服务,这样APIM的所有请求都可以走在自管理的企业内网中.流量都更加安全.当根据官网文档搭建后,如果在本地环境中部署超 ...

- ffmpeg 使用记录

这周周末尝试把我硬盘上面的视频文件压缩了一下,但是效果并不理想.其中主要有两个原因, 视频本来就是h264的编码,再重新编码也没啥用,因为限制大小的主要是码率 ffmpeg GPU加速版的h265编码 ...

- C#实现图片对比

前言 虽然已经正式转JAVA了,但最近发现一个特别好的开源项目masuit,不仅提供很多简便的功能,还有图像的一些特殊操作功能. 下面就实现一个简单图像对比. 实现对比 代码如下,实现一个可以对比翻转 ...

- C++ //常用算法 adjacent_find //查找相邻的重复元素

1 //常用算法 adjacent_find 2 //查找相邻的重复元素 3 #include<iostream> 4 #include<string> 5 #include& ...