使用组合逻辑电路驱动VGA显示器

使用组合逻辑电路驱动VGA显示器

1. 概述

本文讲述一种不使用缓冲存储器驱动VGA显示的简单方法.其中,VGA分辨率采用DE10-Lite建议使用的640X480.像素的时钟25MHz,刷新率59.5帧/秒.

在DE10-Lite实验板上,VGA接口使用4位数值表示色彩.全0表示不亮,全1表示亮度最高,红,黄,蓝的明度在4’b0000-4’b1111之间,表示不同亮度的色彩.

信号col和row表示VGA控制器驱动的像素地址.

2. VGA接口信号

VGA接口相对简单.信号v_sync(垂直同步)变低,表示一帧图像完成,并为下一帧图像做准备.这一点在下图可以看到.

同样,信号h_sync变低表示一行数据传输完成,并为下一行数据做准备,这个在上图放大后可以看到h_sync变低了数百次.

下图显示了一些波形的细节,在266行,信号v_sync和h_sync都是高的时侯,col和row计数的变化,这里没有显示红黄蓝的数值.

3. 开始编写VGA代码

代码设计参考vga.combinational2.zip,其中包含各个模块和PLL例化.

4. 模块说明

VGA工程的主要模块说明如下:

l pll.v,pll.qip,pll.ppf

为得到一个正确的时钟信号,用PLL例化,由50MHz生成25Mhz的时钟信号。

pll.qip给Quartus提供一些信息,器件,相关的Verilog文件,ppf文件。pll.v是PLL例化文件。pll.ppf提供各种输入/出引脚数据。

l vga_controller.v

这个模块生成VGA接收端需要的行和列同步信号。通常,并不需要h_sync,v_sync和disp_ena信号。像素显示总是从左到右,从上往下,起点是左上角那个(0,0)的像素点。为了方便定位像素点,VGA_controller输出两个信号:行和列坐标。row-纵坐标,col-横坐标。注意disp_ena为0时,这些信号无效。

l comb_ckt_generator.v

这是一个组合逻辑模块,用来决定实验板上10个SW开关对应位置的像素点的RGB的色彩值。

l top.v

这是本设计的顶层模块,例化vga_controller和产生寄存器的时序,色彩输出信号。

这里面注意RGB为4‘b0000和4’b1111时的色彩。

5.使用代码去驱动显示

上面提供的代码很简单。给定行,列坐标(row:0-479;col:0-649)。像comb_ckt_generator.v里显示的那样,要创建合适的逻辑给像素点赋值RGB。

通常,会使用缓存来现存储要显示的图像,再显示。这里因为MAX10 FPGA没有现成的足够数量的缓存,所以我们用前述方法替代。

6.时钟信号vga_clk

在这个设计里,所有触发器的同步时钟信号应该是25MHz,而不是50MHz。VGA接口的像素时钟也是25MHz。

7.关于帧更新的时间问题

在完成一帧画面传输至准备传输下一帧画面之间,要及时更新传输的数据。比如,快速移动的对象,不会一部分显示在这一块,一部分显示在另一块。

处理这个问题,最好的方法是使用同步信号,比如垂直同步信号(VGA_VS)。如同DE10-Lite用户手册所述,VGA接口信号包含特殊的时间间隔。前面提供的代码里已经解决了这个问题。

8.保持VGA输出同步

虽然comb_ckt_generator.v没有时钟输入,如果块的复杂性需要,当然可以添加时钟输入和时钟内部逻辑。在行列,同步信号间可以添加流水线控制。

9. 补充说明

VGA驱动电路的难点还是在于VGA时序控制模块,这里的代码采用了一个比较巧妙的设计,以行扫描为例来阐述.我们知道一行完整的数据传输需要行同步的时间+后沿+像素显示的时间+前沿,其中行同步时用来表明一行显示完,准备显示下一行,而前沿,后沿则是消隐的需要.代码里,为了使计数器的值从0开始就与像素的坐标匹配,所以行扫描的周期从像素显示开始计数,一行的计数顺序是像素显示+前沿_行同步+后沿.这样,通过限定最大值,就能确定坐标的范围,并且是从左上角那个点开始显示.

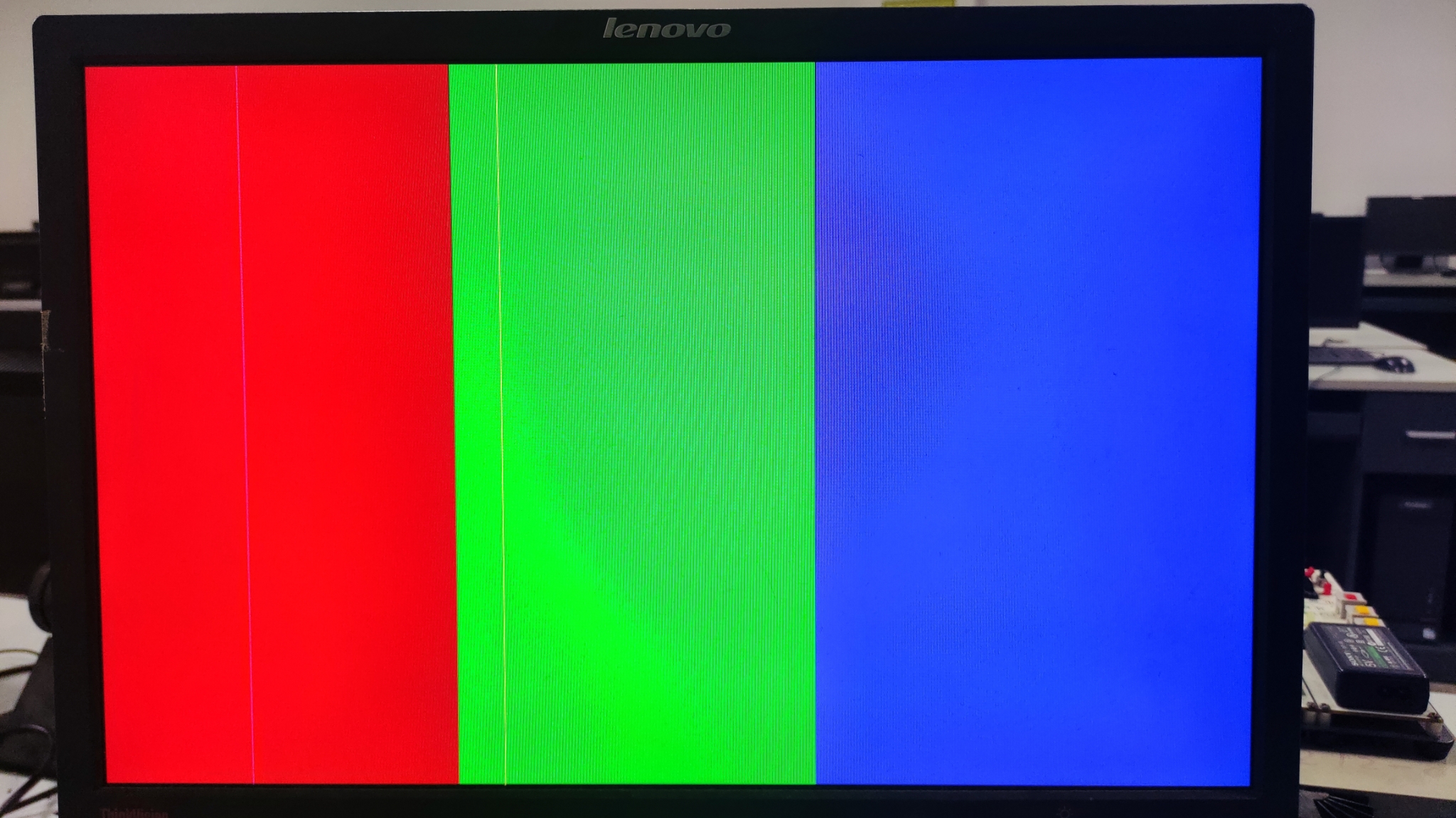

原设计是用3个SW开关来控制显示屏显示三种色彩或混合色.有了坐标和像素点的对应关系的理解后,可以稍稍把下图中85-87行的代码修改成col的区域,使屏幕显示不同的色块.

修改后可以实现类似

References:

- EEC180 Tutorial: Displaying to a VGA monitor using a combinational circuit

https://www.ece.ucdavis.edu/~bbaas/180/tutorials/vga/

Written by YongfengXie

2022/05/27 Written

使用组合逻辑电路驱动VGA显示器的更多相关文章

- 使用FPGA开发板驱动VGA显示器

1. 本次使用的是cyclone4开发板,先看下原理图,因为右边的RGB应该是模拟信号量,但是本次例程只接了3根线,那就是说颜色只有8种. 2. 代码,输出信号有R,G,B三色,就是上图右边的,行同步 ...

- 实验三 组合逻辑电路的VHDL设计

一.实验目的 熟悉QuartusⅡ的VHDL文本设计过程,学习简单组合逻辑电路的设计.仿真和测试方法. 二.实验内容 1. 基本命题 完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测 ...

- Verilog-FPGA硬件电路设计之一——if语句优先级(always块中的阻塞赋值生成的组合逻辑电路是按照顺利执行的)

出处:http://bbs.ednchina.com/BLOG_ARTICLE_3013262.HTM 综合软件:Quartus II 一.有优先级的if语句 if..else if.. else i ...

- FPGA学习笔记(五)—— 组合逻辑电路功能的描述

设计方法: 分析真值表规律 两种描述方式: 方式1:用assign描述,用阻塞赋值= 方式2:用always@(*)描述,用非阻塞赋值<= 选择功能的三种描述方式: ...

- 用verilog来描述组合逻辑电路

1,什么是组合逻辑电路? 逻辑电路在任何时刻产生的稳定的输出信号仅仅取决于该时刻的输入信号,而与过去的输入信号无关,即与输入信号作用前的状态无关,这样的电路称为组合逻辑电路. 上图给出了一个典型的数字 ...

- 【VHDL】组合逻辑电路和时序逻辑电路的区别

简单的说,组合电路,没有时钟:时序电路,有时钟. ↓ 也就是说,组合逻辑电路没有记忆功能,而时序电路具有记忆功能. ↓ 在VHDL语言中,不完整条件语句对他们二者的影响分别是什么?组合逻辑中可能生成锁 ...

- 数字电路基础知识——组合逻辑电路(数据选择器MUX、多路复用器)

转自:https://blog.csdn.net/vivid117/article/details/100747939 数字电路基础知识--组合逻辑电路(数据选择器MUX.也即多路复用器)本次介绍数据 ...

- FPGA驱动VGA显示静态图片

一 .前言 本文设计思想采用明德扬至简设计法.VGA是最常见的视频显示接口,时序也较为简单.本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采 ...

- 硕盟SM-H2V1 HDMI转VGA 笔记本台式主机HDMI转VGA显示器转接头

硕盟SM-G2V1 HDMI转VGA高清转换器一款采用优质芯片的HDMI转VGA转换器,快速传输众享1080P的高清画质显示,而且HDMI转VGA高清转换器,采用24k镀金工艺,耐磨.耐腐蚀性强,这 ...

- Ubuntu14.04安装AMD显卡驱动双屏显示器完全解决方案

网上有很多方法,但是针对AMD显卡的方案不多,所以笔者今天想写一篇关于AMD显卡的教程. 首先,进入这个网址下载一些东东:http://support.amd.com/zh-cn/download/d ...

随机推荐

- 李沐动手学深度学习pytorch实践笔记

1.pytorch中的矩阵乘法: 2.标量对向量求导: 3.pytorch的backward函数: 4.如何直观理解梯度下降: 梯度,是个向量,有方向和长度就是向量,向量里的各个元素是偏导.是标量对向 ...

- Java中一个逐渐被遗忘的强大功能,强到你难以置信!!

大家好,我是冰河~~ 说起Java,简单好用,但是Java中很多牛逼的技术却逐渐被遗忘了~~ 在Java语言出现之前,很多系统都是使用C和C++开发的.Java出现之后,由于其面向对象的思想更加符合人 ...

- logback 日志输出配置

application.properties文件中 logging.config=classpath:logback-spring-dev.xml logback-spring-dev.xml &l ...

- FPGA之PLD的简单设计

FPGA之PLD的简单设计 1.实验原理 PLD是可编程逻辑器件的简称,是FPGA的前身(FPGA是在PLD的基础上发展出来的).从PLD设计可以感受早期可编程逻辑器件的特点,了解FPGA在器件层的原 ...

- C++设计模式 - 桥模式(Bridge)

单一职责模式: 在软件组件的设计中,如果责任划分的不清晰,使用继承得到的结果往往是随着需求的变化,子类急剧膨胀,同时充斥着重复代码,这时候的关键是划清责任. 典型模式 Decorator Bridge ...

- OpenHarmony创新赛|赋能直播第四期

开放原子开源大赛OpenHarmony创新赛进入了中期评审环节,为了解决开发者痛点,本期以三方库移植.MQTT移植案例.开发工具介绍的3节系列技术课程,帮助开发者提升开发效率,为作品的创新能力奠定坚 ...

- OpenHarmony AI框架开发指导

一.概述 1.功能简介 AI 业务子系统是 OpenHarmony 提供原生的分布式 AI 能力的子系统.AI 业务子系统提供了统一的 AI 引擎框架,实现算法能力快速插件化集成. AI 引擎框架主要 ...

- SQL 通配符:用于模糊搜索和匹配的 SQL 关键技巧

SQL通配符字符 通配符字符用于替代字符串中的一个或多个字符.通配符字符与LIKE运算符一起使用.LIKE运算符用于在WHERE子句中搜索列中的指定模式. 示例 返回所有以字母 'a' 开头的客户: ...

- Python 中的字符串基础与应用

在Python中,字符串可以用单引号或双引号括起来.'hello' 与 "hello" 是相同的.您可以使用print()函数显示字符串文字: 示例: print("He ...

- 使用IDEA直接连接数据库报错:Server returns invalid timezone. Go to 'Advanced' tab and set 'serverTimezone' property manually.

错误详情:使用IDEA直接连接数据库报错:Server returns invalid timezone. Go to 'Advanced' tab and set 'serverTimezone' ...