【Loongson】支持AXI总线接口

概述

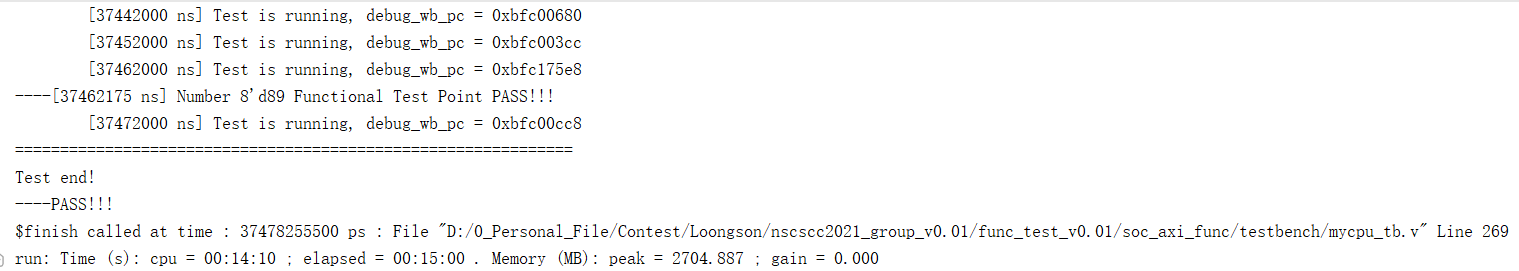

支持axi接口。但其实没有burst,没有cache,没有tlb,所以仿真起来全是空泡,冲突转发相关功能正确性就测不出来。

从sram改为axi:等待时间从一拍到看信号握手

主要更改/bug处:

- 访存指令(取指令/存取ram)自身

- 跳转指令和访存指令

- 异常处理跳出

- 异常处理跳回

- 异常和访存指令

Bug_Log

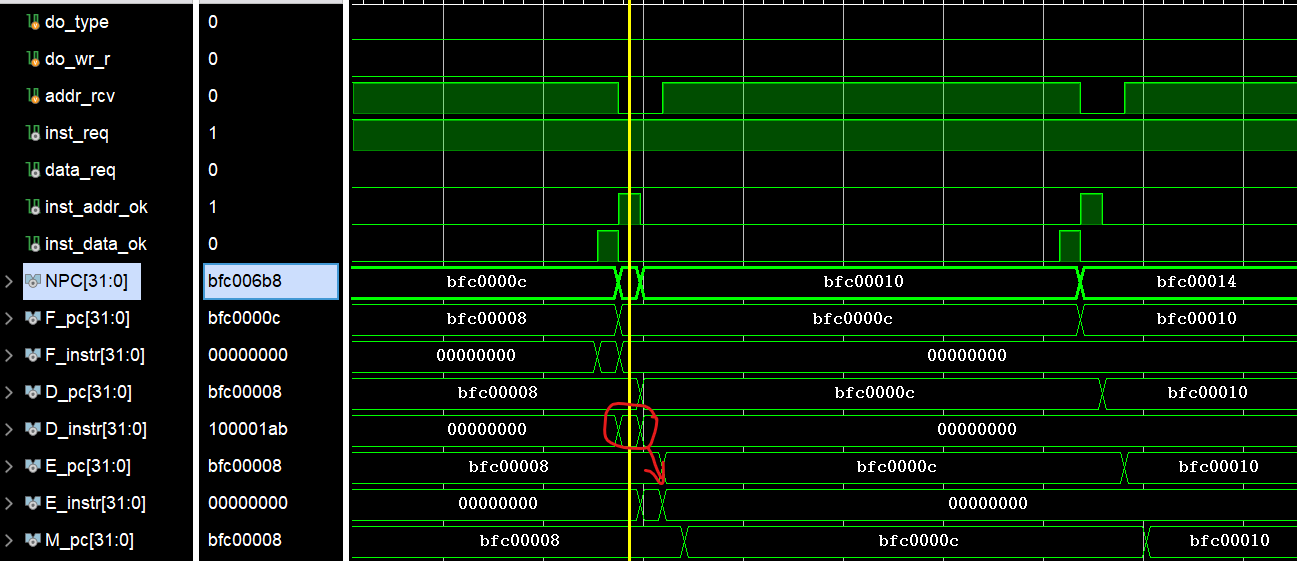

1.D级跳转指令未起作用便向下流水

F级等待raddr指令数据时,将PC的写使能禁了,因而此时D级跳转指令无法生效;因为疏忽将D级及以后继续流水,导致跳转指令失去效益,跳转失败。

核心问题:一条指令流向下一级的必要条件是,在当前流水级完成了自己的使命。

感觉随着以后各种延迟等待的加入,以及指令功能的复杂度增加,使用各种顶层信号控制流水线的各级阻塞/运转会越来越麻烦。或许每一级之间是否流水也弄一个握手信号会方便?

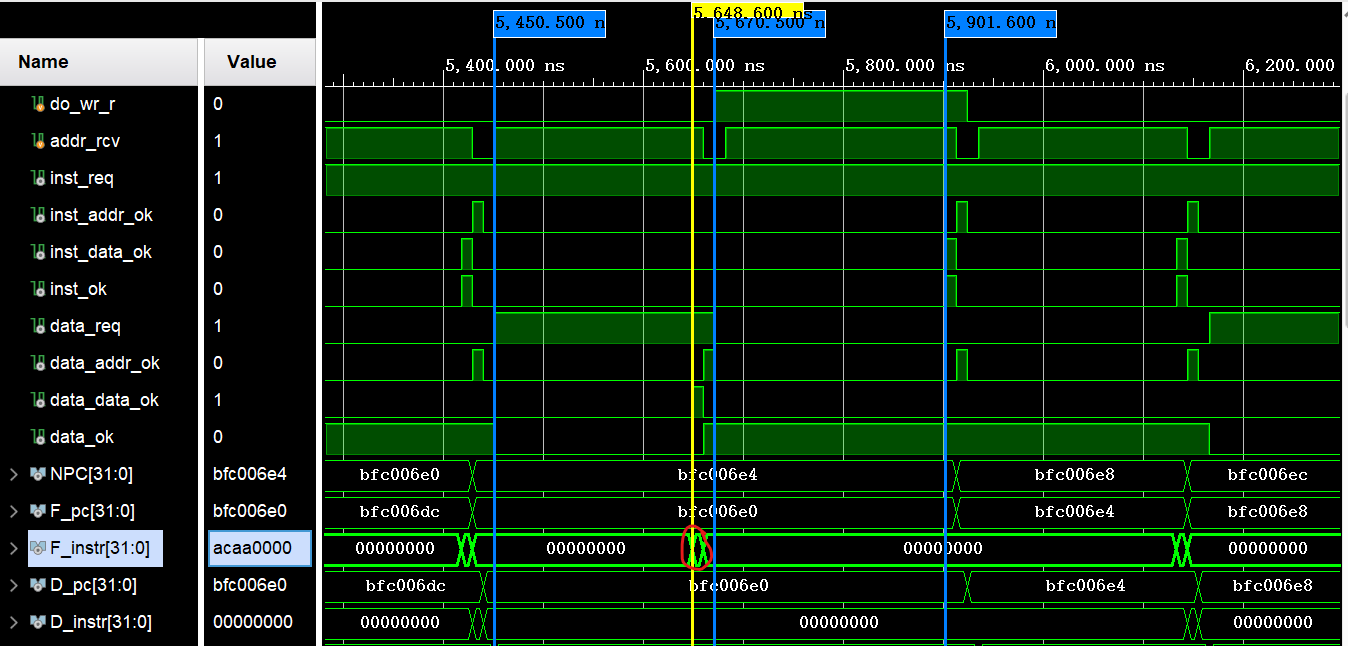

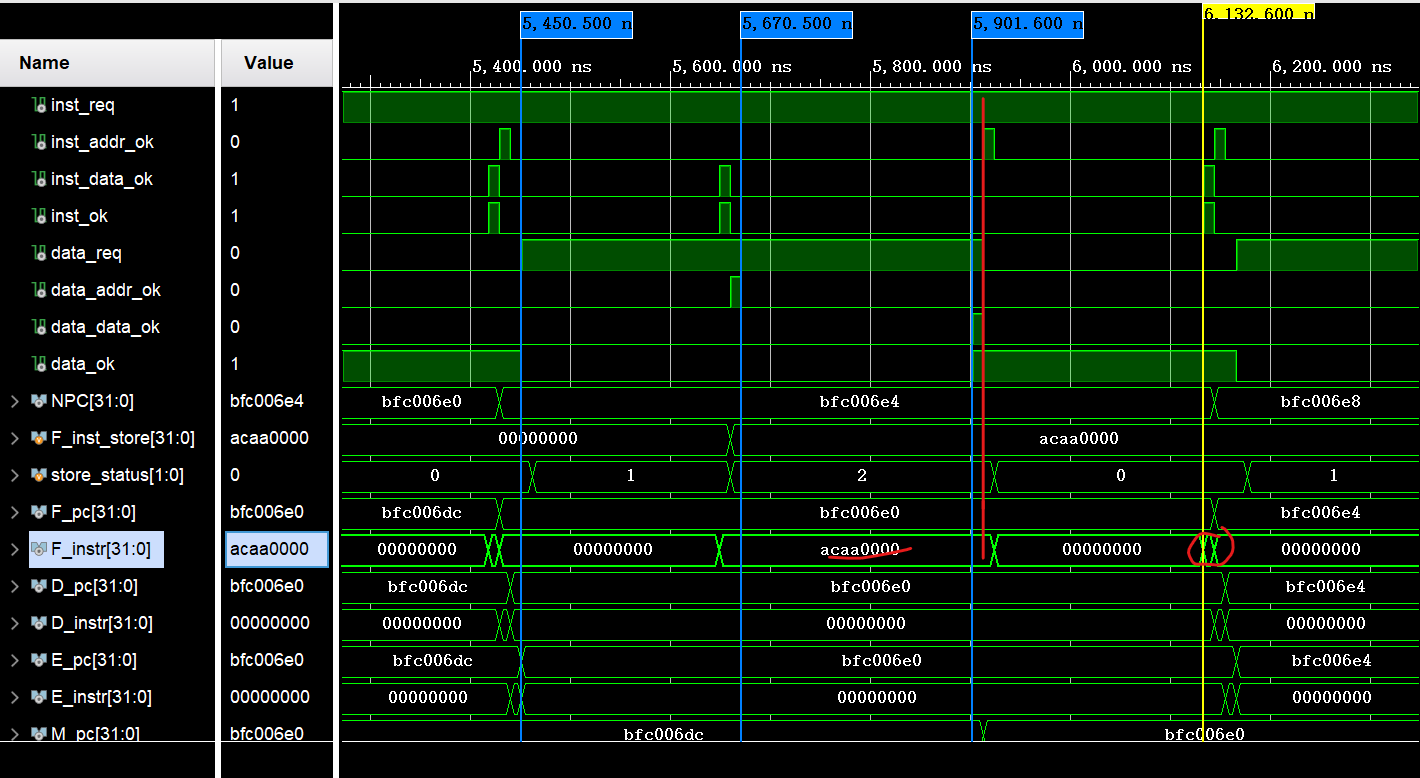

2.访存指令时流水线暂停导致F级漏过axi读通道返回的inst指令

F_instr采用wire类型直接接收rdata而无法存储。

当M级发现store/load指令时发出data_req指令,M级前的流水线暂停(写使能置零),但此时F_pc的读指令请求已然发出。若指令返回时data_req未结束,则因为流水线的暂停导致获取的指令无法被存入D级而丢失。

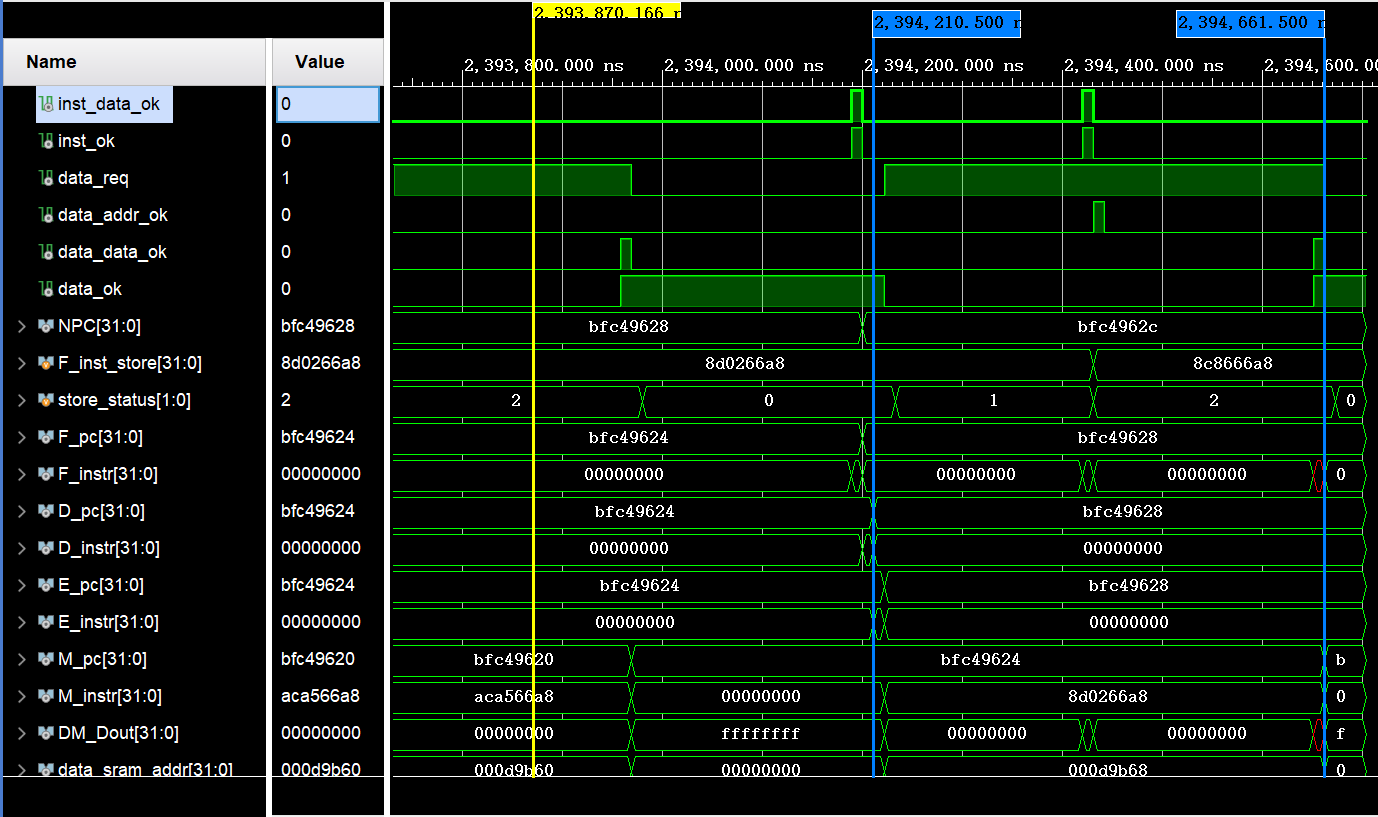

打圈处指令丢失;同时三条蓝线标记分别表示:data_req开始(M检测到store/load指令)、data_req结束(store指令存完/load指令返回)、下一个inst_ok到来(bvalid和bready握手,之后PC可以在下一个上升沿更新)

其实根本不需要。这是多个错误杂糅后显现出的表象

个人的F级只有在inst_data_ok时才会往后流水,所以data_req后并不会动,ar会继续发送相同的PC值,所以指令丢失了没关系。

3.误将data_addr_ok当作store指令完成的标志

借用了类SRAM接口中定义的addr_ok,结果看错了,以为store和load指令处理完毕的信号情况是不一样的。其实都是以bvalid和bready是否握手作为判据之一的。

4.整个wdata信号忘记传值了!

太离谱了,直接忘记了写信号,直到0xbfc4_9628处lw指令才发现。

先是从访问ram中值得到XXXXXXXX,百思不得其解啊,前面也有好多lw没问题的;然后对比了下,前面的访存是取1faf_xxxx中的值(也就是外设),而此处是000d_9b68即ram中的值。

比对确认地址有效后,开始看axi各信号的具体情况;(原先指加了几个握手信号)然后发现wdata一直是ZZZZZZZZ,才惊觉忘传信号。。。

这里察觉到,使用soc_lite.v中的信号最佳,cpu_xxx即为本cpu的axi信号,conf_xxx和ram_xxx分别是外设和ram中的axi信号,很清楚。

5.与异常时的跳转不适配

Req相关机制和axi的运作没有适配。

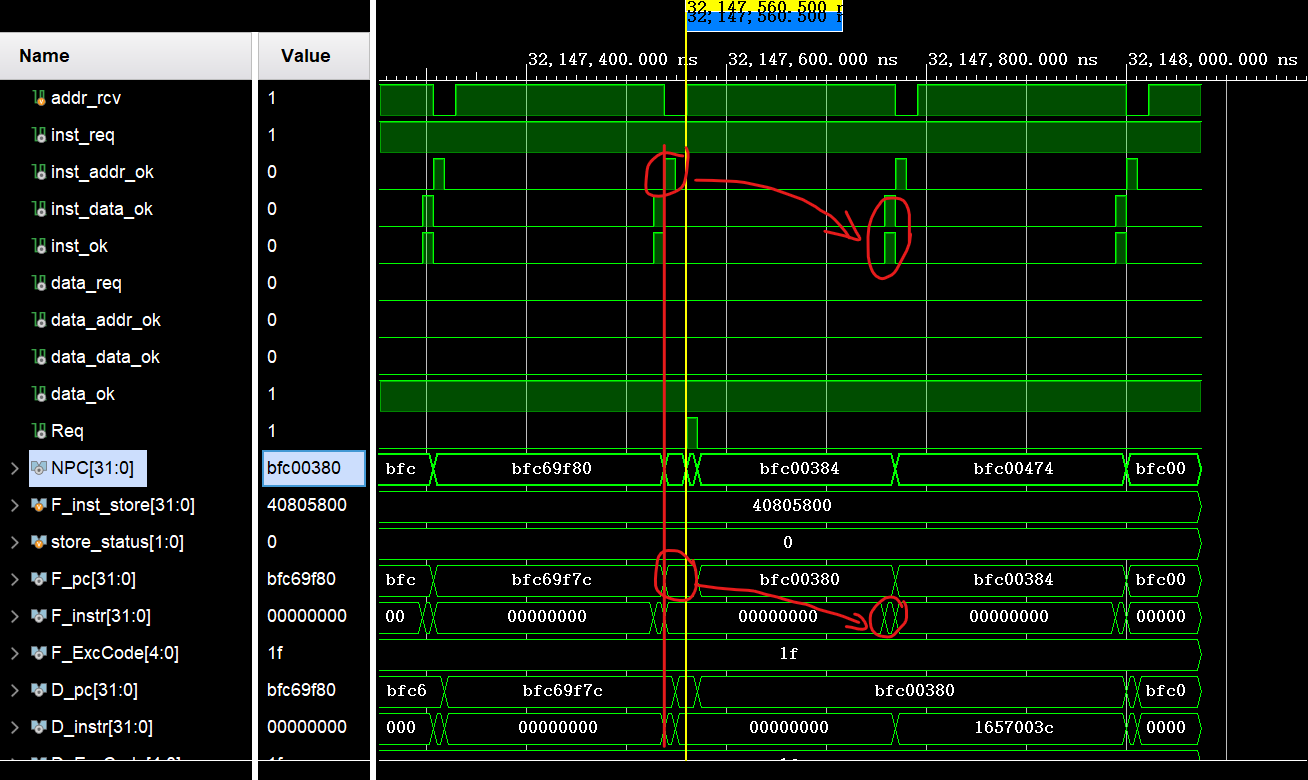

当M级检测到异常指令(PC=bfc6_9f7c)想要跳转时,当前axi接口ar读指令(PC=bfc6_9f80)请求已发出,正在等待返回;若直接跳转到bfc0_0380处,则当bfc6_9f80的指令信息返回时,会被CPU误以为是bfc0_0380的指令而流水,导致:多执行了异常后指令,少执行异常处理首指令。

修正:

源头来自于ar发出的指令覆水难收,于是最直接的想法就是暂停流水级。M级检测到异常必然晚于F级取指的指令发出,因而当Req为1时,暂停M级及之前的流水级,等待rdata正确传回指令(inst_ok)时,启动异常处理跳转的相关机制。

修改时,又注意到CP0设计时Req输出信号的性质:

// In "CP0.v"

assign IntReq = ( (|(HWInt & `IM72)) || (|(`IP10 & `IM10)) || `TI) && ~`EXL && `IE; //soft cannot write IP72

assign ExtReq = (ExcCodeIn != `Exc_Null) && ~`EXL; // exception exit & idle

assign Req = IntReq | ExtReq;

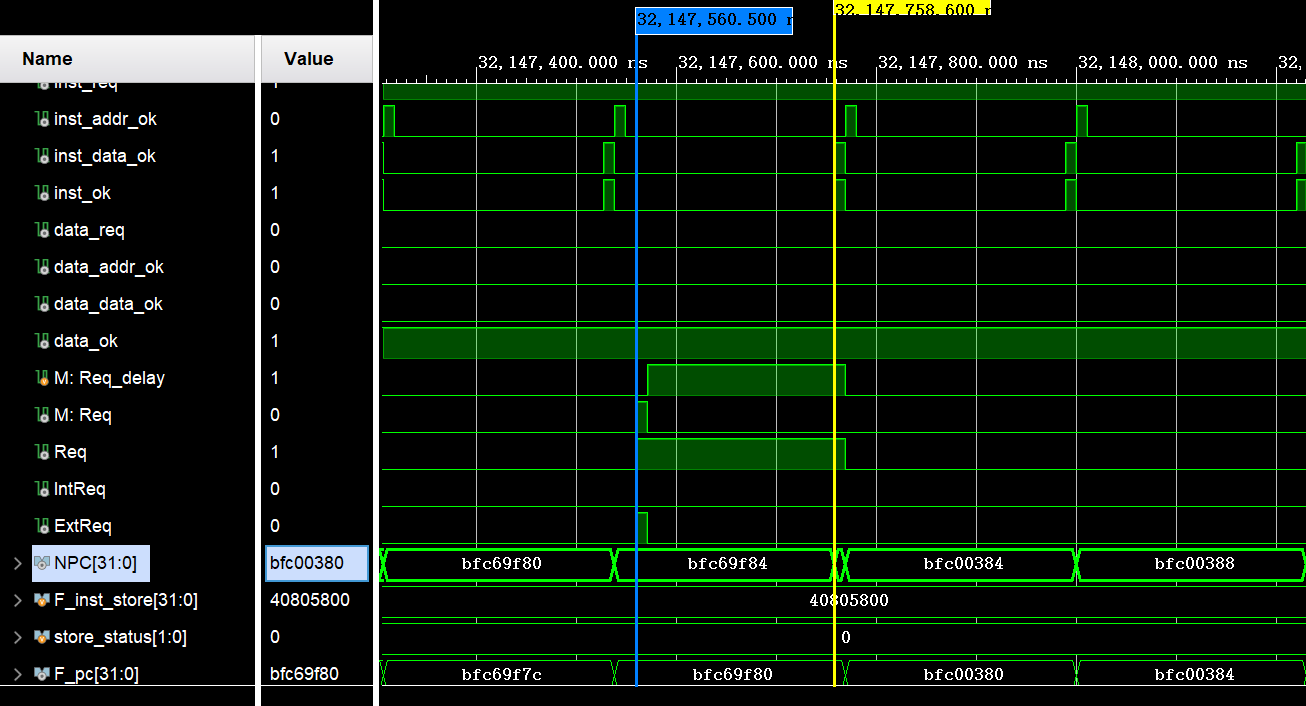

而当Req为1时,下一拍`EXL“异常级”位会被置1:也即CP0模块的Req信号只会存在一拍。考量到耦合度问题,不应该为了axi接口修改CP0模块内部实现;于是在M_LEVEL模块增设reg Req_delay信号,并传出ReqOut = Req | Req_delay来实现Req信号对外的延迟。

reg Req_delay; // for inst_ok

always @(posedge Clk) begin

if (Rst == 1) begin

Req_delay <= 0;

end else begin

if (Req == 1) begin

Req_delay <= 1;

end else if (inst_ok) begin

Req_delay <= 0;

end

end

end

assign ReqOut = Req | Req_delay;

6.与异常处理结束eret跳转不适配

由于跳转延迟槽的存在而eret不设置延迟槽,D级解码出eret指令后,需将下一次延迟槽传来的指令清空。因为axi的缘故,只有inst_ok时才会流水,所以清空延迟槽的操作要等到那时候才行。

关于Clr信号的冗余设置:

所谓清空延迟槽,不过是将应该传入D级的前一级流水pc/inst信号清空,这和Wait信号对本流水级(D)的行为相同,不同处在于,此时D级写使能为1,Wait信号时,写使能为0.

顶层控制流水级寄存器的信号已经过于紊乱了,相关接口开得意义不明!

要对流水级/寄存器的行为进行整合(这些行为不过就是各流水级Rst和En的排列组合);顶层信号代表总体排列的含义,传入流水级后自行操纵寄存器。

7.异常信号与data_ok的冲突

当异常与访存相关时,如“地址错异常”,data_ok会影响PC_en的改变。

若Req(及其延迟信号)结束时,data_ok尚未置1(load/store指令发出的ar/aw信号为被处理),则此时PC_en不会回到1,下一刻NPC的bfc0_0380将会丢失。

解决:

// Former

wire PC_en = !stall & inst_ok & data_ok;

// Current

wire PC_en = !stall & inst_ok & (data_ok | Req);

其他各级流水的en也存在这种情况,但由于传入了Req信号会设空泡并改PC为bfc0_0380,所以暂停也无妨;至于load/store指令的错误影响已处理无需担心。

【Loongson】支持AXI总线接口的更多相关文章

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

- 自我生啃 AMBA AXI 总线笔记

视频1:https://www.youtube.com/watch?v=1zw1HBsjDH8&list=PLkqJVNOiuuHtNrVaNK4O1BSgczja4obeW (What is ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- Zynq-PL中创建AXI Master接口IP及AXI4-Lite总线主从读写时序测试(转)

转载:原文 http://www.eefocus.com/antaur/blog/17-08/423751_6cc0d.html 0. 引言 通过之前的学习,可以在PL端创建从机模式的AXI接口IP ...

- zedboard如何从PL端控制DDR读写(二)——AXI总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的. AXI(Ad ...

- AXI总线

AXI(Advanced eXtensible Interface)是一种总协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture) ...

- zynq里面的AXI总线(2017-1-11)

在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议.其中三种AXI总线分别为: AXI4:(For high-performance memory-mapped requir ...

- AXI总线(转)

AXI(Advanced eXtensible Interface)是一种总协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture) ...

- AXI总线协议

AXI总线协议 (一).概述 AXI (高性能扩展总线接口,Advanced eXtensible Interface)是ARM AMBA 单片机总线系列中的一个协议,是计划用于高性能.高主频的系统设 ...

- 利用ZYNQ SOC快速打开算法验证通路(6)——利用AXI总线实时配置sysGen子系统

利用ZYNQ验证算法的一大优势在于,可以在上位机发送指令借助CPU的控制能力和C语言易开发特点,实时配置算法模块的工作模式.参数等对来对其算法模块性能进行全面的评估.最重要的是无需重新综合硬件模块. ...

随机推荐

- React 应用的 Nginx 缓存控制

典型 React 应用面临的缓存问题,可通过 Nginx 配置进行解决 通用部署 构建应用后,只需使用 Nginx 指向静态文件即可 server { listen 80; root /PATH/TO ...

- 零基础IM开发入门(三):什么是IM系统的可靠性?

本文编写时引用了"聊聊IM系统的即时性和可靠性"一文的部分内容和图片,感谢原作者. 1.引言 上一篇<零基础IM开发入门(二):什么是IM系统的实时性?>讲到了IM系统 ...

- 快速上手jquery

优点 强大的选择器机制 优质的隐私迭代 链式编程 选择机制 选择器 标签名 $('div') id $('#id') class $('.clname') 属性 $('div:[name='66']' ...

- 第六章 dubbo源码解析目录

13.1 dubbo服务降级源码解析 从 9.1 客户端发起请求源码 的客户端请求总体流程图中,截取部分如下: //代理发出请求 proxy0.sayHello(String paramString) ...

- 将github个人访问令牌与TortoiseSVN一起使用

最近用TortoiseSVN提交到Github身份验证,总是提示无效的用户名密码,反复确认密码没输入错的.但是就是提交不了(能获取). 报错如下: 错误: No more credentials or ...

- Access pg walkthrough Intermediate window域渗透

namp nmap -p- -A -sS -T4 192.168.200.187 Starting Nmap 7.94SVN ( https://nmap.org ) at 2024-12-23 00 ...

- 天翼云VPC支持专线健康检查介绍

本文分享自天翼云开发者社区<天翼云VPC支持专线健康检查介绍>,作者:汪****波 天翼云支持本地数据中心IDC(Internet Data Center)通过冗余专线连接到天翼云云上专有 ...

- Django项目实战:配置 setting.py

Django项目实战:配置 setting.py Django项目的配置主要通过settings.py文件完成.这个文件位于项目的根目录下(与manage.py同级).为了让你的应用更加本地化,你可能 ...

- 快速 log2 取整算法 (O(1) 时间与空间复杂度)

先上核心代码(文末附针对多种整数类型的代码): inline int log_2(int x) { int rst = 0; if (x & 0xffff'0000U) rst += 16, ...

- JavaDoc文档的介绍及生成方法

javaDoc命令是用来生成自己的API文档的 参数信息 @author 作者名 @version 版本号 @since 指明需要最早使用的jdk版本 @param 参数名 @return 返回值情况 ...