关于Verilog 中的for语句的探讨

在C语言中,经常用到for循环语句,但在硬件描述语言中for语句的使用较C语言等软件描述语言有较大的区别。

在Verilog中除了在Testbench(仿真测试激励)中使用for循环语句外,在Testbench中for语句在生成激励信号等方面使用较普遍,但在RTL级编码中却很少使用for循环语句。主要原因就是for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,每条执行语句并不能有效地复用硬件逻辑资源,造成巨大的资源浪费。简单的说就是:for语句循环几次,就是将相同的电路复制几次,因此循环次数越多,占用面积越大,综合就越慢。

在RTL硬件描述中,遇到类似的算法,推荐的方法是先搞清楚设计的时序要求,做一个reg型计数器。在每个时钟沿累加,并在每个时钟沿判断计数器情况,做相应的处理,能复用的处理模块尽量复用,即使所有的操作不能复用,也采用case语句展开处理。

对于下面的for循环语句:

for(i=;i<;i++)

DoSomething();

可以采用如下代码实现:

reg [:] counter;

always @(posedge clk)

if(syn_rst)

counter<='b0;

else

counter<=counter+;

always @(posedge clk)

begin

case(counter)

'b0000:

'b0001:

......

default:

endcase

end

另外,有几个语法的细节需要注意一下。for(i=0;i<16;i=i+1)中的i既可以是reg型的变量也可以是integer类型的变量,但是当i是reg型的变量时,需要注意因为判断语句i<16的缘故,i应定义为reg[4:0] i而不是reg[3:0] i 。由于verilog中没有自增运算符,文中提到的for语句不能写成for(i=0;i<16; i++)的形式。 下面简单的列举几个用for实现的程序代码:

示例一:

仿真结果如下:

//Leftshift for 4 bits

module For_Leftshift(

input wire [:]inp,

input wire L_EN,

output reg [:]result

); integer i;

always@(inp or L_EN)

begin

result[:] = ;

result[:] = inp;

if(L_EN == )

begin

for(i=;i<=;i=i+)

begin

result[i] = result[i-];

end

result[:] = ;

end

end endmodule

综合结果(RTL视图,实际是一个4位选择器)

示例三:for不仅可以用在组合逻辑中,而且还可以用在时序逻辑中,用于在1个周期类完成整个for循环。

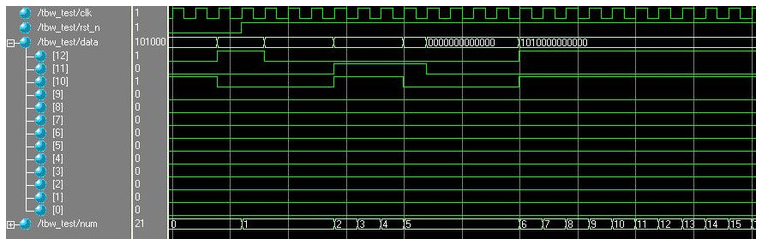

module For_Counter(

input wire clk,

input wire rst_n,

input wire [:] data,

output wire [:] numout

);

integer i;

reg[:] num; always @(posedge clk)

begin

if(!rst_n)

num = ;

else

begin

for(i=;i<;i=i+)

if(data[i]) num = num + ;

end

end assign numout = num; endmodule

综合结果(RTL视图,加法器+触发器)

关于Verilog 中的for语句的探讨的更多相关文章

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 总结Verilog中always语句的使用

always语句包括的所有行为语句构成了一个always语句块.该always语句块从仿真0时刻开始执行其中的行为语句:最后一条执行完成后,再开始执行其中的第一条语句,如此往复循环,直到整个仿真结束. ...

- verilog中初值定义

在利用verilog进行开发时,往往需要对某些寄存器进行赋初值,下面根据笔者在设计中遇到的情况进行分析. 例如下面是实现流水灯(4个led),代码如下: module ledrun ( input ...

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- Verilog中的$display和$write任务

$display(p1,p2, …,pn); $write(p1,p2, …,pn); 这两个函数和系统任务的作用都是用来输出信息,即将参数p2到pn按参数p1给定的格式输出.参数p1通常称为:“格式 ...

- Verilog中的阻塞与非阻塞

这篇文档值得阅读 按说阻塞与非阻塞是Verilog中最基本的东西,也是老生常谈.但是最近看到很多程序里用到阻塞语句竟然不是很明白,说到底是从来没有自己仔细分析过.当然一般情况程序中也是推荐用非阻塞的. ...

- 关于Verilog中的几种赋值语句

1. 连续赋值语句(Continuous Assignments) 连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,是从更高的抽象角度来对电路进行描述.连续赋值语 ...

随机推荐

- ecshop获取url_domain

<?php function url_domain() { $curr = strpos($_SERVER['PHP_SELF'], '/') !== false ? preg_replace( ...

- cocos2d-x3.0 ListView

.h #include "cocos2d.h" #include "cocos-ext.h" #include "ui/CocosGUI.h" ...

- 基于XMPP实现的Openfire的配置安装+Android客户端的实现

最近在整理一些这方面的资料,闲话少说,咱还是直奔主题吧 :) 一.基于xmpp实现的openfire的配置安装 1. 下载最新的openfire安装文件 官方下载站点: http://www.igni ...

- [Angular 2] 9. Replace ng-modle with #ref & events

Let's say you want to write a simple data bing app. when you type in a text box, somewhere in the ap ...

- Xcode常见报错及解决办法

报错一: 在iOS7的真机运行时,弹出错误:App installation failed. There was an internal API error. 如图 解决办法: 在Xcode -> ...

- codevs 1519 过路费 最小生成树+倍增

/*codevs 1519 过路费 最小生成树+倍增*/ #include<iostream> #include<cstdio> #include<cstring> ...

- JavaScript正则验证数字、英文、电话号、身份证号、邮箱地址、链接地址等

验证是否为数字:/^[0-9]*$/验证是否为汉字:/^[\u4e00-\u9fa5],{0,}$/验证x-y位的数字:/^\d{x,y}$/验证由26个英文字母组成的字符串:/^[A-Za-z]+$ ...

- Nginx配置同一个域名http与https两种方式都可访问

##配置 http://test.pay.joyhj.com https://test.pay.joyhj.com 两者都可访问 # vim /usr/local/nginx/conf/vhost/t ...

- OC中的SEL解析

OC中的SEL对象即selector对象,用来保存一个方法的地址.下面通过一个Demo来解析SEL的原理.创建一个Person类,Person.h中: #import <Foundation/F ...

- CSS布局模型思考

flow模型:默认布局模型,元素从左向右.从上到下依次排列,块状元素独占一行.Position属性对应值static. float模型:主要效果是让本来独占一行的块状元素变成内联-块状元素,并到一排显 ...