fpga基础

1.FPGA 的分类:

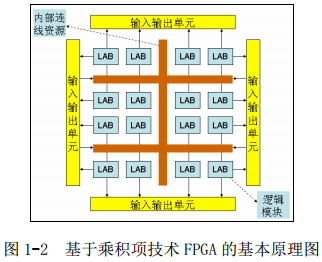

根据 FPGA 基本结构,可将其分为基于乘积项(Product-Term)技术的 FPGA 和基于查找表(Look-Up-Table)技术的 FPGA 两种。

(1)基于乘积项技术的 FPGA 主要由 3 个模块组成:逻辑单元阵列(Logic Cell Array)、可编程连线(PIA)和 I/O 控制块。

- 逻辑单元阵列:是 FPGA 的基本结构,由它来实现基本的逻辑功能。

- 可编程连线: 负责信号传递,连接所有的宏单元。

- I/O 控制块: 负责输入/输出的电气特性控制。

(2)查找表简称为 LUT,其本质就是一个RAM。目前 FPGA 中多使用 4 输入的 LUT,所以每一个 LUT 可以看成一个有 4 位地址线的 16×1的 RAM。

- LUT抽象描述:当用户通过原理图或 HDL 语言描述了一个逻辑电路以后,FPGA 开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入 RAM,这样每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

- LUT缺陷:由于 SRAM 工艺的特点,掉电后数据会消失,因此调试期间可以通过电缆配置 FPGA 器件,调试完成后,需要将数据固化在一个专用的 EEPROM 中(用通用编程器烧写),上电时由这片 EEPROM 对 FPGA 加载数据,十几个毫秒后 FPGA 即可正常工作(亦可由 CPU 配置 FPGA)。此类型的 FPGA 一般不可以进行程序加密。

2.下载可执行程序:

在完成 FPGA 开发以后,软件会生成一个最终的编程文件,不同类型的 FPGA 使用不同的方法将编程文件加载到 FPGA 中。

- 基于乘积项(Product-Term)技术的 FPGA 一般采用 EEPROM(或 Flash)保存程序。

- 基于查找表技术(Look-Up table)技术常使用 SRAM 保存程序。

- 除了上述的两种 FPGA 外,还有一种反熔丝(Anti-fuse)技术的 FPGA

3.FPGA器件叫法:

- XILINX 把基于查找表技术、使用SRAM 工艺、要外挂配置用 EEPROM 的 PLD 叫 FPGA;

- ALTERA 把自己的 PLD 产品 MAX 系列(乘积项技术,EEPROM 工艺)、FLEX 系列(查找表技术,SRAM 工艺)都叫作 CPLD,即复杂 PLD(Complex PLD);但由于 FLEX 系列也是 SRAM工艺、基于查找表技术、要外挂配置用的 EPROM,用法和 XILINX 的 FPGA 一样,所以很多人把ALTERA 的 FELX 系列产品也叫做 FPGA。

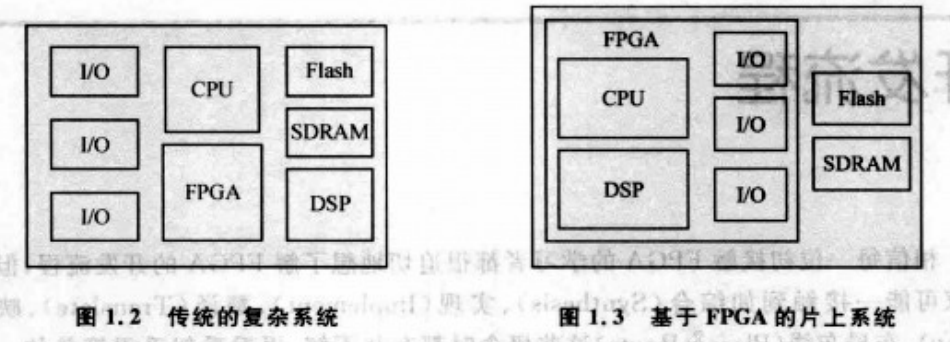

4.片上系统概念:

指单个芯片上集成一个完整的系统,一般包括:系统级芯片控制逻辑模块、微处理器/微控制器内核模块、数字信号处理器模块、存储器或存储器控制控制模块、与外部通信的各种接口协议模块、含有ADC/DAC的模拟前端模块、电源及功耗管理模块。

5.fpga开发细节:

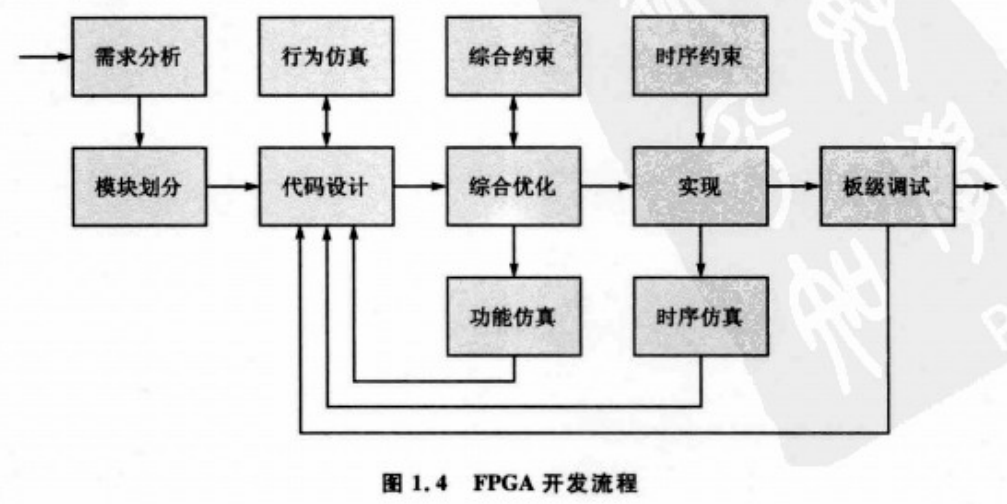

需求分析、模块划分、设计输入、语法检查、综合、功能仿真、全编译、时序约束、实现(翻译、映射、布局布线)、仿真和板级调式。

- 需求分析:器件选型、逻辑资源大小选择、I/O个数考虑、信号电平和系统功耗要求、存储器大小、内嵌功能模块考虑。

- 模块划分:划分的最基本原则是以功能划分为主,有时也按着数据流(并行或顺序)来划分。(主要是在项目分配工作阶段)。

- 设计输入:包括原理图输入、代码输入、搭建SOPC平台。

- 综合:指较高层次的电路描述转化为较低层次的电路描述。具体的说,就是将代码设计(代码输入)转化为底层的与门、非门、RAM触发器等基本逻辑单元相互连接而成的网表。

- 时序约束:工程全局约束---->I/O时序约束------>指定约束。

- 仿真:行为仿真(设计输入完成阶段后进行)、功能仿真(综合优化阶段结束后进行)、时序仿真(实现阶段进行)。

- 板级调试:下载配置完成后进行。

6.fpga开发过程:

(1)利用硬件描述语言(HDL)从上层到下层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表是极其复杂的数字系统。

(2)然后利用电子设计自动化(EDA)工具逐层进行仿真验证,再把其中需要变为具体物理电路的模块组合经由自动综合工具转换到门极电路网表。

(3)接下去再用专用集成电路(ASIC)或现场可编程门阵列(fpga)自动布局布线工具把网表转换为具体电路布线结构的实现。

注意:在制成物理器件之前,具体基本元件可用 verilog 的门极模型(原语元件或 UDP)来代替..

7.Verilog HDL和·VHDL:

均是硬件描述语言(HDL)的一种。

fpga基础的更多相关文章

- FPGA基础知识了解

FPGA学习的一些误区 FPGA入门必看资源 FPGA百度百科 FPGA基础知识及其工作原理 高端设计工具为少有甚是没有硬件设计技术的工程师和科学家提供现场可编程门阵列(FPGA).无论你使用图形化设 ...

- FPGA基础设计(四):IIC协议

很多数字传感器.数字控制的芯片(DDS.串行ADC.串行DAC)都是通过IIC总线来和控制器通信的.不过IIC协议仍然是一种慢速的通信方式,标准IIC速率为100kbit/s,快速模式速率为400kb ...

- FPGA基础入门篇(四) 边沿检测电路

FPGA基础入门篇(四)--边沿检测电路 一.边沿检测 边沿检测,就是检测输入信号,或者FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测.在检测到所需要的边沿后产生一个高电平的脉冲.这在FPGA电 ...

- FPGA基础知识关键点摘要

FPGA基础知识关键点摘要 一.组合逻辑和时序逻辑的区别:组合逻辑与输入直接实时相关,时序逻辑还必须在时钟上升沿出发后输出新值,有没有时钟输入是他们最大的区别!组合时序容易出现竞争冒险现象出现亚稳态, ...

- FPGA基础学习(7) -- 内部结构之CLB

目录 1. 总览 2. 可配置逻辑单元 2.1 6输入查找表(LUT6) 2.2 选择器(MUX) 2.3 进位链(Carry Chain) 2.4 触发器(Flip-Flop) 参考文献: 一直以来 ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA基础架构总结

1.为什么FPGA的整体逻辑的速度有限制? 与ASIC相比较,AS指的是(application specific)专用集成应用,而FPGA是可编程逻辑,在实现的过程中,AS是直接用最基础的逻辑门实现 ...

- 我的 FPGA 学习历程(01)—— FPGA 基础知识和 Quartus 的安装

高级的嵌入式市场主要分为以下三类:ARM.DSP 和 FPGA. 其中 ARM 是行业内的佼佼者,目前几乎所有的安卓智能手机都使用 ARM 授权的 CPU架构:而 DSP(数字信号处理器) 早年就被大 ...

- FPGA基础之逻辑单元(LE or LC)的基本结构

原帖地址: https://blog.csdn.net/a8039974/article/details/51706906/ 逻辑单元在FPGA器件内部,是完成用户逻辑的最小单元.逻辑单元在ALTER ...

- FPGA基础知识1

1.乘法 在FPGA中,乘法运算可以分为 1)信号与信号之间的运算,用乘法器核实现: 2)常数与信号之间的运算,利用移位及加减法实现. A x 16 = A左移4位: A x 20 = A x 16 ...

随机推荐

- STP生成树算法

生成树算法第一:决定谁是“根网桥”对比各个网桥ID,先对比ID中的优先级,优先级相同的时候对比网桥MAC地址,对比依据是谁的值最小,谁是“根网桥” 第二:决定哪些是“根端口”窍门——每个非根网桥上都有 ...

- Shell登陆远程服务器

现场服务器较多,密码3个月过期,在到期时需更改密码. 使用expect编写,尝试登陆2次后退出(防止密码错误时账号锁定),超时重试一次. shell脚本调用并定时执行,登陆成功后执行一条命令,如:ho ...

- 深度学习面试题27:非对称卷积(Asymmetric Convolutions)

目录 产生背景 举例 参考资料 产生背景 之前在深度学习面试题16:小卷积核级联卷积VS大卷积核卷积中介绍过小卷积核的三个优势: ①整合了三个非线性激活层,代替单一非线性激活层,增加了判别能力. ②减 ...

- Java查询目录下的所有文件(包括子目录)

目录图: 方法代码: /** * 读取目录下的所有文件 * * @param dir * 目录 * @param fileNames * 保存文件名的集合 * @return */ public st ...

- Jira 入门【转】

JIRA是Atlassian公司出品的项目与事务跟踪工具,被广泛应用于缺陷跟踪.客户服务.需求收集.流程审批.任务跟踪.项目跟踪和敏捷管理等工作领域.它是一个集 项目计划.任务分配.需求管理.错误跟踪 ...

- MQ消息机制如何确认消费了消息?

消息队列如何保证消息能百分百成功被消费 目前常用的消息队列有很多种,如RabbitMQ,ActiveMQ,Kafka...下面以RabbitMQ为例来讲如何保证消息队列中的信息能百分百被消费掉. 其中 ...

- python 设计模式之工厂模式 Factory Pattern (简单工厂模式,工厂方法模式,抽象工厂模式)

十一回了趟老家,十一前工作一大堆忙成了狗,十一回来后又积累了一大堆又 忙成了狗,今天刚好抽了一点空开始写工厂方法模式 我看了<Head First 设计模式>P109--P133 这25页 ...

- Java基础 println 输出常量的示例

JDK :OpenJDK-11 OS :CentOS 7.6.1810 IDE :Eclipse 2019‑03 typesetting :Markdown code ...

- 八、postman的cookie支持

postman中可以直接添加cookie,查看响应中的cookie https://postman-echo.com/cookies/set?foo1=bar1&foo2=bar2 var r ...

- o2s【我】

//预处理对象转String方法 private String o2s(Object o) { if(o!=null&&!"".equals(o)&& ...