Vivado中备份设计好的block design

参考链接

https://blog.csdn.net/dimples_song/article/details/81391615

前言

为了不每次都重新生成block design,避免重复劳动。

可以使用直接复制原始工程的design bd块或者使用tcl脚本生成bd。

流程

- 复制原始工程的bd文件夹。

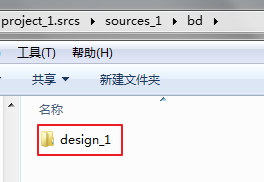

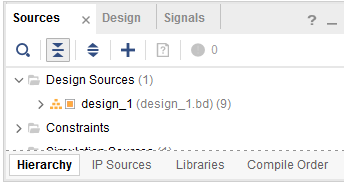

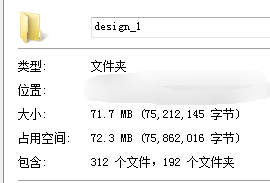

(1)对于原工程生成好的bd文件夹位于如下,复制design_1文件夹。

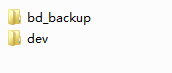

(2)把design_1文件夹放置在新工程的工程文件夹的上一层(或者其他位置),不可放在同一层级(有尾缀为xpr的文件夹),否则导入报错。

如上图所示,放在了bd_backup文件夹中,dev为新工程所在文件夹。

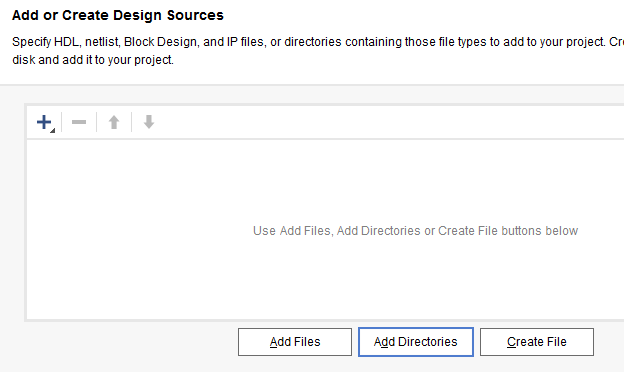

(3)像添加源文件一样,可以直接把design_1文件夹导入即可。

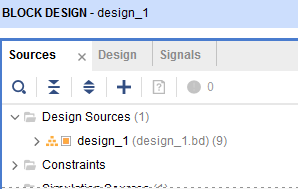

(4)可以看到bd已经导入。

- 使用tcl脚本生成bd。

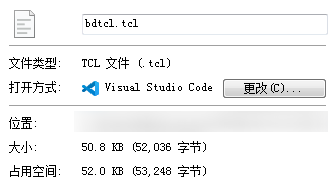

(1)在打开bd设计的前提下,在原工程中tcl控制台导出bd的tcl文件。

write_bd_tcl C:/Users/Administrator/Desktop/test_bd_backup/bdtcl.tcl

(2)复制此tcl文件到任意文件夹下。

在新工程中的tcl控制台中source此文件即可。(如果直接在当前目录下,则可以直接使用下述语句)

source bdtcl.tcl

(3)见证奇迹。可以看到bd文件已经导入。

结论

上述两种都可以备份bd file,当然第一种可能简单一点,但是从文件占用存储空间来考虑,第二种tcl文件所占空间要小得多。

所以,使用哪种根据实际情况选择即可。

以上。

Vivado中备份设计好的block design的更多相关文章

- ZYNQ Block Design中总线位宽的截取与合并操作

前言 在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作. 在verilog下,截位操作可如下所示: wire [7:0] w_in; wire ...

- 使用Vivado的block design

使用Vivado的block design (1)调用ZYNQ7 Processing System (2)配置ZYNQ7系统 (3)外设端口配置 根据开发板原理图MIO48和MIO49配置成了串口通 ...

- ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.

前言 在Block design中引出AXI接口给外部,检查设计告警如下: [BD 41-968] AXI interface port /axi_lite4 is not associated to ...

- Tcl在Vivado中的使用

http://blog.chinaaet.com/detail/36014 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发.与之前的ISE设计套件 ...

- Vivado中debug用法

Vivado和ISE相比ChipScope已经大幅改变,很多人都不习惯.在ISE中称为ChipScope而Vivado中就称为in system debug.下面就介绍Vivado中如何使用debug ...

- 73.Vivado使用误区与进阶——在Vivado中实现ECO功能

关于Tcl在Vivado中的应用文章从Tcl的基本语法和在Vivado中的应用展开,继上篇<用Tcl定制Vivado设计实现流程>介绍了如何扩展甚至是定制FPGA设计实现流程后,引出了一个 ...

- IP核的使用(Vivado中的调用,product guide的查询阅读 ,引脚的设置(位宽,个数,算法等),coe文件的初始化 )

IP核:Intellectual Property core ,即知识产权核.每个IP核可以实现特定功能,我们在设计一个东西时可以直接调用某个IP核来辅助实现功能. 存在形式:HDL语言形式,网表形式 ...

- 自适应网页设计(Responsive Web Design)

引用:http://www.ruanyifeng.com/blog/2012/05/responsive_web_design.html 随着3G的普及,越来越多的人使用手机上网. 移动设备正超过桌面 ...

- 【转】Android的材料设计兼容库(Design Support Library)

转自:http://www.jcodecraeer.com/a/anzhuokaifa/developer/2015/0531/2958.html?mType=Group Android的材料设计兼容 ...

随机推荐

- Single Cell Genomics Day: A Practical Workshop

干货满满! Single Cell Genomics Day: A Practical Workshop

- GSON工具类

import java.util.Map; import com.google.gson.reflect.TypeToken; import com.google.gson.FieldNamingPo ...

- 自定义电脑IP地址

一台电脑有了ip地址才能上网,ip就是电脑的标识,在互联网中就是其中的一份子. 默认情况下电脑会自动获取IP地址,当无法自动获取或与网络IP地址相冲突时,就要自行设置电脑静态IP地址. 如下图步骤:

- springboot-把web项目打成war包部署到外部tomcat

将打包方式修改为war <packaging>war</packaging> 移除tomcat依赖或者将tomcat依赖scope改为provide 移除tomcat依赖 &l ...

- 有些新电脑采用“UEFI”作为固件。由于UEFI不支持DOS,所以在UEFI环境下安装的WIN10等系统也就无法使用基于DOS的一键GHOST

有些新电脑采用“UEFI”作为固件.由于UEFI不支持DOS,所以在UEFI环境下安装的WIN10等系统也就无法使用基于DOS的一键GHOST

- 【VS开发】WaitForSingleObject 和 WaitForMultipleObjects函数 (让线程挂起等待事件)

WaitForSingleObject 和 WaitForMultipleObjects:1.WaitForSingleObject 等待函数可使线程自愿进入等待状态,直到一个特定的内核对象变为已通 ...

- python zip函数(11)

一.zip函数描述和使用 zip() 函数用于将可迭代的对象作为参数,将对象中对应的元素打包成一个个元组,然后返回由这些元组组成的对象,返回的结果可以直接强转为list列表,这样做的好处是节约了不少的 ...

- 小白都能看懂的vue中各种通信传值方式,附带详细代码

1.路由通信传值 路由通信是通过路由跳转用query把参数带过去,也是vue常用的通信手段. 例子: 创建并在路由注册一个组件Head <template> <div id=&quo ...

- LeetCode 611. 有效三角形的个数(Valid Triangle Number)

611. 有效三角形的个数 611. Valid Triangle Number 题目描述 LeetCode LeetCode LeetCode611. Valid Triangle Number中等 ...

- [转帖]Linux中的find(-atime、-ctime、-mtime)指令分析

Linux中的find(-atime.-ctime.-mtime)指令分析 https://www.cnblogs.com/zhangjinjin01/p/5505970.html https://w ...