ZYNQ Block Design中总线位宽的截取与合并操作

前言

在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作。

在verilog下,截位操作可如下所示:

wire [7:0] w_in;

wire [3:0] w_out;

assign w_out = win[3:0];合并操作可如下所示:

wire [3:0] w_in0;

wire [3:0] w_in1;

wire [7:0] w_out;

assign w_out = {w_in1,w_in0};所以问题就来了:如何在不写代码的情况下在block design设计中实现截取与合并的操作呢?

用到的IP

(1)constant IP。

此IP可以输出可配置位宽的常数,电平可配置0或者1。

(2)concat IP。

此IP可以使得分立的线拼接成单一线输出,相当于verilog描述的拼接操作。输入端口数和位宽均可配置。注意In1会放置在高位,[In1,In0]。

(3)slice IP。

此IP功能跟concat IP相反,会把输入截取想要的位宽输出。相当于verilog的位宽截取操作。输入位宽,输出位宽,截取msb和截取lsb都是可以配置的。

实例

100M网口使用MII接口。可以知道数据tx和rx都是4bit位宽的,但在MII IP接口中,数据位宽为8bit。则需截位与合并。

(1)总线位宽合并。

如下图所示,对于100M的网口使用,rx的高4bit需要接0。则需要使用到constant IP和concat IP。

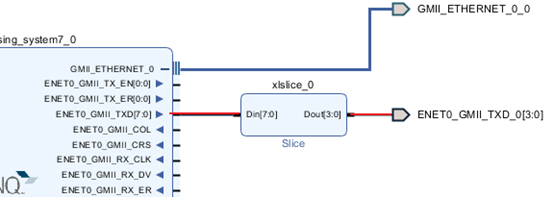

(2)总线位宽截取。

对于100M网口的tx,高位是没用的,则通过slice IP截取低4bit作为输出。

重新生成wrapper,可以看到位宽符合预期,这么做的好处在于无需手动去修改生成的信号位宽,一劳永逸。

以上。

ZYNQ Block Design中总线位宽的截取与合并操作的更多相关文章

- ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.

前言 在Block design中引出AXI接口给外部,检查设计告警如下: [BD 41-968] AXI interface port /axi_lite4 is not associated to ...

- Verilog中变量位宽注意

Verilog中,变量定义方式可以为:reg[位宽-1:0] 数据名:reg[位宽:1] 数据名.其他变量也类似. 以reg变量cnt为例,当cnt位宽为4时,可定义为reg[3:0] cnt,或者定 ...

- C++中输出 位宽和小数点后位数 的控制

要用到这个头文件: <iomanip> setw(x) : 表示控制输出x的位宽 setprecision(x) :表示 控制输出小数点后 x 位 cout.precision(x): 表 ...

- 使用js方法将table表格中指定列指定行中相同内容的单元格进行合并操作。

前言 使用js方法对html中的table表格进行单元格的行列合并操作. 网上执行此操作的实例方法有很多,但根据实际业务的区别,大多不适用. 所以在网上各位大神写的方法的基础上进行了部分修改以适合自己 ...

- s3c2440裸机-内存控制器(二、不同位宽外设与CPU地址总线的连接)

不同位宽设备的连接 black 我们先看一下2440芯片手册上外设rom是如何与CPU地址总线连接的. 8bit rom与CPU地址线的连接 8bit*2 rom与CPU地址线的连接 8bit*4 r ...

- C语言-字、半字、内存位宽相关

1.32位系统:32位系统指的是32位数据线,但是一般地址线也是32位,这个地址线32位决定了内存地址只能有32位二进制,所以逻辑上的大小为2的32次方.内存限制就为4G.实际上32位系统中可用的内存 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 【设计经验】3、ISE中烧录QSPI Flash以及配置mcs文件的加载速度与传输位宽

一.软件与硬件平台 软件平台: 操作系统:Windows 7 64-bit 开发套件:ISE14.7 硬件平台: FPGA型号:XC6SLX45-CSG324 QSPI Flash型号:W25Q128 ...

- Vivado中备份设计好的block design

参考链接 https://blog.csdn.net/dimples_song/article/details/81391615 前言 为了不每次都重新生成block design,避免重复劳动. 可 ...

随机推荐

- 解决win10下MySQL 8.0登录Access denied for user 'root'@'localhost' (using password: YES)的问题

近些时间在开始学MySQL,安装挺顺利的,按照网上现成的教程就能安装成功. 但是,在输入 mysql -uroot -p 再输入密码时,遇到了这个情况 Access denie ...

- redis订阅者与发布者

#conding=utf-8 #一.创建redis类 文件名 RedisHelper import redis # conn=redis.Redis(host='127.0.0.1')# import ...

- 【MySQL】Unknown column 'column_name' in 'field list'

使用 INSERT INTO - SELECT FROM - ON DUPLICATE KEY UPDATE 时遇到了这个问题,百思不得其解

- 【iOS】Xcode 插件安装后无效

今天把 Xcode 升级到 7.3.1,发现插件安装后无效…… 原因:苹果要求加入UUID证书从而保证插件的稳定性. 解决方法: 1. 查看Xcode的UUID 在终端输入以下命令: defaults ...

- Cell Phone Networ (树形dp-最小支配集)

目录 Cell Phone Networ (树形dp-最小支配集) 题意 思路 题解 Cell Phone Networ (树形dp-最小支配集) Farmer John has decided to ...

- ansible批量管理服务 上

1 ansible简介 1.1 ansible批量管理服务概述 (1)是基于python语言开发的自动化软件工具(2)是基于SSH远程管理服务实现远程主机批量管理(3)并行管理,部署简单,应用也简单方 ...

- 夯实Java基础(四)——面向对象之多态

1.多态介绍 面向对象三大特征:封装.继承.多态.多态是Java面向对象最核心,最难以理解的内容.从一定角度来看,封装和继承几乎都是为多态而准备的. 多态就是指程序中定义的引用变量所指向的具体类型和通 ...

- Selenium+java - 借助autolt完成上传文件操作

写在前面: 上传文件是每个自动化测试同学会遇到,而且可以说是面试必考的问题,标准控件我们一般用sendkeys()就能完成上传,但是我们的测试网站的上传控件一般为自己封装的,用传统的上传已经不好用了, ...

- 浅谈单例模式及其java实现

单例模式是23种设计模式中比较简单的一种,在此聊一下单例模式. 1.什么是设计模式? 对于没有接触过设计模式的人来说,一听到设计模式这四个字就觉得这个东西很高深莫测,一下子就对这个东西产生了恐惧感,其 ...

- [Spring cloud 一步步实现广告系统] 20. 系统运行测试

系统运行 经过长时间的编码实现,我们的主体模块已经大致完成,因为之前我们都是零散的对各个微服务自行测试,接下来,我们需要将所有的服务模块进行联调测试,Let's do it. 清除测试数据&测 ...