【转】 VGA时序及其原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一行,完成一屏后再返回来扫描剩下的行,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,75Hz等等。标准的VGA显示的场频60Hz,行频31.5KHz。

行场消隐信号:是针对老式显像管的成像扫描电路而言的。电子枪所发出的电子束从屏幕的左上角开始向右扫描,一行扫完需将电子束从右边移回到左边以便扫描第二行。在移动期间就必须有一个信号加到电路上,使得电子束不能发出。不然这个回扫线会破坏屏幕图像的。这个阻止回扫线产生的信号就叫作消隐信号,场信号的消隐也是一个道理。

显示带宽:带宽指的显示器可以处理的频率范围。如果是60Hz刷新频率的VGA,其带宽达640x480x60=18.4MHz,70Hz的刷新频率1024x768分辨率的SVGA,其带宽达1024x768x70=55.1MHz。

时钟频率:以640x480@59.94Hz(60Hz)为例,每场对应525个行周期(525=10+2+480+33),其中480为显示行。每场有场同步信号,该脉冲宽度为2个行周期的负脉冲,每显示行包括800点时钟,其中640点为有效显示区,每一行有一个行同步信号,该脉冲宽度为96个点时钟。由此可知:行频为525*59.94=31469Hz,需要点时钟频率:525*800*59.94约25MHz.

VGA时序分析:

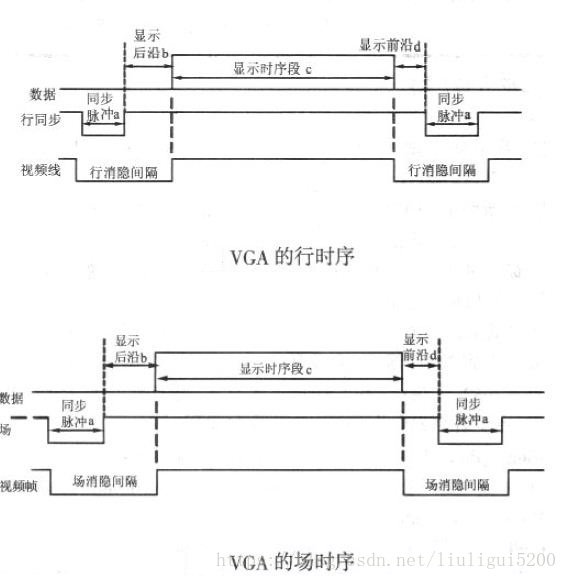

VESA中定义行时序和场时序都需要同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四部分。VGA工业标准显示模式要求:行同步,场同步都为负极性,即同步脉冲要求是负脉冲。

由VGA的行时序可知:每一行都有一个负极性行同步脉冲(Sync a),是数据行的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿(Back porch b),在显示时序段(Display interval c)显示器为亮的过程,RGB数据驱动一行上的每一个像素点,从而显示一行。在一行的最后为显示前沿(Front porch d)。在显示时间段(Display interval c)之外没有图像投射到屏幕是插入消隐信号。同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)都是在行消隐间隔内(Horizontal Blanking Interval),当消隐有效时,RGB信号无效,屏幕不显示数据。

VGA的场时序与行时序基本一样,每一帧的负极性脉冲(Sync a)是一帧的结束标志,同时也是下一帧的开始标志。而显示数据是一帧的所有行数据。

转自:https://blog.csdn.net/liuligui5200/article/details/80974319

【转】 VGA时序及其原理的更多相关文章

- 【转载】VGA时序与原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- VGA时序及其原理(转载)

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- 图像处理算法的仿真平台之VGA时序

一 概述 图像处理算法一般是用matla或OpenCV实现的,若是用FPGA实现,设计思路差别极大.matlab和opencv的优势:这些工具的优势在于可以方便地载入图像文件,或输出数据到图像文件, ...

- VGA 时序标准

VGA 显示器扫描方式从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行同步:当扫描完所有的行 ...

- FPGA VGA时序的理解

最近在做FPGA毕业设计,毕业设计规划的是摄像头采集图像,经过均值滤波,中值滤波,高斯滤波,然后通过VGA接口控制显示器显示出来,所以最近学习了一下FPGA的VGA驱动的相关内容. VGA接口 如上图 ...

- VGA设计(原理说明。Verilog代码实现,仿真结果)

各类显示屏的显示原理大部分是利用人眼的视觉暂留效应.比如之前的数码管显示就是设计每个周期内各个小段按顺序显示,来达到显示一个数字的效果. VGA同理,显示屏在显示时是一个像素一个像素地显示,在人眼看来 ...

- FPGA驱动VGA显示静态图片

一 .前言 本文设计思想采用明德扬至简设计法.VGA是最常见的视频显示接口,时序也较为简单.本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采 ...

- 【接口时序】7、VGA接口原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- VGA原理

VGA原理 1.VGA时序 2.不同的显示标准,有不同的水平段和垂直段 3.像素时钟和帧频的关系 联系目前调试的1080i 50Hz: 像素时钟为148.5MHz, 水平段周期 = 2640 X (1 ...

随机推荐

- Codeforces 1136 - A/B/C/D/E - (Done)

链接:https://codeforces.com/contest/1136/ A - Nastya Is Reading a Book - [二分] #include<bits/stdc++. ...

- Python2与python3 文件操作关于打开文件

#首先在python3中操作文件只有一种选择,那就是open() #而在python2中则有两种方式:file()与open() 两者都能够打开文件,对文件进行操作,也具有相似的用法和参数,但是,这两 ...

- Java之事务的基本应用

基本介绍 事务是数据一致性最基本的保证,也就是说一个事务中的操作要么都成功,要么都失败,不允许部分成功.我们常说的事务就是jdbc事务,当然Java中还有其他事务,并且在使用jdbc事务有很多注意点, ...

- ffmpeg的编译和安装

1. 先到ffmpeg官网上下载ffmpeg源码,然后配置.编译 http://ffmpeg.org/download.html 可以如下进行配置: ./configure --prefix=/usr ...

- 11.1-uC/OS-III就绪列表

准备好运行的任务被放到就绪列表中, 如图6-1.就绪列表是一个数组( OSRdyList[]),它一共有OS_CFG_PRIO_MAX条记录,记录的数据类型为OS_RDY_LIST(见OS.H).就绪 ...

- eclipse 安装 lombok插件

下载插件 官网下载 :https://projectlombok.org/ 有些小伙伴官网可能打不开,现提供我的下载地址:https://files.cnblogs.com/files/niceyoo ...

- ORACLE中关于使用between在MyBatis中取不同的区间值和取反

最近在项目中使用between取不同的区间值问题,由于区间跨度大,而且区间多,又是前端传过来的参数,所以使用in和exists比较麻烦.然后就考虑使用between.现将使用方法记录一下. 假如表有个 ...

- Spark Streaming之窗口函数和状态转换函数

流处理主要有3种应用场景:无状态操作.window操作.状态操作. reduceByKeyAndWindow import kafka.serializer.StringDecoder import ...

- Linux下安装jieba

Jieba代码对 Python 2/3 均兼容 * 全自动安装:`easy_install jieba` 或者 `pip install jieba` / `pip3 install jieba` * ...

- JDBC-DAO层数据访问工具类的实现

private static PreparedStatement pst; private static ResultSet rst; public static <T> int inse ...