自定义AXI总线IP之补全寄存器的输入输出配置

自定义AXI总线IP之补全寄存器配置输入和输出

1、实验目的

在使用默认的AXI4的配置时,不会有寄存器的配置,无法配置端口的输入还是输出。根据前面的AXI总线的理解,这里通过仲裁器判断,将AXI4的从地址0x04对应的寄存器用于端口的配置。通过寄存器的读取后直接输出到顶层。也可以直接将端口的数据加载到从机发射。

2、实验操作

(1)创建自定义IP

tools中的第一个就是新建一个IP核,设置就不多叙述。

(2)将slv_reg1de1数据加入判断序列

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

slv_reg0 <= 0;

slv_reg1 <= 0;

slv_reg2 <= 0;

slv_reg3 <= 0;

end

else begin

if (slv_reg_wren && slv_reg1==16'h0000)

begin

case ( axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )

2'h0:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 0

slv_reg0[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

2'h1:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 1

slv_reg1[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

2'h2:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 2

slv_reg2[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

2'h3:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 3

slv_reg3[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

default : begin

slv_reg0 <= slv_reg0;

slv_reg1 <= slv_reg1;

slv_reg2 <= slv_reg2;

slv_reg3 <= slv_reg3;

end

endcase

end

end

end

将这个判断加入到slv_reg0的接收模块。(这个判断不加的话可能存在为主机输入信号时可以向从机写入数据)

assign slv_reg_rden = axi_arready & S_AXI_ARVALID & ~axi_rvalid;

always @(*)

begin

// Address decoding for reading registers

case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] &&slv_reg1==16'hffff )

2'h0 : reg_data_out <= (slv_reg1==16'hffff)? SWS_VALID: slv_reg0;

2'h1 : reg_data_out <= slv_reg1;

2'h2 : reg_data_out <= slv_reg2;

2'h3 : reg_data_out <= slv_reg3;

default : reg_data_out <= 0;

endcase

end

这个是从机发送数据时的数据加载。利用这个判断可以将SWS的信号传到主机。

// Add user logic here

assign LED_VALID=(slv_reg1==16'h0000)? slv_reg0 : 1'b0;

// User logic ends

这个是将缓存器中的数据读取出来。

3、方案缺陷

这个三行修改的代码实现的功能,还是有许多的缺陷的。相对于专用的GPIO的设计,这个设计用两个端口分别读取输入输出,不能合并使用。优点就是可以适应输入输出的转化而不需要顾及端口不足的问题。还有一些其他细节的数据清零问题。由于是开始学习,就不过多的考虑其他因素。

4、验证操作

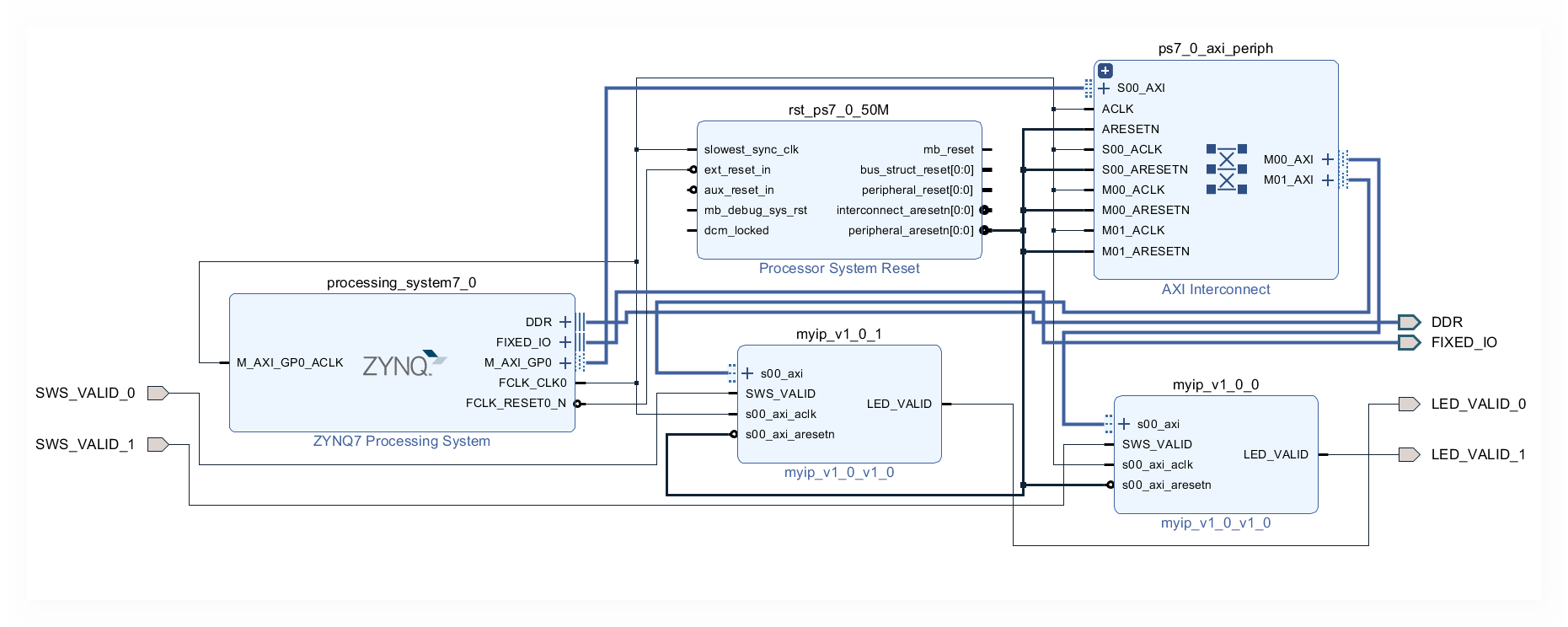

就是使用bd视图调用原理图就可以构建软件平台。软件通过寄存器的读取,即可测试输入输出信号是否有效。

这是初步的连接的原理图,后面的验证工作就是基于这个平台来支持读取和写入的切换的。这里根据开发板设置具体参数即可。

5、软件测试

这里的综合时间比较长,后面一篇续篇再做这个部分。

//补全

根据后面的实验验证,这个设计可能存在问题,也有可能是设置问题,最后的仿真结果并不如意。看来思路还是有问题,还是需要实际的修改。可以尝试一步一步来。

6、总结

这次的实验采取简单的仲裁逻辑判断输入输出,利用简单逻辑叠加和三目选择运算符实现一位宽数据的输入输出切换。官方IP核切换通过开发软件设置完成。个人自制的一般需要是确认为输入输出信号,这个设置其实只是为了熟悉AXI中各个信号的作用,实际作用并不大。

自定义AXI总线IP之补全寄存器的输入输出配置的更多相关文章

- ZYNQ自定义AXI总线IP应用——PWM实现呼吸灯效果

一.前言 在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能.要想使自定义IP核被CPU访问,就必须带有总线接口.ZYNQ采用AXI BUS实现PS和PL之间 ...

- 给 zsh 自定义命令添加参数自动补全

有时我会自定义一些 zsh 命令,以便提升某些高频操作的效率.本文记录我给一个自定义命令添加参数自动补全的方法. 场景 我自定义了一个 zsh 命令 gmt,执行 gmt <b2>,可以将 ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- Vim自动补全神器YouCompleteMe的配置

简介:YouCompleteMe号称Vim的自动补全神器,该项目在github的地址:YouCompleteMe:以下在10.0.1 build-1379776平台配置完成 插件安装操作: 1.确保V ...

- Linux --- vim 安装、支持python3的配置、插件自动补全YCM的安装配置及全过程错误总结

1.git(用来下载vim和相关插件) sudo apt-get install git 2,cmake(用来编译clang-llvm) sudo apt-get install build-esse ...

- vscode中html和vue没有自动补全,需要怎么配置

先安装HTML Snippets插件 点击 文件-首选项-设置,然后根据以下操作 然后在setting.json中加入以下代码 然后就有提示了

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

- vim代码补全-spf13,YouCompleteMe

vim代码补全 现在的图形界面的IDE(Integrated Development Environment)一般具有语法高亮,语法检查,自动补全功能,大大提高了编程的效率. vim作为文本编辑器其强 ...

- Vim自动补全神器:YouCompleteMe

第一次听说这个插件还是在偶然的情况下看到别人的博客,听说了这个插件的大名.本来打算在实训期间来完成安装的,无奈网实在不给力,也就拖到了回家的时候.在开始准备工作的时候就了解到这个插件不是很容易安装,安 ...

- EditPlus自动补全、模板配置

EditPlus真的是一款非常好用的编辑器,虽然小,但是短小精悍,速度快.只要配置好了,功能也是很强大的.下面来总结一下如何配置EditPlus的自动补全,和模板配置. 一.配置自动补全:(以开发CS ...

随机推荐

- STM32F407VET6 / BLACK_F407VE开发板间隔0.5秒不断重启

有一块 STM32F407VET6 的故障开发板, 之前的问题是经常无法烧录, 必须reset之后才能连接, 具体查看这篇 STM32F407VET6烧录出现flash download failed ...

- 惠普CP1025后盖传感器松导致不停自检或打印中掉电, 跳闪三角灯

上次修了离合器, 没出两星期又出问题了. CP1025这个型号就是出名的开机特别慢, 正常自检是1分钟, 但是前天我在给机器换完粉盒后, 自检似乎进入了死循环, 一直在自检. 周末才有空看看能不能解决 ...

- 【Unity3D】UGUI之Toggle

1 Toggle属性面板 在 Hierarchy 窗口右键,选择 UI 列表里的 Toggle 控件,即可创建 Toggle 控件,选中创建的 Toggle 控件,按键盘[T]键,可以调整 Tog ...

- Qt+ECharts开发笔记(一):ECharts介绍、下载和Qt调用ECharts基础柱状图Demo

前言 使用Qt开发大数据可视化看板,基于Qt使用QWidget或者QML是很难达到ECharts大数据看板的效果,所以使用Qt来制作. 核心思想 每一个ECharts图表使用一个无边框的Q ...

- Redis缓存应用场景

记录一下自己的听课笔记,看的网课. 参考资料:https://zhuanlan.zhihu.com/p/157717158 常见应用场景 1 数据缓存 缓存一些常用的.经常访问的.不经常变化的数据,也 ...

- 04、Etcd中常见的概念

本篇内容主要来源于自己学习的视频,如有侵权,请联系删除,谢谢. 上一章节,我们学习了 Etcdctl 的使用,从中窥探了 Etcd 的强大之处.从这一节开始,后面的内容基本上都是偏理论的东西,争取在看 ...

- 在Ubuntu搭建DHCP服务器

一.提供DHCP的服务器,自己必须有固定的IP地址 不然局域网就乱了,服务器自身启动(比如搭建完DHCP服务后,重新启动了服务器)的时候,DHCP服务器没有IP地址,无法和自己的DHCP服务通信. 在 ...

- CentOS6.8下yum安装Nginx

在/etc/yum.repos.d/目录下创建一个源配置文件nginx.repo: cd /etc/yum.repos.d/ vim nginx.repo 填写如下内容: [nginx] name=n ...

- 【Azure Redis】Redis客户端出现15分钟的超时异常

问题描述 客户端使用 Lettuce.io 连接 Azure Redis,出现了长达15分钟的Timeout异常. 问题解答 Azure Redis作为PaaS服务,由于一些平台的升级操作而引发的故障 ...

- 【Azure 应用服务】在Azure上部署一套VUE框架的单页面应用,有什么可以参考的文档呢?

问题描述 在Azure上部署一套VUE框架的单页面应用,有什么可以参考的文档呢? 问题回答 Azure官方上并没有VUE框架的实例代码,但是可以参考Node JS项目,来进行设置. 在 Azure 中 ...